- •1.Поняття архітектури еом

- •Характеристики еом.

- •3.Модульна структура еом

- •4.Матричні обчислювальні системи

- •Асоціативні обчислювальні системи

- •Принципи векторної обробки

- •Ммх технологія

- •5.Чипсет. Сучасні чипсети та їх характеристики.

- •6.Способи адресації

- •7.Режими роботи процесора.

- •8.Регістри відладки та тестуваня

- •10.Методи підвищення бистродії алп

- •13.Ієрархічна структура пам’яті.

- •14.Стекова пам’ять

- •15.Пристрої оперативної пам’яті.

- •Simm-модулі.

- •Simm edo ram (Extended Data Out) (5-2-х-х) мають тільки 72 піна і можуть працювати на частоті до 50 Мгц.

- •16.Флеш-пам’ять.

- •Розподіл секторів.

- •19.Фізична структура оптичних дисків

- •20.Організація переходу до перериваючої програми та пріоритетне обслуговування запитів переривання

- •21.Інтерфейси введення-виведення. Класифікація інтерфейсів

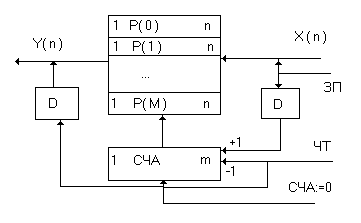

14.Стекова пам’ять

Стековая пам'ять, що. реалізуює безадресне завдання операндів, є ефективним елементом архітектури ЕОМ. Стек - це група послідовно пронумерованих регістрів (апаратний стек) або комірок пам'яті, що мають вказівник стека (звичайно регістр), у якому автоматично при запису та зчитуванні встановлюється номер (адреса) першого вільного осередку стека (вершина стека). При операції запису слово, що заносить у стек, заноситься у вільний осередок стека, а при зчитуванні зі стека витягається останнє слово, що надійшло в нього. Таким чином, у стеці реалізується принцип LIFO «останній прийшов - перший пішов».

Мал. 3.4. Стековая пам'ять.

Передбачається, що область пам'яті для стека знаходиться в сегменті стека, база якого визначається регістром SS - сегментним регістром стека. При додаванні запису в стек спочатку перевіряється, чи містить вказівник стека (ESP) значення, не менше довжини запису, що поміщає в стек, (2 байти для 16-розрядного й 4 байти для 32-розрядного процесора). Якщо ця умова не задоволена, то генерується особливий випадок порушення стека. Якщо ж ESP містить значення не менше необхідного, виконується декремент вказівника стека на 2(4) і операнд зберігається за адресою SS:SP (SS:ESP) у поточному сегменті стека, на який указує показник стека. (Число 4 - число байт в 32-х розрядному процесорі).

При зчитувані даних зі стека вміст ESP порівнюється з межею SS. Якщо звернення виявляється поза межею, формується особливий випадок порушення стека. Коли звернення виявляється дозволеним, зчитуються дані за адресою SS:[ESP] і здійснюється інкремент ESP на 4. Прочитати дані зі стека можна в регістр або в коміпку пам’яті.

У сучасних архітектурах процесорів стек й стекова адресація широко використовується при організації переходів до підпрограм і повернення з них, а також у системах переривання.

Останнім часом ємкість мікросхем динамічної пам'яті збільшувалась в четверо кожні три роки. Але швидкість цих мікросхем за той же період зростала набагато меншими темпами (приблизно 7% у рік). У той час, як продуктивність процесорів, починаючи з 1987р, збільшувалася на 50% у рік.

Таким чином, узгодження продуктивності сучасних процесорів зі швидкістю ОП обчислювальних машин і систем залишається однієї з найважливіших проблем. Методи підвищення продуктивності за рахунок збільшення розмірів Кеш-пам'яті й введення багаторівневої організації КЕШ можуть виявитися недостатньо ефективними з погляду вартості системи. Тому важливим напрямком сучасних розробок є методи підвищення пропускної здатності пам'яті за рахунок її організації, включаючи спеціальні методи організації динамічних ЗУ.

15.Пристрої оперативної пам’яті.

Запис типу 6-3-x-x називається формулою пам'яті і розшифровується наступним чином:

відкриття і доступ до першої комірки сторінки виконується за 6 тактів,

доступ до решти комірок відкритої сторінки – за 3 тактів.

Розглянемо основні типи корпусів динамічної пам’яті:

Спочатку мікросхеми динамічного ОЗУ випускалися в DIP-корпусах. Потім їх змінили модулі, що складаються з декількох мікросхем: SIPP, SIMM і, нарешті, DIMM і RIMM. Розглянемо ці різновиди детальніше.

DIP

DIP- корпус — це історично найстародавніша реалізація DRAM. DIP-корпус відповідає стандарту IC.

Мікросхеми (по-іншому, чипи) динамічного ОЗП встановлюються так званими банками. Банки бувають на 64, 256 Кбайт, 1 і 4 Мбайт. Кожний банк складається з дев'яти окремих однакових чипів. З них вісім чипів призначено для зберігання інформації, а дев'ятий чип служить для перевірки парності решти восьми мікросхем цього банку.

Чипи пам'яті бувають одно і чотирьох розрядними, і мають ємкість 64 Кбіт, 256 Кбіт, 1 і 4 Мбіт.

SIPP

Ці модулі є маленькою платою з декількома напаяними мікросхемами DRAM.

SIPP-модулі з'єднуються з системною платою за допомогою контактних штирків. Під контактною колодкою знаходяться 30 маленьких штирків, які вставляються у відповідну панель системної плати.

Модулі SIPP мали певні вирізи, які не дозволяли вставити їх в роз'єми неправильним чином.