- •2. Этапы развития вычислительной техники

- •3. Поколения эвм.

- •4. Принципы фон Неймана

- •Как работает машина фон Неймана

- •5. Мпс (шины, осн. Составляющие).

- •6. Два типа архитектуры (принстонская и гарвардская).

- •7. Карты Карно. Минимизация с их помощью.

- •8 .Дешифраторы: назначение, классификация. Принципы действия. Уго. Синтез линейного дешифратора.

- •9.Многоступенчатые дешифраторы: прямоугольные, пирамидальные.

- •10.Шифратор . Определение. Описание закона функционирования. Схема реализации уго.

- •11. Мультиплексоры: назначение, определение, уго, Структурная схема.

- •12. Мультиплексное дерево.

- •13.Демультиплексоры: принципы действия , уго.

- •Уго демультиплексора «1 в 4».

- •14.Сумматоры: классификация, назначение. Классификация

- •15.Одноразрядный комбинационный полусумматор.

- •1 6.Одноразрядный комбинационный полный сумматор.

8 .Дешифраторы: назначение, классификация. Принципы действия. Уго. Синтез линейного дешифратора.

Основное назначение дешифратора состоит в том, чтобы выбрать (адресовать, инициализировать) один объект из множества находящихся в устройстве. Рис. 3.5 иллюстрирует это применение. Каждому объекту присваивают определенный адрес (номер). Когда на входы дешифратора поступает двоичный код адреса, соответствующий элемент активизируется за счет появления логического 0 на связанном с ним выходе де-шифратора, а остальные элементы остаются заблокированными. Можно предусмотреть, чтобы с одного из выходов дешифратора на определенный блок поступал управляющий сигнал, когда на входах дешифратора появляется определенный код, соответствующий, например, превышению какого-либо параметра (температуры, напряжения и т.д.), который должен быть приведен к нормальному уровню указанным блоком.

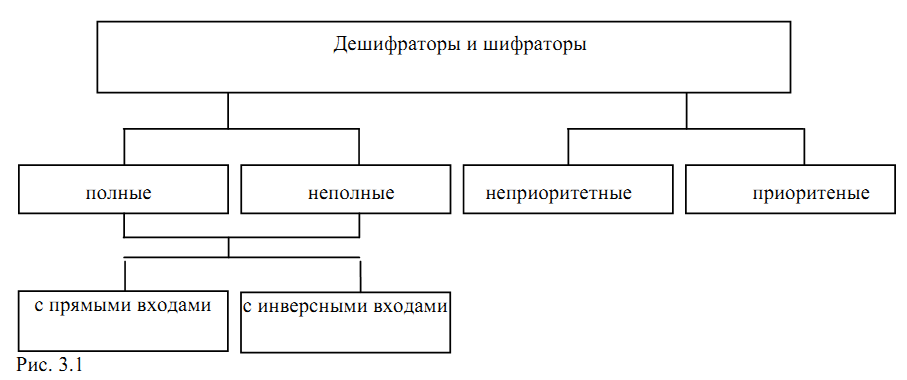

Классификация.

Дешифраторы могут быть полными и неполными. Полные дешифраторы реагируют на все входные коды, неполные – на коды,

величина которых не превосходит некоторого заранее установленного значения. Выходы дешифраторов могут быть прямыми и инверсными.

Шифраторы выпускаются приоритетными и не приоритетными. У приоритетного шифратора входы имеют разный приоритет.

Возбужденный вход с большим приоритетом подавляет действие прежде возбужденного и устанавливает на выходах код, соответствующий своему значению.

Принцип действия.

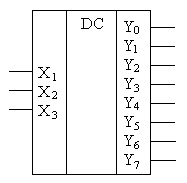

Ф ункция

дешифратора понятна из названия.

Дешифратор преобразует входной двоичный

код в управляющий сигнал только на

одном из своих выходов. В общем случае

дешифратор имеет n однофазных входов

и 2 в степени n выходов, где n - разрядность

дешифрируемого кода. Микросхемы

дешифраторов обозначаются на схемах

буквами DC (от английского слова

Decoder). Активным

всегда является только один выход

дешифратора, причем номер этого выхода

и соответствующего ему сигнала однозначно

определяется входным кодом.

То

есть при сигнале на входе дешифратора

00 мы получаем 1 на нулевом выходе, при

сигнале на входе 01 получаем 1 на первом

выходе, при сигнале на входе 10 - 1 на

втором выходе и так далее.

В

стандартные серии входят дешифраторы

на 4, 8 и 16 выходов, что соответствует 2,

3 и 4 разрядам входного кода.

Входы,

на которые поступает входной код, часто

называют адресными входами. Их обозначают

1, 2, 4, 8, где число соответствует весу

двоичного кода. Код на входах 1, 2, 4, 8

определяет номер активного выхода.

Входы

С1, С2, С3 - это входы разрешения, объединенные

по функции "И". С помощью сигнала

на этих входах определяется момент

срабатывания дешифратора. Входы

разрешения могут также использоваться

для наращивания разрядности входного

кода.

Выходные

сигналы дешифраторов и входы разрешения,

часто имеют отрицательную полярность,

то есть их активное состояние отображается

значением логического 0, а не логической

1.

Если

нужно дешифровать код с большим числом

разрядов, используют объединение

нескольких микросхем дешифраторов.

Еще

одно распространенное применение

дешифраторов - селекция заданных входных

кодов. Появление сигнала на выбранном

выходе дешифратора будет означать

поступление на вход интересующего нас

кода. В данном случае увеличивать число

разрядов входного силикатируемого

кода становится гораздо проще.

В

отечественных сериях микросхемы

дешифраторов обозначаются буквами ИД

ункция

дешифратора понятна из названия.

Дешифратор преобразует входной двоичный

код в управляющий сигнал только на

одном из своих выходов. В общем случае

дешифратор имеет n однофазных входов

и 2 в степени n выходов, где n - разрядность

дешифрируемого кода. Микросхемы

дешифраторов обозначаются на схемах

буквами DC (от английского слова

Decoder). Активным

всегда является только один выход

дешифратора, причем номер этого выхода

и соответствующего ему сигнала однозначно

определяется входным кодом.

То

есть при сигнале на входе дешифратора

00 мы получаем 1 на нулевом выходе, при

сигнале на входе 01 получаем 1 на первом

выходе, при сигнале на входе 10 - 1 на

втором выходе и так далее.

В

стандартные серии входят дешифраторы

на 4, 8 и 16 выходов, что соответствует 2,

3 и 4 разрядам входного кода.

Входы,

на которые поступает входной код, часто

называют адресными входами. Их обозначают

1, 2, 4, 8, где число соответствует весу

двоичного кода. Код на входах 1, 2, 4, 8

определяет номер активного выхода.

Входы

С1, С2, С3 - это входы разрешения, объединенные

по функции "И". С помощью сигнала

на этих входах определяется момент

срабатывания дешифратора. Входы

разрешения могут также использоваться

для наращивания разрядности входного

кода.

Выходные

сигналы дешифраторов и входы разрешения,

часто имеют отрицательную полярность,

то есть их активное состояние отображается

значением логического 0, а не логической

1.

Если

нужно дешифровать код с большим числом

разрядов, используют объединение

нескольких микросхем дешифраторов.

Еще

одно распространенное применение

дешифраторов - селекция заданных входных

кодов. Появление сигнала на выбранном

выходе дешифратора будет означать

поступление на вход интересующего нас

кода. В данном случае увеличивать число

разрядов входного силикатируемого

кода становится гораздо проще.

В

отечественных сериях микросхемы

дешифраторов обозначаются буквами ИД

УГО трехразрядного дешифратора.

Синтез Линейного Дешифратора 3->8.

Х3 Х2 Х1 |

Z0 Z1 Z2 Z3 Z4 Z5 Z6 Z7 |

0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 |

1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1

|

Таблица состояний дешифратора

Как следует из таблицы состояния, каждой функции соответствует только один минтерм, следовательно, не требуется минимизировать эти функции. Из полученных уравнений и схемы дешифратора следует, что для реализации полного дешифратора на m входов (переменных) потребуются n = 2m элементов конъюнкции (количество входов каждого элемента “И” равно m)и m элементов отрицания.