- •Структура и принцип действия микропроцессора классической архитектуры

- •2. Выполнение процессором командного цикла.

- •Машинный и командный цикл cisc микропроцессора

- •4. Структура команд. Способы адресации. Длинное командное слово

- •5 . Организация подпрограмм и использование стековой области памяти.

- •6.Аппаратные средства интрфейса.

- •7.Програмные средства интерфейса для управления электроприводами

- •8. Параллельный и последовательный интерфейс. Области применения

- •9. Принцип действия программируемого таймера.

- •10. Ввод и вывод информации с применением программируемого контроллера прерываний.

- •11.Работа вычислительного устройства в режиме прямого доступа к памяти.

- •12. Программная реализация интервалов времени.

- •13 Аппаратная реализация интервалов времени

- •14. Микросхемы памяти, их основные характеристики и классификация

- •15. Функциональная схема устройства оперативной памяти

- •16. Постоянные запоминающие устройства, их типы и области применения.

- •17. Применение пзу в качестве функционального преобразователя (фп).

- •18.Цифро-аналоговое преобразование.

- •19.Аналого-цифровое преобразование.

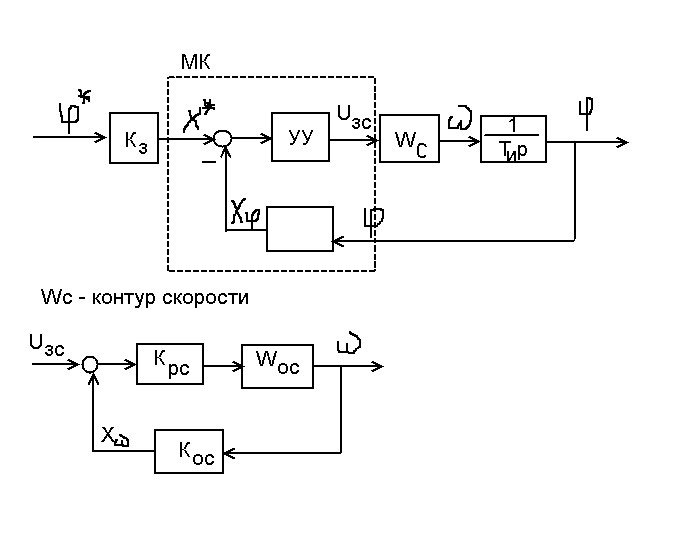

- •23. Микроконтроллер, его функциональная схема и применение в системе управления электроприводом

- •24. Влияние времени выполнения программы микроконтроллером на запас устойчивости замкнутой системы.

- •25. Микроконтроллер как динамическое звено.

- •26. Выбор числа разрядов слова данных по требуемой точности системы управления.

- •27. Рекурсивные и нерекурсивные цифровые фильтры, их передаточные функции и структурные схемы. Алгоритм и программа цифрового фильтра.

- •28. Цифровое дифференцирование и интегрирование.

- •31. Паралельная обработка информации. Классификация вычислительных систем с параллельной обработкой информации.

- •32. Процессоры с сокращенным набором команд (risc) и с полным набором команд (cisc). Примеры.

- •33. Гарвардская и разнесенная архитектуры микропроцессоров. Примеры.

- •35. Гарвардская архитектура восьмиразрядных микроконтроллеров pic.

- •36. Функциональная схема микроконтроллера msp430 и назначение входящих в него устройств.

- •37. Функциональная схема микроконтроллера pic16 и назначение входящих в него устройств.

- •38. Система команд микроконтроллера msp430. Пример составления программы.

- •39 .Система команд микроконтроллеров архитектуры adsp-bf. Пример составления программы

- •40Режимы энергопотребления микроконтроллеров.Примеры

- •41 Архитектура risc – ядра arm7 16/32 разрядных микроконтроллеров.

- •42. Система команд микроконтроллеров arm7. Пример составления программы.

- •43. Способы повышения эффективности использования конвейера.

- •45. Структура ядра adsp-bf и его регистры.

- •46. Алгоритм расчета сигнала управления в замкнутой системе.

- •47. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием устройства захвата сравнения.

- •48. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием таймера счетчика

- •49. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала времени.

- •50. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала перемещения.

- •51. Применение программируемого таймера в системах управления эп.

- •52. Применение программируемого таймера в системах управления эп.

- •53. Использование нечеткой логики для синтеза управления. Лингвист. Переменные.

- •54 Алгоритм нечеткого управления

- •55. Структура и принцип действия искусственного нейрона. Соединение в сеть

- •56. Применение искусственной нейронной сети в качестве устройства управления.

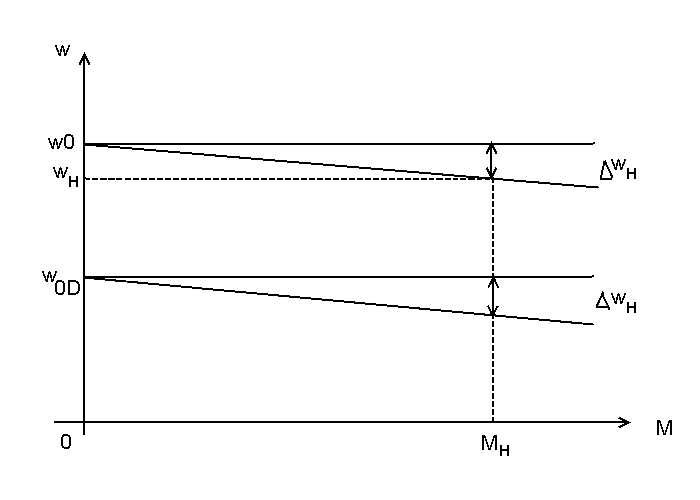

26. Выбор числа разрядов слова данных по требуемой точности системы управления.

1) Система управления положением:

2) Система управления скоростью:

Для таких систем обычно задаются

Т ребуемое

количество разрядов контроллера при

интерполяции определяется на основании

формулы:

ребуемое

количество разрядов контроллера при

интерполяции определяется на основании

формулы:

,

(1)

,

(1)

где K – количество разрядов контроллера.

Таким образом, для нахождения разрядности микроконтроллера, необходимо решить неравенство:

.

(2)

.

(2)

Таким образом, исходя из заданной точности, для реализации программы управления необходимо к разрядов.

27. Рекурсивные и нерекурсивные цифровые фильтры, их передаточные функции и структурные схемы. Алгоритм и программа цифрового фильтра.

Цифр. Фильтр называется рекурсивным, если сигнал на его выходе зависит от знач. Вых. Сигнала на предыдущих шагах.

По последнему выражению составим структурную схему:

Цифр. Фильтр допускает аппаратную программную реализацию. Аппаратная реализация выполняется на основании структурной схемы. Для аппаратной реализации применяются процессорные матрицы. Каждый процессор выполняет 1-ну или несколько операций.

Для программной реализации цифрового фильтра используется переход от z-изображения к оригиналу.

Необходимые

параметры

,

а также начальные условия:

,

а также начальные условия: .

При переходе к след. Шагу расчета должны

возрастать, т. есть в памяти необходимо

хранить вход. и выход. величины на 2-х

пропущенных шагах.

.

При переходе к след. Шагу расчета должны

возрастать, т. есть в памяти необходимо

хранить вход. и выход. величины на 2-х

пропущенных шагах.

Перейдем к рекурсии:

Нерекурсивный фильтр

Структура фильтра имеет след вид:

КИХ и БИХ

Импульсная хар-ка (ИХ) - реакция на ед. импульс:

Такая (ИХ) является конечной (КИХ). Рекурсивные фильтры обычно имеют бесконечную имп. характеристику.

28. Цифровое дифференцирование и интегрирование.

Непрерывный интегратор имеет передаточную функцию:

Цифровое дифференцирование

Если на вход подать последовательность импульсов, то на выходе будет 1 импульс

29.Способы повышения производительности микропроцессора. Конвейерное выполнение команд. Пример микроконтроллера с конвейерным выполнением команд.

Совершенствование архитектуры дает повышение производительности без повышения тактовой частоты. Усовершенствование архитектуры, увеличивает коэффициент использования.

1980г.-организация памяти, расслоение памяти (КЭШ).

1990г.-процессоры с длинным командным словом, конвейеры(LIW).

2000г.-многоядерные процессоры.

Все это распараллеливает обработку информации.

Параллелизм:

Векторный - на уровне программ крупнозернистый.

Скалярный - на уровне команды мелкозернистый.

1)

2) 1-на команда много данных.

3)Много

команд, одни данные.

3)Много

команд, одни данные.

Скалярный параллелизм. За счет усовершенствования аппаратных средств. Конвейерное выполнение помогает расслоению памяти. Применение КЭШ-памяти.

Позволяет сократить суммарное выполнение команды.

Недостаток – при конвейерной организации закрывается ветвление, затрудняется прерывание.

Процессор называется суперконвейерным если он содержит конвейер вложенностью не менее 5-ти ступеней.

Суперскалярный процессор кода имеет более 5-ти работающих параллельно конвейеров. Позволяет за 1-н такт выполнить несколько команд.

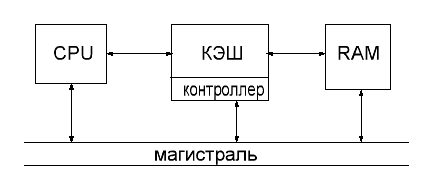

30. КЭШ-память, ее назначение и принцип действия

КЭШ – дополнительная высокоскоростная память, в которой дублируется часть активного пространства основной памяти. При таком решении при обращении к памяти вначале анализируется КЭШ; если нужная информация в нем отсутствует, то происходит обращение к основной памяти. Она предназначена для временного хранения данных и команд. КЭШ память не занимает адресного пространства.

Контроллер КЭШ «памяти» работает по алгоритму позволяющее учесть обновление данных. Высокое быстродействие КЭШ обусловлено выполнением его на статических элементах памяти (триггеры). Возможны несколько уровней КЭШ памяти.