- •Структура и принцип действия микропроцессора классической архитектуры

- •2. Выполнение процессором командного цикла.

- •Машинный и командный цикл cisc микропроцессора

- •4. Структура команд. Способы адресации. Длинное командное слово

- •5 . Организация подпрограмм и использование стековой области памяти.

- •6.Аппаратные средства интрфейса.

- •7.Програмные средства интерфейса для управления электроприводами

- •8. Параллельный и последовательный интерфейс. Области применения

- •9. Принцип действия программируемого таймера.

- •10. Ввод и вывод информации с применением программируемого контроллера прерываний.

- •11.Работа вычислительного устройства в режиме прямого доступа к памяти.

- •12. Программная реализация интервалов времени.

- •13 Аппаратная реализация интервалов времени

- •14. Микросхемы памяти, их основные характеристики и классификация

- •15. Функциональная схема устройства оперативной памяти

- •16. Постоянные запоминающие устройства, их типы и области применения.

- •17. Применение пзу в качестве функционального преобразователя (фп).

- •18.Цифро-аналоговое преобразование.

- •19.Аналого-цифровое преобразование.

- •23. Микроконтроллер, его функциональная схема и применение в системе управления электроприводом

- •24. Влияние времени выполнения программы микроконтроллером на запас устойчивости замкнутой системы.

- •25. Микроконтроллер как динамическое звено.

- •26. Выбор числа разрядов слова данных по требуемой точности системы управления.

- •27. Рекурсивные и нерекурсивные цифровые фильтры, их передаточные функции и структурные схемы. Алгоритм и программа цифрового фильтра.

- •28. Цифровое дифференцирование и интегрирование.

- •31. Паралельная обработка информации. Классификация вычислительных систем с параллельной обработкой информации.

- •32. Процессоры с сокращенным набором команд (risc) и с полным набором команд (cisc). Примеры.

- •33. Гарвардская и разнесенная архитектуры микропроцессоров. Примеры.

- •35. Гарвардская архитектура восьмиразрядных микроконтроллеров pic.

- •36. Функциональная схема микроконтроллера msp430 и назначение входящих в него устройств.

- •37. Функциональная схема микроконтроллера pic16 и назначение входящих в него устройств.

- •38. Система команд микроконтроллера msp430. Пример составления программы.

- •39 .Система команд микроконтроллеров архитектуры adsp-bf. Пример составления программы

- •40Режимы энергопотребления микроконтроллеров.Примеры

- •41 Архитектура risc – ядра arm7 16/32 разрядных микроконтроллеров.

- •42. Система команд микроконтроллеров arm7. Пример составления программы.

- •43. Способы повышения эффективности использования конвейера.

- •45. Структура ядра adsp-bf и его регистры.

- •46. Алгоритм расчета сигнала управления в замкнутой системе.

- •47. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием устройства захвата сравнения.

- •48. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием таймера счетчика

- •49. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала времени.

- •50. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала перемещения.

- •51. Применение программируемого таймера в системах управления эп.

- •52. Применение программируемого таймера в системах управления эп.

- •53. Использование нечеткой логики для синтеза управления. Лингвист. Переменные.

- •54 Алгоритм нечеткого управления

- •55. Структура и принцип действия искусственного нейрона. Соединение в сеть

- •56. Применение искусственной нейронной сети в качестве устройства управления.

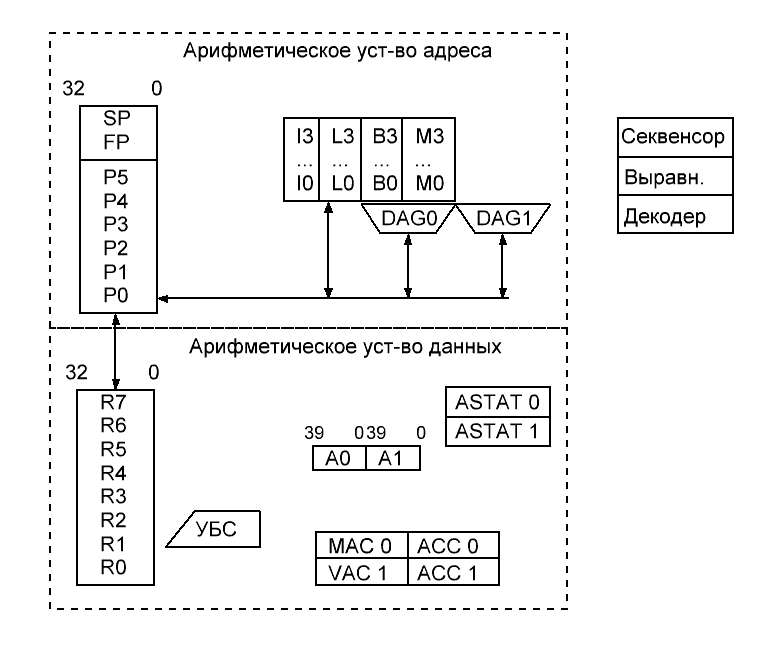

45. Структура ядра adsp-bf и его регистры.

Ядро ADSP-BFимеет разнесенную архитектуру (отдельные арифметические уст-ва для адресов и данных).

Секвенсор — аппаратное устройство, кот. выполняет переход, организацию циклов и использование подпрограмм. Он имеет свою систему команд.

Вычисление адреса необходимо для косвенной и индексной адресации.

Регистры - указателя на адрес (P0-P5)

FP – указатель границ

SP - указатель стека

DAG – генератор адреса данных

I0-I3 – регистры-индексы

M0-M3 – регистры-идентификаторы (адрес=I+M)

B0-B3 – указатели на базовые адреса

L0-L3 – длина величин

ASTAT – флаговый регистр

УБС – устр-во барабанного сдвига

А0,А1 – аккумуляторы

MAC 0, MAC 1 – аппаратные умножители

ACC 0, ACC 1 – ариф.-лог. уст-во (АЛУ)

Арифметическое уст-во данных обеспечивает выполнение длинного командного слова. Оно оперирует с данными 1, 2, и 4 байта. Данные должны располагаться в R0..R7 и P0..P5

46. Алгоритм расчета сигнала управления в замкнутой системе.

Разработка алгоритма расчета сигнала управления является важной частью проектирования системы с микропроцессорным управлением и выполняется одновременно с разработкой функциональной схемы системы управления.

Системы кправления ЭП по выполняемым функциям делят на 2 класса: системы логического управления и замкнутые системы управления. В случае программной реализации оба класса систем требуют цикличности работы программного обеспечения, поскольку лишь периодический опрос состояния внешних устройств и периодическое формирование сигналов управления обеспечивают работу системы в реальном времени.

При разработке функциональной схемы системы управления ЭП от МК необходимо вначале определить все функционально необходимые элементы системы, исходя из ее функционального назначения и требований.

Программа формирования управляющего сигнала должна быть циклической, причем каждый цикл должен предусматривать чтение информации с датчиков, расчет соответствующего значения сигнала управления и вывод этого сигнала для воздействия на объект управления. В то же время программа должна обеспечивать правильную начальную установку параметров регуляторов и начальные условия. Поэтому программа управления обычно составляется из двух частей: инициализационной и циклической. Инициализационная часть содержит операторы, которые определяют типы переменных и их начальные значение. Инициализационная часть выполняется один раз при начальном запуске системы. Циклическая часть должна предусматривать периодический ввод информации с периферийных устройств и формирование сигналов управления на основании этой информации, вывод значений сигналов управления для воздействия на объект. Циклическая часть повторяется периодически неограниченное количество раз во время функционирования системы и прекращает выполнение с отключением системы.

Содержание программного обеспечения циклической и инициализационной частей замкнутой системы определяется в зависимости от структуры и вида регуляторов, которые необходимо реализовать. Поэтому алгоритм формирования сигнала управления разрабатывается после решения задачи синтеза замкнутой системы. Задача синтеза замкнутой системы с цифровым управлением может быть решена одним из двух методов – точным либо приближенным. Точный метод прходится применять, когда интервал времени, в течение которого выполняется циклическая часть программы, сравним со временем переходного процесса с синтезированной системе. Тогда дискретные передаточные функции (ДПФ) регуляторов синтезируются на основании ДПФ объекта. Приближенные методы допустимы, если время переходного процесса синтезированной системы в 10 и более раз превышает время выполнения циклической части программы. Чем меньше время выполнения циклической части, тем меньше запаздывание в контуре регулирования, и тогда динамика цифровой системы приближается к динамике непрерывной системы.

При проектировании системы цифрового управления ЭП целесообразно вначале определить допустимое время выполнения циклической части на основании требуемого быстродействия. Это позволяет оценить ориентировочно пригодность конкретного типа МК для выполнения данной задачи управления. После этого, если время выполнения циклической части достаточно мало, можно применить метод синтеза непрерывной системы.

С целью дискретизации сигнала управления, следует перейти к z-преобразованию. Для этого можно использовать различные приближенные выражения, связывающие переменную z и переменную p преобразования Лапласа. На основании разложения в ряд: z=epT1+Тр+Т2р2/2! +Т3р3/3!+...1+Тр. Можно приближенно принять z1+Тр.