- •5.3 Усилительный каскад с общим эмиттером 43

- •1. Полупроводниковые приборы

- •Физические основы полупроводниковых приборов

- •Собственные и примесные полупроводники

- •1.3 Типы пробоев n – р – перехода

- •2. Полупроводниковые диоды

- •2.1 Классификация и маркировка

- •2.2 Выпрямительные диоды

- •2.3 Кремниевые диоды

- •2.3 Кремниевые диоды

- •2.4 Германиевые диоды

- •2.5 Арсеннид-галлиевые диоды.

- •2.6 Селеновые выпрямители

- •2.7 Импульсные диоды

- •2.8 Диоды Шотки

- •2.8.1 Выпрямительные диоды Шотки

- •2.9 Стабилитроны

- •2.10 Cтабисторы

- •2.11 Шумовые диоды

- •2.12 Туннельные диоды

- •2.13 Обращённые диоды

- •2.14 Варикапы

- •3. Транзисторы

- •3.1 Классификация и маркировка

- •3.2 Биполярные транзисторы

- •Схемы включения транзисторов

- •3.2.2 Схема с общим коллектором (эмиттерный повторитель)

- •3.2.3 Статические вах

- •3.2.4 Параметры транзистора в режиме малого сигнала

- •3.3 Полевые транзисторы

- •3.3.1 Полевые транзисторы с управляющим р – n переходом

- •3.3.2 Статические характеристики полевых транзисторов

- •3.3.3 Статические характеристики передачи

- •4. Тиристоры

- •4.1 Диодные тиристоры (динисторы)

- •4.2 Триодные тиристоры

- •5. Полупроводниковые устройства

- •5.1 Усилители

- •5.1.1 Усилительный каскад с общим эмиттером

- •5.1.2 Классы усиления

- •5.1.3 Способы задания рабочей точки покоя

- •5.1.4 Термостабилизация точки покоя

- •5.2 Схема с коллекторной термостабилизацией

- •5.2.1 Каскад с общим эмиттером при работе на переменном сигнале

- •5.2.2 Частотные искажения

- •5.2.3 Параметры усилительного каскада с общим эмиттером

- •5.3 Усилительный каскад с общим эмиттером

- •5.3.1 Временные диаграммы работы каскада с общим коллектором

- •5.3.2 Многокаскадное соединение усилителей

- •5.4 Усилитель мощности

- •5.4.1 Усилитель мощности в классе а, б

- •6. Генераторы

- •6.1 Генераторы с независимым возбуждением.

- •6.2 Генераторы с самовозбуждением (автогенераторы)

- •6.3 Генераторы синусоидальных колебаний

- •6.5 Стабилизация частоты автогенератора

- •6.6 Импульсные устройства, генераторы и формирователи импульсов

- •6.7 Виды и параметры импульсов:

- •6.7.1 Реальный импульс

- •6.7.2 Энергетические параметры импульсного сигала

- •6.8 Генераторы импульсов

- •7. Транзисторные ключи

- •7.1 Процессы переключения транзистора в ключе

- •7.1.1 Включение

- •7.2.2 Выключение

- •8. Импульсные устройства

- •8.1 Триггер

- •8.2 Мультивибратор

- •8.3 Одновибратор

- •9. Интегральные микросхемы

- •9.1 Общие положения (понятия)

- •10. Основы цифровой электроники

- •10.1 Первичные понятия алгебры Буля:

- •10.2 Оснoвные логические элементы

- •10.3 Основные тождества алгебры Буля

- •10.4 Представление логических элементов на основе базовых (на примере логического элемента «и – не»)

- •10.5 Схемотехника логических элементов

- •10.5.1 Элементы не в ттл – микросхемах

- •1 0.5.2. Реальная ячейка схемы ттл

- •10.5.3. Принцип работы элемента и-не.

- •1 0.5.4. Микросхемы с открытым коллектором.

- •10.5.5. Нагрузочная способность элемента ттл

- •10.6. Основы логических схем

- •10.6.1. Способы расчета логических схем

- •10.6.2. Комбинационные логические схемы

- •11 Цифровые микросхемы

- •11.1. Мультиплексор.-кп

- •11.2. Дешифраторы. –ид

- •11.2.1. Принцип действия

- •1 1.3. Шифраторы

- •11.4. Триггеры

- •11.4.1. Асинхронный rs триггер

- •11.4.2. Синхронный rs-триггер

- •11.4.6. Однотактный jk –триггер

- •11.4.7. Временные диаграммы работы

- •11.4.8. Двухтактные jk –триггеры или триггеры типа ms

- •11.5. Счетчики импульсов

- •11.5.1. Четырехразрядный асинхронный двоичный счётчик по модулю 16

- •1 1.5.2. Синхронный счётчик

- •11.5.3. Двоично-десятичный счётчик или счётчик по модулю десять

- •11.5.4. Вычитающие счётчики

- •1 1.5.5. Вычитающий счётчик с самоостановом

- •1 1.5.6. Реверсивный счётчик

- •11.6. Регистры

- •11.6.1. Параллельный регистр или регистр памяти

- •11.6.2 Регистр сдвига, кольцевой регистр

- •12 Арифметические устройства. Алу

- •12.1. Полусумматор

- •12.2. Полные сумматоры.

- •12.3 Параллельный сумматор многоразрядных чисел.

- •12.4. Вычитатели.

- •12.4.1. Использование сумматоров для вычитания

- •12.5. Суммирующее устройство последовательного действия или последовательный сумматор

- •12.6. Двоичное умножение

- •12.7. Сложение и вычитание чисел, представленных в дополнительном коде

- •12.7.1. Правила представления чисел в двоичном коде

- •1 2.8. Сумматор-вычитатель, работающий в дополнительном коде

- •13 Оперативные и постоянные запоминающие устройства.

- •1 3.2. Пример реализации элемента с тремя состояниями: 0, 1, z-состояния.

- •13.3. Постоянные запоминающие устройства пзу

- •13.4. Аналоговые интегральные микросхемы

- •14. Операционные усилители

- •14.1. Общие положения.

- •15. Принципы управления двигателем след. Св-ва п/п приб.

- •15.1 Режимы целесообразного управления по цепи якоря.

- •15.2 Широтно – импульсный преобразователь

- •18.2 Трехфазный управляемый выпрямитель

- •1 8.4. Однополюсный выпрямитель

- •18.5. Выпрямитель с нулевым выводом

- •1 8.3. Мостовой двухполупериодный выпрямитель

- •18.5.Фильтры

- •19.4 Пример системы вертикального управления

7. Транзисторные ключи

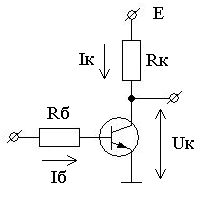

Транзисторные ключи являются основным элементом импульсных схем. Наиболее распространен ключ по схеме с общим эмиттером.

Рис.7.1. Принципиальная схема транзисторного ключа

Транзисторный ключ имеет три режима работы:

Режим отсечки: транзистор заперт (ключ разомкнут)

В этом случае заперты оба p – n перехода.

Uбэ < 0 Uбк < 0

IK = IKO IЭ << IK (IБ = IЭ – IК)

Iб ≈ - IКО

Рис.7.2. Динамические характеристики режима отсечки

На динамических характеристиках режим отсечки соответствует т. А.

Режим насыщения.

В этом случае открыты оба p – n перехода транзистор открыт (ключ замкнут)

Uбэ > 0 Uбк > 0

Напряжение на транзисторе UK ≈ 0. Это напряжение на открытых p – n переходах.

Rтр ≈ 0.

![]() -

максимально возможный ток через

транзистор.

-

максимально возможный ток через

транзистор.

На динамических характеристиках соответствует точке В транзистор переходит в режим насыщения при положительном приращении базового тока до значения, при котором изменение тока коллектора прекращается. Это соответствует переходу рабочей точки по линии нагрузки из точки А в точку В.

Определим ток базы насыщения, как минимальный ток, при которм ключ уже находится в состоянии насыщения.

![]() ,

где

,

где

β – коэффициент тока базы.

При расчете ключевых схем используют токовый критерий насыщения, т.е. выбирают Iб > Iбн и критерий отсечки по напряжению.

Динамический режим соответствует переходу из т. А в т. В и обратно.

Этот режим имеет конечную длительность. Транзистор в этом случае работает как линейный элемент и потребляет мощность на себя, снижая тем самым КПД импульсного устройства. Влияние этого режима, ослабляется с увеличением ключей.

7.1 Процессы переключения транзистора в ключе

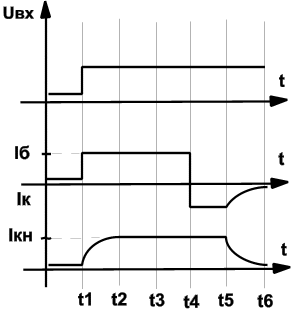

7.1.1 Включение

Пусть

в момент времени t,

подается отпирающее входное напряжение,

ток базы скачком устанавливается

![]() .

.

Рис.7.3. Динамические характеристики включения

Причем Rб выбрано таким образом, что Iб > Iбн.

![]() ,

где τтр

– постоянная времени транзистора,

определяемая емкостью n

– p транзистора

и характеризует инерционные свойства

транзистора. Под действием тока базы,

ток коллектора увеличивается и стремится

к β*Iб.

,

где τтр

– постоянная времени транзистора,

определяемая емкостью n

– p транзистора

и характеризует инерционные свойства

транзистора. Под действием тока базы,

ток коллектора увеличивается и стремится

к β*Iб.

Но на уровне тока насыщения увеличение тока прекращено, что соответствует моменту времени t2. Далее ток коллектора не изменяется , но в базе транзистора происходит накопление избыточных носителей заряда до времени t3.

Iб > Iбн

Динамическому режиму работы транзистора соответствует этап формирования фронта импульса [t1, t2]. Длительность фронта импульса можно найти из уравнения:

![]()

![]()

Из этой формулы видно, что длительность фронта уменьшается с увеличением тока базы.

7.2.2 Выключение

В момент t4 подан импульс запирающего напряжения.

На

этапе t4,

t5

происходит накопление заряда в базе

при этом IК

= IКН,

а ток базы определяется уравнением:

![]() .

.

На этапе t4, t6 происходит формирование импульса среза tср, находится аналогично. И уменьшается с увеличением отрицательного тока базы.

Соответственно из этих условий вытекает один из способов увеличения быстродействия ключей, он называется метод формирования оптимального тока базы.

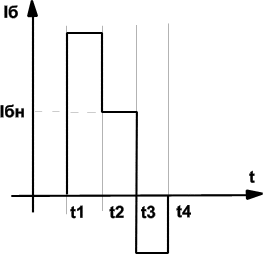

Оптимальная форма тока будет иметь следующий вид:

Рис.7.4. Оптимальная форма тока

t1, t2 - соответствует формированию тока импульса Iб >> Iбн

t2, t3 - задана длительностью импульса Iб ≈ Iбн

t3, t4 – этап формирования среза Iб << 0

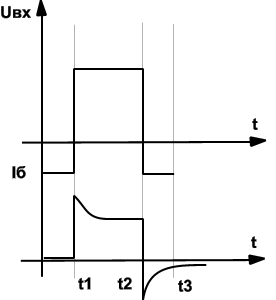

Практически эта диаграмма может быть реализована путем добавления форсирующего конденсатора в цепь базы.

Рис.7.5. Временная диаграмма схемы включения