- •Высокопроизводительные вычислительные системы

- •Лекция № 2 (1.03.12)

- •Лекция № 3 (15.03.12)

- •Лекция № 4 (22.03.12)

- •Лекция № 5 (29.03.12)

- •Лекция № 6 (.12) Классификация параллельных компьютеров и систем Классификация Флинна

- •Классификация Хокни

- •Классификация Фекта

- •Векторно – конвейерные компьютеры

- •Лекция № 7 (12.04.12)

- •Лекция № 8 (26.04.12)

- •Лекция № 9 (03.05.12)

- •Вычислительные системы с распределенной памятью.

- •Кластерные вс

- •Метакомпьютер

- •Лекция № 10 (10.05.12) Функционирование процессора. Исполнение команд.

- •Трассировка

- •Регистрация программных событий

- •Милликод (millicode) в процессорах z/series

- •Организация внутренней памяти. Уровни процессорной памяти.

- •Лекция № 11 (17.05.12) Адресация внутренней памяти.

- •Динамическая трансляция адреса

- •Подсистемы ввода/вывода Назначение и компоненты системы в/в

- •Лекция № 12 (24.05.12)

- •Множественная подканальная система mcss.

- •Лекция № 13 (12)

Лекция № 11 (17.05.12) Адресация внутренней памяти.

Различают 3 базовых типа адресных пространств (Address Space AS) и соответствующие их типы адресов:

абсолютные. Абсолютный адрес однозначно соответствует номеру байта физической памяти.

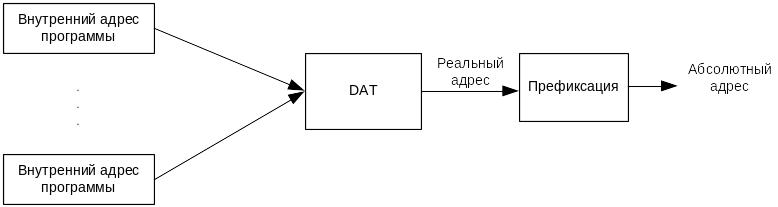

реальные. Р.А. используется в многопроцессорных системах и определяет адрес байта, который преобразуется в абсолютный путем префиксации.

виртуальные. В.А. формируются процессором при выполнении программ и транслируются посредством динамического преобразования адресов (dynamic address translatium – DAT).

Адрес операнда, вычисляемый в машинной команде называется логическим адресом:

где X и B – содержимое индексного и базового регистров, а D – смещение в байтах.

Логический адрес м.б. реальным, если DAT отключен, или виртуальным.

В регистре префикса (8 Кбайт) находится адресный префикс, который ставится перед реальным адресом и получается абсолютный адрес.

Динамическая трансляция адреса

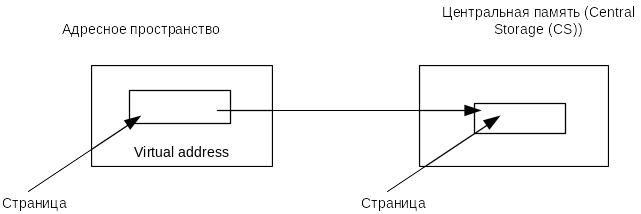

Виртуальное адресное

пространство имеет объем

.

Память делится на блоки по 4 Кбайта

(указывается область и страница)

.

Память делится на блоки по 4 Кбайта

(указывается область и страница)

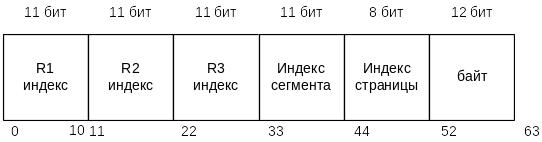

64-ти битный виртуальный адрес

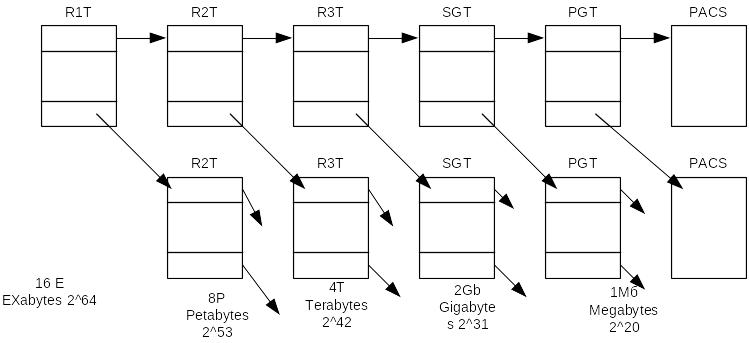

Для адресации виртуальной памяти требуется 5 уровней таблиц трансляции:

таблицы областей памяти 1,2,3 уровня (region tables) R1T, R2T, R3T, таблицы сегментов SGT и страниц PGT.

Индексы задают номера строк в соответствующих таблицах. В строках таблиц находится ссылка на таблицу нижнего уровня, а в таблицах страниц – адрес начала страницы в реальной памяти. Поле байт указывает смещение байта в реальной памяти относительно начала страницы. Имеется бит в таблице страниц, который указывает размещение страницы в реальной памяти. Если этот бит равен 1 – то страница не размещена в ОП. В этом случае DAT вызывает программное прерывание, чтобы необходимая страница была прочитана из внешней памяти. DAT может потребовать до 5 обращений в таблицы и время преобразования может быть слишком большим. Для уменьшения этого времени в DAT вводится буфер быстрого преобразования TLB (translation –Lookaside Buffer). В литературе такой буфер иногда называют кэш-памятью адресов. Каждый процессор имеет свой буфер TLB. Процессор обращается к таблице DAT только при первом преобразовании виртуального адреса. Полученные из таблицы атрибуты (строки индекса и адреса записываются в строках TLB). При последующих обращениях с теми же атрибутами выполняется обращение в TLB без обращений в ОП.

Подсистемы ввода/вывода Назначение и компоненты системы в/в

Назначение подсистемы – выполнение операции в/в, включающих процедуры настройки и управления периферийными устройства (ПУ) для обмена информацией между ними и ОП сервером.

Z-Series – это подсистема называется канальной подсистемой Channel Subsystem – CSS. Основу CSS составляют каналы, выполняющие в/в под управлением канальных программ. CSS освобождает ЦП от рутинных операций и функционирует параллельно с ними.

Основные компоненты CSS:

внешнее запоминающее устройство

устройство в/в

Номер устройства задается 16 разрядным кодом и допускается до 65 тысяч и допускается до 536 устройств.

Устройства управления (контроллеры) CU – обеспечивают адаптацию типовых процедур к конкретным особенностям устройств. Контроллер принимает команды от CSS, дешифрирует и вырабатывает управляющие сигналы для ПУ.