- •Управление в режиме раздельных выходов

- •Триггер Шмитта

- •Большие и сверхбольшие интегральные схемы.

- •Проблемы повышения степени интеграции.

- •Надежность ис

- •Методы оценки надёжности.

- •Матричная организация озу.

- •Статическая зя на однотипных моп-транзисторах

- •Динамическая зя на однотипных моп-транзисторах.

- •Основные параметры озу:

- •Функциональная электроника

- •Криоэлектроника

- •Спинтроника

- •Переход к наноэлектронике

- •2)Эффект Холла

- •3)Эффект кулоновской блокады

- •4)Эффект гигантского магнитного сопротивления

- •5)Эффект(принцип) суперпозиции квантовых состояний

- •"Кремний-на-изоляторе"

- •Транзисторы с двойным и с окольцовывающим затвором

- •С двойным затвором

- •С окольцовывающим затвором

- •Транзисторы с вертикальным каналом

- •Лазеры с квантовыми ямами и точками

- •Фотоприемники на квантовых ямах

- •Квантово-точечные клеточные автоматы и беспроводная электронная логика

- •Новые материалы наноэлектроники

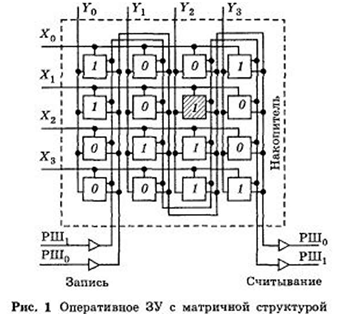

Матричная организация озу.

Отдельная ЗЯ расположена в узлах «решетки», образованной адресными шинами X и Y. Количество ячеек равно произведению количества горизонтальных шин на количество вертикальных. Каждая ЗЯ связана с одной горизонтальной и одной вертикальной адресными шинами. Поэтому, если подаются напряжения на определенные горизонтальную и вертикальную шины (например, Х1 и Y2), то к периферии подключается вполне определенная 3Я (на рис.1 заштрихована). В эту ячейку (с уникальным адресом X1Y2) можно либо записать необходимый бит информации («0» или «1»), либо считать информацию из ячейки (в ячейке ЗЯ12 записана «1»).

И запись, и считывание осуществляется с помощью разрядных шин РШ1 и РШ0, которые подключены ко всем ЗЯ. При записи выходы считывания отключаются, и на разрядные шины подают один из двух наборов (01 или 10), в зависимости от того, какое число желательно хранить в ЗЯ (на рис.1 в клетках указаны уровни на главных выходах ячеек). При считывании входы записи отключаются и уровни, характеризующие состояние ЗЯ, поступают через усилители в соответствующие внешние узлы.

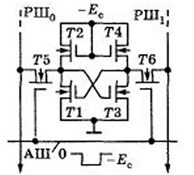

Статическая зя на однотипных моп-транзисторах

с р-каналом имеет классическую структуру RS-триггера с управляющими ключами T5 и T6. Эти ключи нормально заперты и ЗЯ отключена от разрядных шин. При поступлении отрицательного импульса –Ес на адресную шину ключи T5 и T6 отпираются и подключают ячейку к разрядным шинам. При этом на разрядные шины поступят уровни Q и Q, записанные в ячейке. В режиме записи на адресную шину также подается импульс –Ес, а на разрядные шины подаются необходимые (взаимно противоположные) уровни, которые приводят ячейку в соответствующее состояние. Таким образом, импульс на адресной шине в обоих режимах играет роль тактового импульса.

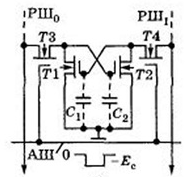

Динамическая зя на однотипных моп-транзисторах.

Хранение бита информации осуществляется емкостями C1 и С2. Методика записи и считывания — та же, что и в предыдущей ячейке. Пусть при записи на разрядные шины РШ1 и РШ0 поданы соответственно уровни –Ес и 0. Уровень –Ес через ключ T4 поступит на затвор транзистора Т1, и этот транзистор будет открыт. На затвор транзистора Т2 поступит уровень 0, и этот транзистор будет заперт. Напряжения на емкостях будут иметь значения Uc1 = –Ес, UC2 = 0. Если остаточный ток запертого транзистора Т2 достаточно мал, то емкость C1 будет разряжаться весьма медленно и, следовательно, напряжения –ЕС и 0 будут сохраняться на выходах ячейки (на стоках) длительное время. За это время можно несколько раз считывать информацию из ячейки (хотя при считывании емкость дополнительно шунтируется цепями считывания и ее разряд ускоряется). Для того чтобы поддерживать напряжение на емкости, несмотря на неизбежный ее разряд, осуществляют регенерацию (периодическая запись того же кода). Динамические ЗЯ значительно экономичнее статических, так как у них отсутствует источник питания и, следовательно, в режиме хранения они не потребляют мощность.

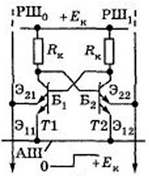

ЗЯ на многоэмиттерных БПТ.

Принципы записи и считывания здесь такие же, как и в предыдущих ЗУ, если не считать положительных полярностей логических уровней и адресного (тактового) импульса. Пусть в режиме хранения транзистор Т2 заперт, а Т1 насыщен, тогда Uб1 = U* и Uб2 ≈ 0. Если на разрядных шинах задан небольшой (0,1–0,2 В) «дежурный» потенциал, то эмиттерный переход Э21 будет практически заперт и весь ток будет проходить через Э11; в транзисторе Т2 будут заперты оба эмиттерных перехода.

При считывании, когда на адресную шину подается положительное напряжение Ек, эмиттер Э11 запирается и ток транзистора Т1 протекает в шину РШ0 через эмиттер Э21, который остался под низким потенциалом; шина РШ1 остается обесточенной. При записи одновременно с адресным импульсом подается напряжение +ЕК на ту разрядную шину, которая связана с транзистором, подлежащим запиранию. В нашем примере, если подать напряжение Ек на шину РШ1, то транзистор Т2 останется запертым и состояние ЗЯ не изменится. Если же подать напряжение Ек на шину РШ0, то окажутся запертыми оба эмиттера транзистора Т1. Тогда ток потечет через базу транзистора Т2 в эмиттер Э22, который находится под низким потенциалом шины РШ1. При этом транзистор Т2 откроется, т. е. состояние ЗЯ изменится на обратное.