Лабораторная работа №1

.docСанкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. Ульянова (Ленина)

Кафедра САПР

Отчет по лабораторной работе №1:

«RS -, D - и JK – триггеры»

По дисциплине «Схемотехника»

Выполнили: Дюсебаев Т.

Сиснерос-Камышев М.

Гр. 3372

Проверил: Фахми Ш. С.

Санкт-Петербург, 2005

1. RS-Триггеры

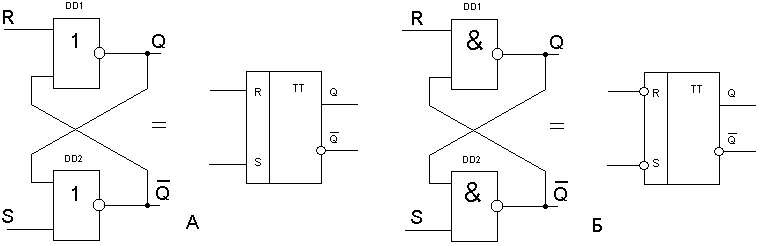

В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами. Их схемы и условные обозначения приведены на рисунке. Триггеры такого типа построены на двух логических элементах 2ИЛИ-НЕ - триггер с прямыми входами (а), 2И-НЕ - триггер с инверсными входами (б).

Рис. 1

Выход каждого из элементов подключен к одному из выходов другого элемента. Здесь приведены таблицы истинности для каждого из этих триггеров:

|

S |

R |

Qt |

-Qt |

Qt+1 |

-Qt+1 |

|

S |

R |

Qt |

-Qt |

Qt+1 |

-Qt+1 |

|

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

1 |

* |

* |

|

1 |

1 |

0 |

1 |

* |

* |

|

1 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

* |

* |

|

1 |

1 |

1 |

0 |

* |

* |

|

1 |

1 |

1 |

0 |

0 |

1 |

В таблицах (Qt и -Qt обозначают уровни, которые были на выходах триггера до подачи на его входы так называемых активных уровней. Активным. называют логический уровень, действующий на входе логического элемента и однозначно определяющий логический уровень выходного сигнала (независима от логических уровней, действующих на остальных входах). Для элементов ИЛИ-НЕ за активный уровень принимают высокий уровень, а для элементов И-НЕ - низкий уровень. Уровни, подача которых на один из входов не приводит к изменению логического уровня на выходе элемента, называют пассивными. Уровни Qt+1 и -Qt+1 обозначают логические уровни на выходах Триггера после подачи информации на его входы.

Для триггера с прямыми входами Qt+1=1 при S=1 и R=0; Qt+1=0 при S=0 и R=1; Qt+1= Qt при S=0 и R=0. При R=S=1 состояние триггера будет неопределенным, так как во время действия информационных сигналов Логические уровни на выходах триггера одинаковы (Qt+1=-Qt+1=0), а после окончания их действия триггер может равновероятно принять любое из устойчивых состояний. Поэтому такая комбинация является запрещенной (и может вывести триггер из строя).

Режим S=1, R=0 называют режимом записи 1 (так как Qt+1=1); режим S=0 и R=1 - режимом записи 0. Режим S=0, R=О называется режимом хранения информации, так как информация на выходе остается неизменной. Для триггера с инверсными входами режим записи логической 1 реализуется при -S=0, -R=1, режим записи логического 0 - при -S=1, -R=0. При -S=-R=1 обеспечивается хранение информации. Комбинация S=R=0 является запрещенной.

Следует, однако, отметить, что самостоятельно RS-триггеры в устройствах цифровой техники практически не используются из-за их низкой помехоустойчивости

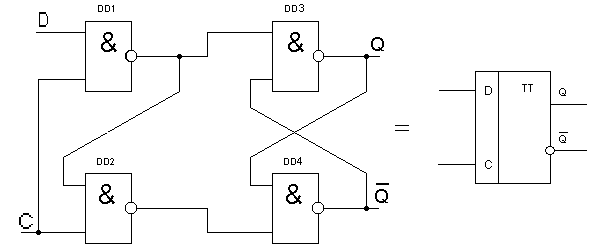

2. D-Триггер

Он имеет информационный выход и вход синхронизации. Одна из возможных структурных схем однотактного D-триггера и его условное обозначение показаны на рисунке.

Рис. 2

Если уровень сигнала на входе C= 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе. При этом на входы RS-триггера с инверсными входами (элементы 3 и 4) поступают пассивные уровни (-S=-R=1). При подаче на вход синхронизации уровня С=1 информация на прямом выходе будет повторять информацию, подаваемую на вход D. Таким образом, при C=0 Qt+1=Qt, C=1 Qt+1=D). Таблица истинности тактируемого D-трнггера имеет вид:

|

D |

C |

Qt+1 |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

Здесь Qt означает логический уровень на прямом выходе до подачи импульса синхронизации, а Qt+1 - логический уровень на этом выходе после подачи импульса синхронизации.

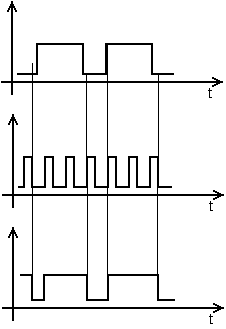

На рисунке 3 изображены временные диаграммы тактируемого D-триггера. В таком триггере происходит задержка сигнала на выходе по отношению к сигналу, поданному на вход. на время паузы между синхросигналами. Для устойчивой работы триггера необходимо, чтобы в течение синхроимпульса информация на входе была неизменной.

Тактируемые D-триггеры могут быть с потенциальным и динамическим управлением. У первых из них информация записывается в течение времени, при котором уровень сигнала С=1. В триггерах с динамическим управлением информация записывается только в течение перепада напряжения на входе синхронизации. Динамические входы изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы, то триггер срабатывает по фронту входного импульса, если от нее - по срезу. Еще в схемах вы встретите / и \ обозначения первое соответственно фронт второе спад. В таком триггере информация на входе может быть задержана на один такт по отношению к входной информации.

Рис. 3

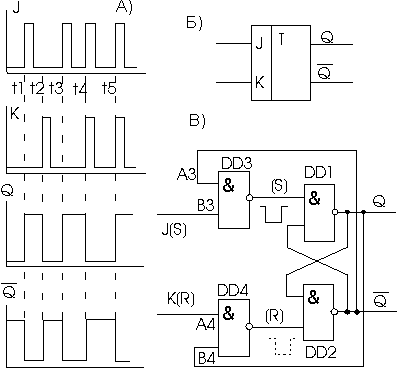

3. JK-Триггер

Триггер типа JK представляет собой устройство с двумя устойчивыми выходными состояниями, обладающее двумя информационными входами J и K (рис. 7.1). По принципу действия он сходен с RS-триггером, с той разницей, что в состояниях JK-триггера нет неопределенности при одновременном поступлении сигналов высокого уровня на оба входа. На рис. 7.1В показана схема JK-триггера на ЛЭ И-НЕ. Она отличается от схемы RS-триггера только тем, что элементы DD3 и DD4 включены не как инверторы, а по входам A3 и A4 управляются сигналами с выходов триггера /Q и Q, соответственно.

Работу схемы поясняет рис. 7.1А. Если JK-триггер находится в нулевом состоянии (Q = 0, a /Q = 1 -до момента t1) и на вход J поступит сигнал показанного на рисунке вида, на выходе DD3 за счет связи выхода /Q с входом A3, возникнет сигнал низкого уровня. Он будет действовать подобно сигналу /S на входе /R/S-триггера, образованного элементами DD1 и DD2, т. е. вызовет смену состояния триггера. Если JK-триггер пребывал в единичном состоянии (Q = 1 и /Q = 0 - до момента t2) и сигнал поступит на вход K, то, рассуждая аналогично, можно убедиться, что на выходе DD4 возникает сигнал (показан на рисунке штрихами), который действует подобно сигналу /R, т. е. состояние триггера снова изменится (в этом случае на выходе DD3 напряжение высокого уровня). Когда на обоих входах J и К одновременно напряжение низкого уровня, состояние триггера сохраняется

Рис. 7.1. JK-триггер: А - временная диаграмма работы, Б - условное графическое обозначение, В - схема с четырмя ЛЭ И-НЕ

Когда на входы J и К одновременно поступает напряжение высокого уровня, дальнейшее поведение триггера зависит от его исходного состояния.

1. Исходное состояние JK-триггера - единичное (Q = 1 и /Q = 0 - после момента t3). За счет связи /Q с A3 на входе A3 = 0 и на выходе DD3 сохраняется напряжение высокого уровня, на которое сигнал J= 1 на входе Вз не влияет. В то же самое время на выходе элемента И-НЕ (DD4) вследствие связи входа В4 с выходом Q (Q = 1) появится сигнал /R, от которого /R/S-триггер, состоящий из DD1 и DD2, сменит состояние (Q = 0, a /Q = l - после момента t4).

2. Исходное состояние триггера - нулевое (Q = 0 и /Q = 1 - после момента t4). Рассуждая аналогично, нетрудно убедиться, что на выходе DD4 сохранится напряжение высокого уровня, а на выходе DD3 появится сигнал /S, который сменит состояние /R/S-триггера (Q = 1, /Q = 0 - после момента t5).

Таким образом, в обоих случаях JK-триггер меняет свое состояние. В этом и состоит различие между JK- и RS-триггерами.

Работа JK-триггера определяется следующей таблицей состояний:

|

J |

K |

Qn+1 |

/Qn+1 |

|

0 |

0 |

Qn |

/Qn |

|

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

|

1 |

1 |

/Qn |

Qn |

Цель работы: Спроектировать RS-, D- и JK- триггеры в среде Triscend FastChip 2.6 и проверить их работоспособность на плате.

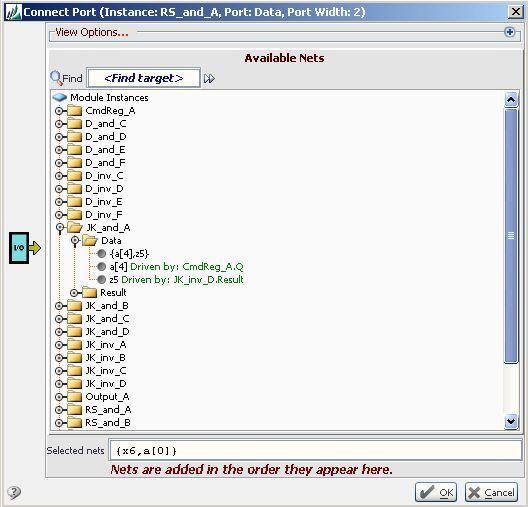

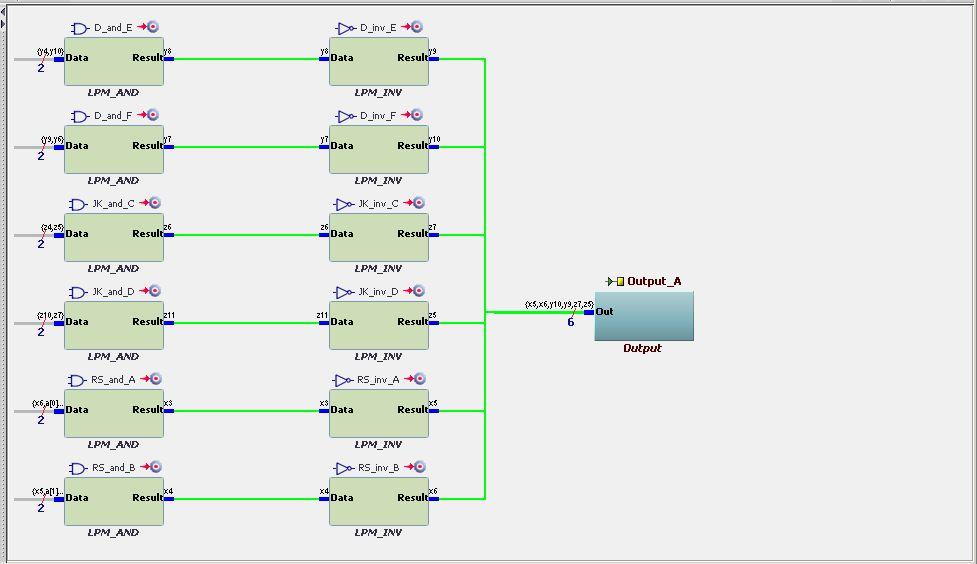

Описание: Для проектирования RS-, D- и JK- триггеров нам понадобятся логические элементы И и НЕ. В библиотеке Triscend FastChip 2.6 они называются LPM_AND и LPM_NOT соответственно. Мы переименовали их в нашей работе для удобства следующим образом: RS_and_A, RS_and_B, JK_inv_A, JK_inv_B и т.д. Для соединения вскх этих элементов в RS-, D- и JK-триггеры необходимо проименовать их входы и выходы таким образом, чтобы имя выхода элемента совпадало с именем входа элемента с которым он должен быть соединен:

-

В нашей работе мы задействовали все 3 триггера одновременно.

-

Ко входам каждого из триггеров подключается Регистр комманд (Command Register), который в библиотекек FastChip 2.6 называется CmdReg_A.

-

Выходы триггера подключаются к выходному регистру (Output_A):

Далее делаем связывание (Bind), если оно прошло безошибочно, то можем приступать к следующему этапу проектирования.

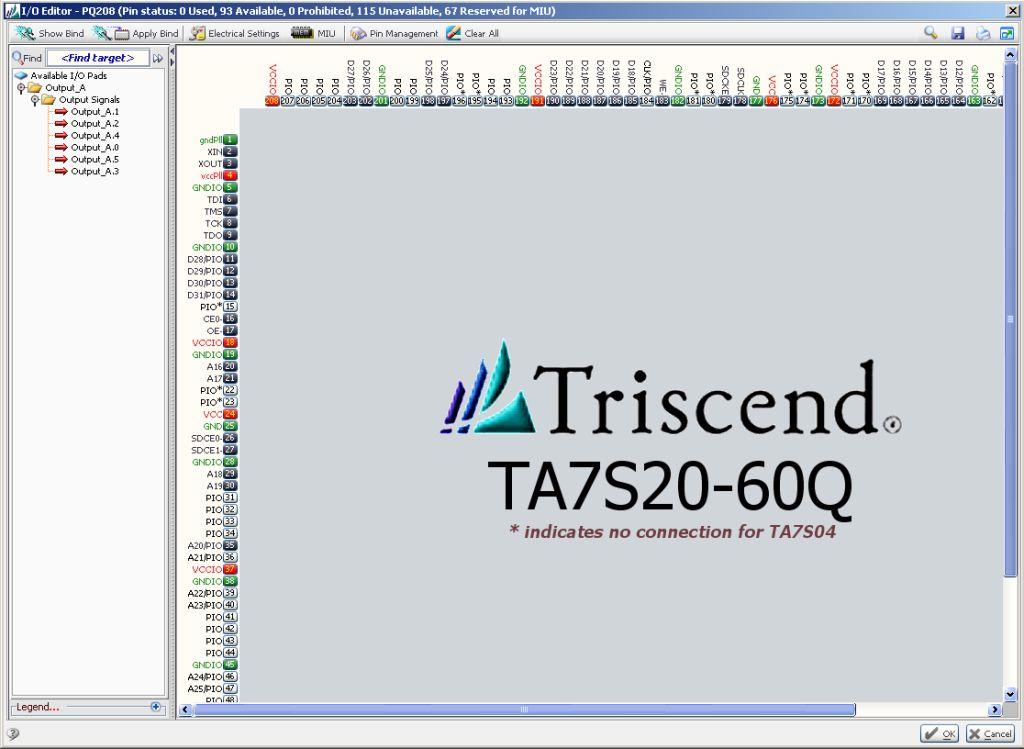

С помощью I/O Editor’a подключаем нужные нам выходы к ножкам кристалла:

Например:

-

15 – светодиод.

-

127, 126, 101, 102 и т.д. – сегменты индикатора

В нашей работе:

-

127, 135, 103 ножки подключенные к сегментам индикатора необходимые для отображения буквы «Г».

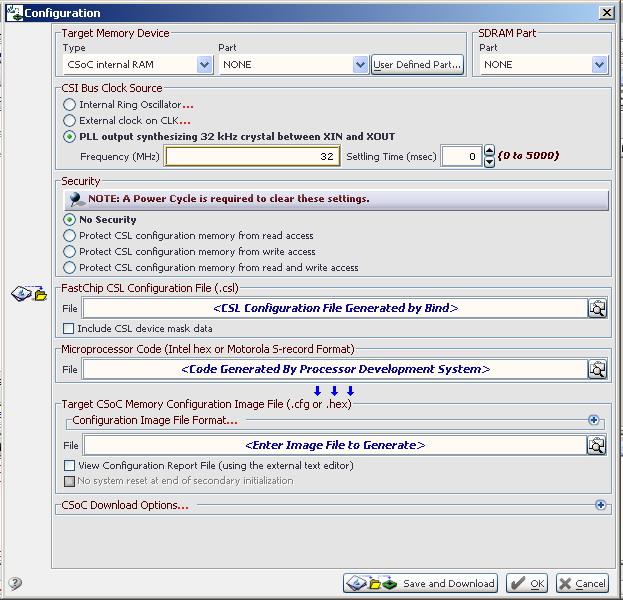

Завершающий этап осуществляется в Triscend FastChip Device Link Utility. В пункте меню Tools -> Device Link Options прописывается IP-адрес компьютера, к которому подключена плата. Далее в меню configuration задаем частоту (32 КГц):

На плате индикаторе платы должна загорется буква «Г».

Выводы:

-

В ходе выполнения мы ознакомились с RS-, D- и JK-триггерами, их функциональными способностями и таблицами истинности.

-

Также получили начальные сведения о среде Triscend FastChip 2.6 и ее возможностях в процессе проектирования триггеров.