- •Розділ і Теоретична частина

- •1.1 Керуючі регістри процесора Структура керуючих регістрів процесора

- •Структура регістру прапорців процесора

- •1 .2 Перемикання між режимами

- •1.3 Формування фізичної адреси

- •Формування лінійної адреси без участі селекторів.

- •Формування лінійної адреси в захищеному режимі

- •Сторінкове перетворення адрес

- •1.4 Захист по привілеях

- •Захист на рівні сегментів

- •Захист на рівні сторінок

- •1.5 Мультизадачність

- •1 .6 Особливості режиму системного управління

- •Порівняльні характеристики режимів процесора

- •Розділ іі Практична частина

- •2.1 Алгоритм роботи програми

- •2.2 Програма обчислення значення виразу

- •Висновки

- •Список використаної літератури

Формування лінійної адреси в захищеному режимі

Особливістю захищеного режиму є використання селекторів і дескрипторів для звернення до пам'яті.

Дескриптор - це 8-байтна одиниця описової інформації, розпізнавана пристроєм управління пам'яттю в захищеному режимі, що зберігається в дескрипторній таблиці. Дескриптор сегмента містить базову адресу описуваного сегмента, межу сегмента і права доступу до сегменту.

Д

Рис.

1.5 Формування лінійної адреси в захищеному

режимі

визначається регістрами процесора GDTR, IDTR, LDTR. Регістри GDTR і IDTR - 6-байтні, вони містять 32 біта лінійної базової адреси дескрипторної таблиці і 16 біт межі таблиці. Програмно доступна частина регістру LDTR - 16 біт, які є селектором LDT. Дескриптори LDT знаходяться в GDT. Однак щоб не звертатися щоразу до GDT в процесорі є тіньова (програмно недоступна) частину регістра LDTR, в яку процесор поміщає дескриптор LDT при кожному перевантаження селектора в регістрі LDTR.

Значення, що поміщаються в сегментні регістри, називаються селекторами. Селектор містить індекс дескриптора в дескрипторній таблиці, біт який визначає, до якої дескрипторної таблиці проводиться звернення (LDT чи GDT), а також запитувані права доступу до сегменту. Таким чином, селектор вибирає дескрипторну таблицю, вибирає дескриптор з таблиці, а по дескриптору визначається положення сегмента в лінійному просторі пам'яті. Проте звернення до дескрипторних таблиць відбувається тільки при завантаженні селектора в сегментний регістр. При цьому процесор поміщає дескриптор в тіньову (програмно недоступну) частину сегментного регістра. При формуванні лінійної адреси дескриптор сегмента процесору вже відомий.

Сторінкове перетворення адрес

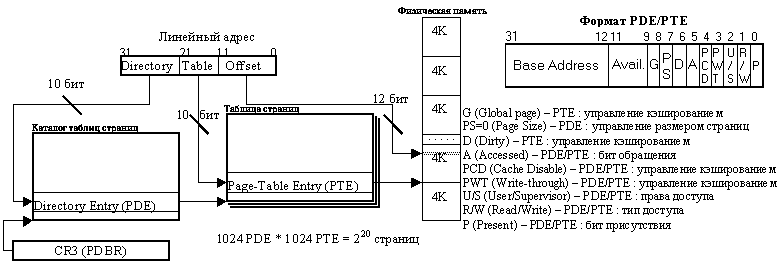

Механізм сегментації забезпечує чудовий захист, але він не дуже зручний для реалізації свопінгу (підкачки). У дескрипторі сегмента є біт присутності, по ньому процесор визначає, чи знаходиться даний сегмент у фізичній пам'яті чи він знаходиться на вінчестері. В останньому випадку генерується виключення # 11, обробник якого може довантажити сегмент в пам'ять. Незручність полягає в тому, що різні сегменти можуть мати різну довжину. Цього можна уникнути, якщо механізм підкачки реалізовувати на основі сторінкового перетворення. Особливістю цього перетворення є те, що процесор у цьому випадку оперує з блоками рівної довжини (4 Кбайт) - сторінками.

У

сторінковому перетворенні беруть участь

два типи структур: каталоги таблиць і

таблиці сторінок. Ці структури складаються

з 1024 32-бітних елементів. Елементи містять

старші 20 біт фізичної адреси об'єктів,що

адресуються. Елементи таблиці сторінок

адресують сторінки, а елементи каталогу

таблиць адресують таблиці сторінок.

Старші 20 біт фізичної адреси каталогу

таблиць зберігається в регістрі CR3 (Page

Directory Base Register). (Це єдиний регістр

процесора, який містить фізичну адресу

пам'яті). Всі структури вирівняні по

межі сторінки.

У

сторінковому перетворенні беруть участь

два типи структур: каталоги таблиць і

таблиці сторінок. Ці структури складаються

з 1024 32-бітних елементів. Елементи містять

старші 20 біт фізичної адреси об'єктів,що

адресуються. Елементи таблиці сторінок

адресують сторінки, а елементи каталогу

таблиць адресують таблиці сторінок.

Старші 20 біт фізичної адреси каталогу

таблиць зберігається в регістрі CR3 (Page

Directory Base Register). (Це єдиний регістр

процесора, який містить фізичну адресу

пам'яті). Всі структури вирівняні по

межі сторінки.

Рис. 1.6 Сторінкова трансляція пам’яті

У процесі сторінкової трансляції адрес отримана лінійна адреса розбивається на три частини. Старші десять біт лінійної адреси є індексом елемента з каталогу таблиць. З цього елементу визначається фізичну адресу таблиці сторінок. Біти 21-12 лінійної адреси вибирають елемент з цієї таблиці сторінок. Обраний елемент визначає фізичну адресу сторінки. Молодші 12 біт лінійної адреси визначають зміщення від початку сторінки.

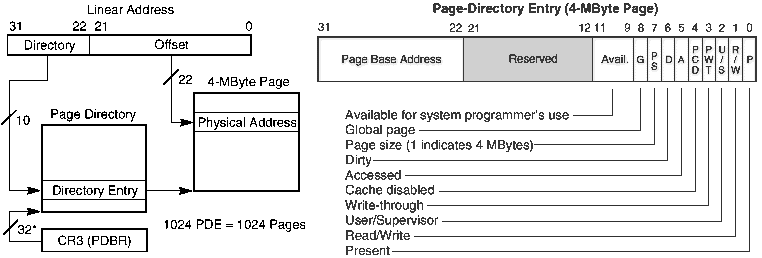

У процесорах, починаючи з Pentium, сторінки можуть мати розмір 4 Кбайт або 4 Мбайт (ця можливість називається розширенням розміру сторінок), а в процесорах з архітектурою P6 при включеному розширенні фізичної адреси – 4 Кбайт або 2 Мбайт. (Розширення фізичної адреси полягає у використанні 36-бітної фізичної адреси замість 32-бітної.) Розширення розміру сторінок включається установкою біта 4 (Page Size Extension) в регістрі CR4, а розширення фізичної адреси - установкою біта 5 (Physical Address Extension) в регістрі CR4 . Обидві можливості працюють тільки в захищеному режимі при включеній сторінковій трансляції адрес. У табл.1.1 показані можливі сполучення керуючих бітів і їх сукупний результат.

PG (CR0) |

PAE (CR4) |

PSE (CR4) |

PS (PDE) |

Размір сторінки |

Розрядність фізичної адреси |

0 |

x |

x |

x |

- |

32 біт |

1 |

0 |

0 |

x |

4K |

32 біт |

1 |

0 |

1 |

0 |

4K |

32 біт |

1 |

0 |

1 |

1 |

4M |

32 біт |

1 |

1 |

x |

0 |

4K |

36 біт |

1 |

1 |

x |

1 |

2M |

36 біт |

Табл. 1.1 Можливі сполучення керуючих бітів

Рис.

1.7 Таблиця сторінок

системи, до якого часто звертаються всі програми і який не слід вивантажувати з пам'яті, при цьому заощаджується місце - не потрібні проміжні таблиці сторінок.

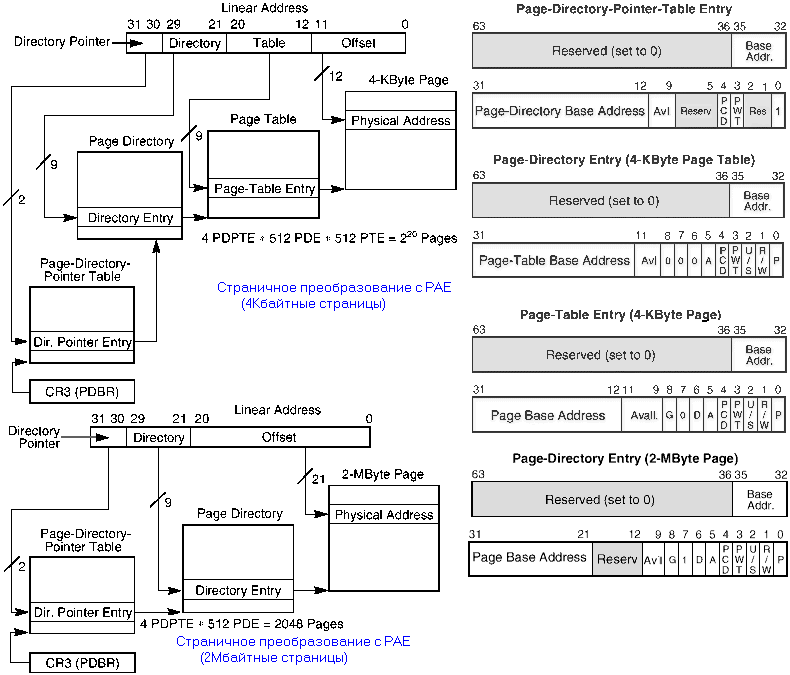

Рис.

1.8 Сторінкове перетворення з PAE

У

процесорах з архітектурою P6 шина адреси

36-розрядна, проте для того, щоб процесор

генерував 36-бітові адреси необхідно

включити PAE. Для того, щоб зберігати

фізичну адресу більшої розрядності

розмір елементів каталогів таблиць і

таблиць сторінок збільшено до 64 біт, а

число елементів скорочено до 512 (щоб

кожна структура займала рівно 4Кбайт -

одну сторінку пам'яті). Скорочення числа

елементів призвело до зменшення розмірів

індексів, в результаті вивільнилося

два старших біта в лінійній адресі. Вони

використовуються для індексації ще

однієї структури - таблиці покажчиків

на каталоги таблиць сторінок (PDPT). Ця

таблиця містить чотири 64-бітних елемента,

які задають фізичні адреси каталогів

таблиць. Якщо при 32-бітній адресації

активний лише один каталог таблиць,

старші 20 біт адреси якого зберігаються

в регістрі CR3 (PDBR), то при 36-бітній адресації

активних каталогів 4. Їх адреси зберігаються

в PDPT, а регістр CR3 в цьому випадку зберігає

адресу PDPT (старші 27 біт фізичної адреси

в бітах 5-31 регістру CR3) і називається

Page-Directory-Pointer Table Register. Таким чином,

формування фізичної адреси для 4Кбайтних

сторінок трирівневе, а для 2Мбайтних

сторінок - дворівневе.

У

процесорах з архітектурою P6 шина адреси

36-розрядна, проте для того, щоб процесор

генерував 36-бітові адреси необхідно

включити PAE. Для того, щоб зберігати

фізичну адресу більшої розрядності

розмір елементів каталогів таблиць і

таблиць сторінок збільшено до 64 біт, а

число елементів скорочено до 512 (щоб

кожна структура займала рівно 4Кбайт -

одну сторінку пам'яті). Скорочення числа

елементів призвело до зменшення розмірів

індексів, в результаті вивільнилося

два старших біта в лінійній адресі. Вони

використовуються для індексації ще

однієї структури - таблиці покажчиків

на каталоги таблиць сторінок (PDPT). Ця

таблиця містить чотири 64-бітних елемента,

які задають фізичні адреси каталогів

таблиць. Якщо при 32-бітній адресації

активний лише один каталог таблиць,

старші 20 біт адреси якого зберігаються

в регістрі CR3 (PDBR), то при 36-бітній адресації

активних каталогів 4. Їх адреси зберігаються

в PDPT, а регістр CR3 в цьому випадку зберігає

адресу PDPT (старші 27 біт фізичної адреси

в бітах 5-31 регістру CR3) і називається

Page-Directory-Pointer Table Register. Таким чином,

формування фізичної адреси для 4Кбайтних

сторінок трирівневе, а для 2Мбайтних

сторінок - дворівневе.