- •Розділ і Теоретична частина

- •1.1 Керуючі регістри процесора Структура керуючих регістрів процесора

- •Структура регістру прапорців процесора

- •1 .2 Перемикання між режимами

- •1.3 Формування фізичної адреси

- •Формування лінійної адреси без участі селекторів.

- •Формування лінійної адреси в захищеному режимі

- •Сторінкове перетворення адрес

- •1.4 Захист по привілеях

- •Захист на рівні сегментів

- •Захист на рівні сторінок

- •1.5 Мультизадачність

- •1 .6 Особливості режиму системного управління

- •Порівняльні характеристики режимів процесора

- •Розділ іі Практична частина

- •2.1 Алгоритм роботи програми

- •2.2 Програма обчислення значення виразу

- •Висновки

- •Список використаної літератури

1 .6 Особливості режиму системного управління

Режим системного управління призначений для виконання деяких дій з можливістю їх повної ізоляції від прикладного програмного забезпечення і навіть операційної системи. Перехід в цей режим відбувається тільки апаратно. Коли процесор знаходиться в режимі SMM, він виставляє сигнал SMIACT #. Цей сигнал може служити для включення виділення фізичної пам'яті (System Management RAM), так що пам'ять SMRAM можна зробити доступною тільки для цього режиму.

П

Рис.

1.11 Структура

SMRAM

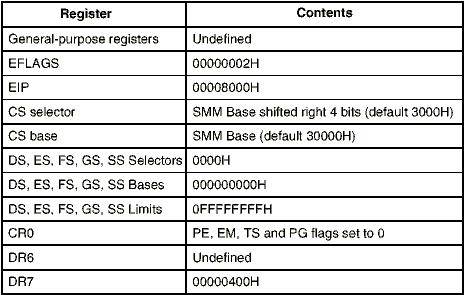

Табл.

1.2 Стан процесора при вході в режим SMM

Слід зазначити, що в режимі SMM не передбачена робота з перериваннями і особливими випадками: переривання по IRQ і SMI# замасковані, покрокові пастки і точки зупину відключені, обробка переривання по NMI відкладається до виходу з режиму SMM. Якщо необхідно забезпечити роботу з перериваннями або особливими випадками, то треба ініціалізувати IDT і дозволити переривання, виставивши прапорець 9 (Interrupt Enable) в регістрі EFLAGS. Перери-вання по NMI будуть розбло-ковані автома-тично після пе-ршої ж команди IRET.

При поверненні з SMM (за інструкцією RSM) процесор відновлює свій контекст із SMRAM. Обробник може програмно внести зміни в образ контексту процесора, тоді процесор перейде не в той стан, в якому відбулося SMI. Якщо SMI було отримано під час виконання інструкції HLT, то подальші дії при виході з SMM визначаються значенням поля "Auto HALT Restart": процесор може знову повернутися до інструкції зупину або перейти до виконання наступної команди. Якщо SMI відбулося при виконанні інструкції вводу-виводу, то в залежності від значення поля "I / O instruction Restart" можливий рестарт інструкції введення виводу.

Ці особливості режиму системного управління дозволяють використовувати його для реалізації системи управління енергозбереженням.

Порівняльні характеристики режимів процесора

Характеристика |

RM |

PM, VM=0 |

PM, VM=1 |

SMM |

Формированння линейної адреси |

без участі селекторів |

через селектори і дескриптори |

без участі селекторів |

без участі селекторів |

Межа сегментів |

64К |

визначається дескриптором |

64К |

4Г |

Размер адреси/даних за замовчуванням |

16 біт |

визначається дескриптором |

16 біт |

16 біт |

Максимальний об’єм доступної пам’яті (віртуальної) |

1M+64K-16 |

64T-2х4Г |

1M+64K-16 |

4Г |

Захист |

Ні |

Так |

Тільки на рівні сторінок |

Ні |

Сторінкове перетворення (в т.ч. PAE) |

Ні |

Так |

Так |

Ні |

Мультизадачність |

Ні |

Так |

Так |

Ні |

Обробка переривань |

IDT – таблиця векторів |

IDT - дескрипторна таблиця |

IDT - дескрипторна таблиця |

IDT - таблиця векторів, необхідна спеціальна ініціалізація |

Табл. 1.3 Порівняння режимів роботи процесора