- •Ознайомлення із стендом мікропроцесорного контролера омк сімейства mcs-51 та виконання команд

- •5 Основні теоретичні положення

- •6 Послідовність виконання роботи

- •8 Контрольні питання:

- •Дослідження схем відображення інформації із статичною індикацією

- •2 Апаратура та прилади: пеом, навчально-налагоджувальний стенд ev8031/avr

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання:

- •Дослідження схем відображення інформації із світлодіодами на омк

- •2 Апаратура та прилади: пеом, навчально-налагоджувальний стенд ev8031/avr

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання:

- •Дослідження схем відображення інформації із динамічною індикацією на омк

- •2 Апаратура та прилади: пеом, навчально-налагоджувальний стенд ev8031/avr

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання:

- •Дослідження програмування омк mcs-51 для роботи із знакосинтезуючим індикатором

- •2 Апаратура та прилади: пеом, навчально-налагоджувальний стенд ev8031/avr

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання:

Комп’ютерна схемотехніка

Лабораторна робота № 6

Ознайомлення із стендом мікропроцесорного контролера омк сімейства mcs-51 та виконання команд

1 Мета роботи: вивчення функціональних можливостей навчально-налагоджувального стенду, внутрішньої структури та команд однокристального мікроконтролера сімейства MCS-51

2 Апаратура та прилади: ПЕОМ, навчально-налагоджувальний стенд EV8031/AVR

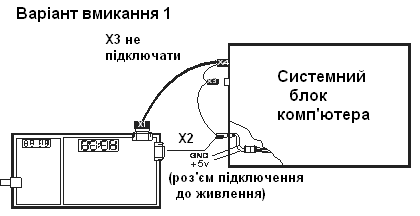

3 Схема підключення стенда:

Підключення напруги живлення стенда (+5 В) і зв’язок з персональним комп’ютером здійснюється універсальним кабелем зв’язку з комп’ютером (DB9+DB25+живлення) за схемою рисунка 1.

Рисунок 1 – Схема підключення стенда до ПК і живлення

4 Опис стенда:

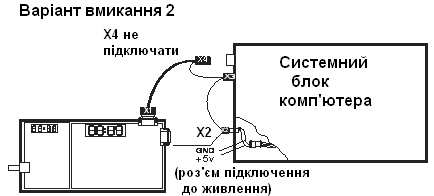

Стенд представляє собою мікропроцесорний контролер, що містить пам’ять програм, пам’ять даних і набір периферійних пристроїв. Структурна схема стенда наведена на рисунку 2, розташування елементів схеми на рисунку 3. Стенд дозволяє налагоджувати програми, написані на мовах Сі і Асемблер. Завантаження програми здійснюється з персонального комп’ютера по послідовному порту RS-232C.

Рисунок 2 – Структурна схема стенда Рисунок 3 – Схема розташування елементів стенду

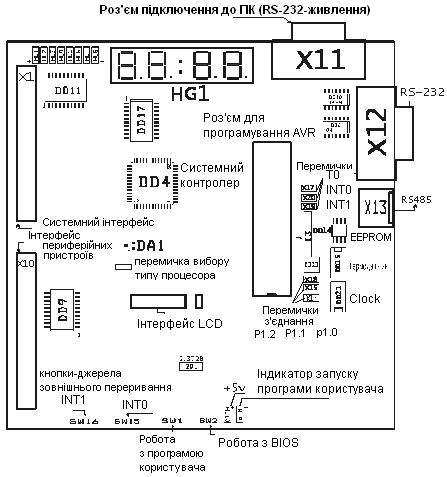

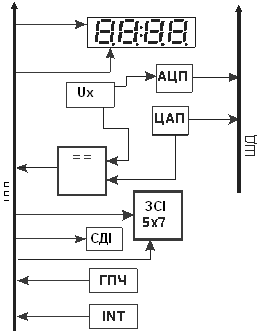

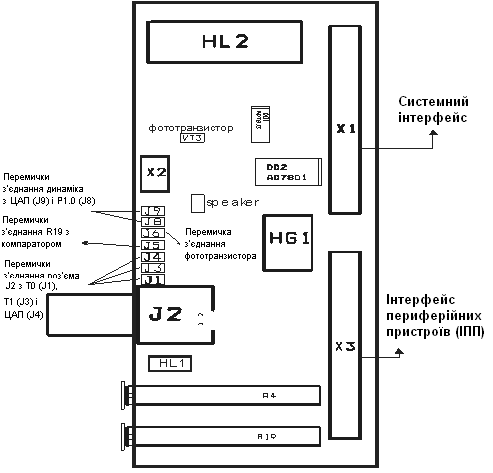

Структурна схема плати розширення наведена на рисунку 4, розташування основних органів керування і мікросхем на платі наведені на рисунку 5.

888 – 4-розрядна динамічна індикація; HG1 – знакосинтезуючий індикатор 5х7;

ЗСІ – знакосинтезуючий індикатор; HL2 – 4-х розрядна динамічна індикація;

ІПП – інтерфейс периферійних пристроїв; J2– роз’єм підключення зовнішніх контрольно-вимірювальних приладів;

СДІ – світлодіодні індикатори; R19–резистор, змінює частоту генерації змінного генератора;

ЦАП – цифро-аналоговий перетворювач; HL1 – індикатор стану виходу компаратора

ГПЧ – генератор із плавно змінюваною частотою; R4 – змінний резистор, джерело вхідного сигналу для АЦП;

АЦП – аналого-цифровий перетворювач;

INT – кнопки запиту переривання;

Uх – джерело вимірюваної напруги;

ШД – шина даних

= = – компаратор;

Рисунок 4–Структурна схема плати розширення Рисунок 5-Розташування елементів плати розширення

5 Основні теоретичні положення

ОМК MCS-51 є мікропроцесорним пристроєм з архітектурою СІSC – з повним набором команд. Система команд містить 111 базових команд форматом 1 – 3 байти. До складу операндів входять булеві дані – біти, цифрові (4 біти), байтові і адресні дані. Всі команди виконуються за 1–2 машинних цикли, тривалість становить 1 або 2 мкс при тактовій частоті 12 МГц, за виключенням команд множення і ділення, які виконуються за 4 машинних цикли тривалістю 4 мкс.

Всі команди MCS-51 поділяються на п’ять функціональних груп:

команди пересилання;

арифметичні команди;

логічні команди;

команди передачі керування;

команди операцій над бітами.

Всього ОМК виконує 13 типів команд, формат яких наведений в таблиці 1. Перший байт команди завжди містить код операції КОП, адресна частина (другий і третій байти), якщо є, містить адреси операндів або їх безпосередні значення.

При виконанні команд використовуються регістри загального призначення (РЗП) з одного з чотирьох банків РПД Rn (n = 0, 1,..., 7).

Операндами може бути комірка резидентної або зовнішньої пам’яті програм або даних, константа – безпосередній операнд, регістри спеціальних функцій і SFR, порти вводу/виводу. Порти і SFR адресуються тільки прямим способом.

Байти пам’яті можуть адресуватися непрямим способом через адресні регістри R0, R1, DPTR, PC.

Акумулятор є джерелом операнду і місцем фіксації результату при виконанні арифметичних, логічних операцій і деяких операцій передачі даних. Крім того, тільки з використанням акумулятора можна виконати операції зсувів, перевірки на нуль, формування прапорця паритету тощо.

#d – безпосередні 8-розрядні дані

ad – байт з РПД за прямою адресацією, в команді вказується або адреса байту 00 – FFН, або позначення одного з регістрів SFR

bit – біт з прямою адресацією, в команді вказується або адреса біта 00 – FFH, або розташування його в регістр спеціальних функцій

/bit - інверсія прямо адресованого біта

rel – відносна адреса одного з переходів

a7 . . . a0 – 8-розрядна адреса

a10 . . . a0 – 11-розрядна адреса

add, ads – байт-приймач і байт-джерело з прямою адресацією

ad16h, ad16l – старший і молодший байти 16-розрядної адреси

#d16h, #d16l – старший і молодший байти безпосередніх 16-розрядних даних.

Таблиця 1 – Формати команд

Тип команди |

1-й байт |

2-й байт |

3-й байт |

1 |

коп |

|

|

2 |

коп |

#d |

|

3 |

коп |

ad |

|

4 |

коп |

bit |

|

5 |

коп |

rel |

|

6 |

коп а10а9a8 |

а7...a0 |

|

7 |

коп |

ad |

#d |

8 |

коп |

ad |

rel |

9 |

коп |

add |

ads |

10 |

коп |

#d |

rel |

11 |

коп |

bit |

rel |

12 |

коп |

ad16h |

ad16l |

13 |

коп |

#d16h |

#d16l |