Руководство пользователя по сигнальным процессорам Sharc

.pdfПамять 5

16 столбцов + 2 столбца в группе = 8 групп.

Получается 8 доступных групп; неиспользуемых столбцов нет. Таким образом, 2 Мбитный блок памяти ADSP 21060, который полностью состоит из 32 разрядных слов, обеспечивает:

8 К × 8 групп = 64 Кслова для хранения данных.

Память ADSP 21061 размещается в восьми 16 разрядных столбцах, следовательно, подобные вычисления можно проделать и для этого процессора:

4 К × 2 группы = 8 Кслов (для хранения команд) 4 К × 4 группы = 16 Кслов (для хранения данных).

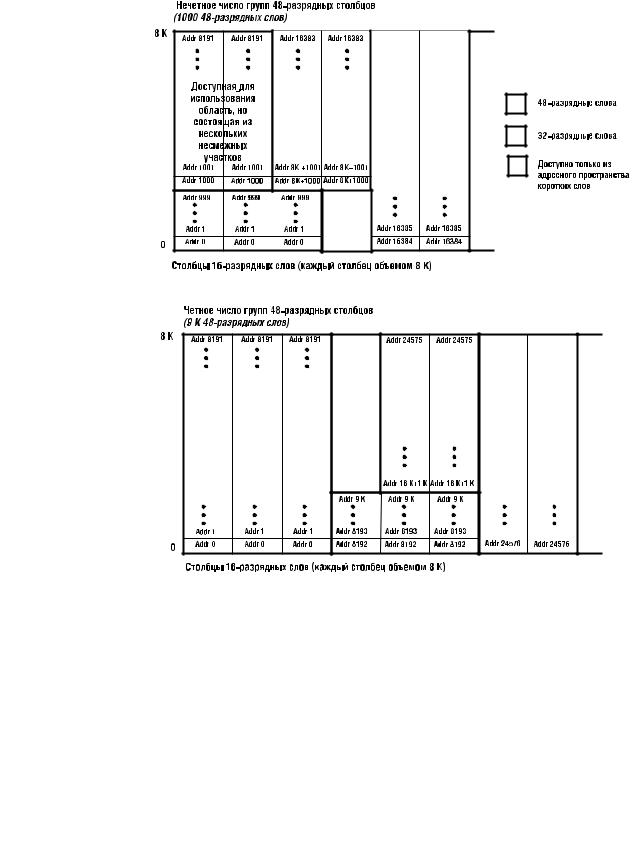

На рис. 5.8 показано расположение 16 разрядных слов внутри 48 разрядных и 32 разрядных слов, а также начальные адреса для каждого столбца памяти ADSP 21060. Конфигурация памяти для ADSP 21062 показана на рис. 5.9а, для ADSP 21061 – на рис. 5.9б.

Блок 0 |

|

|

|

|

|

|

ADSP-21060 (два блока 8 Кx16) |

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48-разрядные слова |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

M |

L |

L |

|

H |

|

M |

H |

|

M |

L |

|

L |

H |

|

M |

H |

|

M |

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

32/16-разрядные |

|

0x20000 |

|

|

0x22000 |

|

0x24000 |

|

|

0x26000 |

|

0x28000 |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

L |

H |

L |

|

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

|

слова |

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x20000 |

|

0x22000 |

|

0x24000 |

|

0x26000 |

|

0x28000 |

|

0x2a000 |

|

0x2c000 |

|

0x2e000 |

|

|||||||||

Блок 1 |

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48-разрядные слова |

|

H |

|

M |

L |

L |

|

H |

|

M |

H |

|

M |

L |

|

L |

H |

|

M |

H |

|

M |

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

32/16- |

|

0x30000 |

|

|

0x32000 |

|

0x34000 |

|

|

0x36000 |

|

0x38000 |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

L |

H |

L |

|

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

|

разрядные слова |

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x30000 |

|

0x32000 |

|

0x34000 |

|

0x36000 |

|

0x38000 |

|

0x3a000 |

|

0x3c000 |

|

0x3e000 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

Замечание: Все адреса обозначают первый элемент каждого столбца.

«Несуществующие» 48-разрядные адреса появляются, когда блок заполнен 48-разрядными командами. Из-за того что имеется определенное количество адресов на блок, вы можете попасть в диапазон 48-разрядных «несуществующих» адресов (адресуемых, но не имеющих содержимого) в конце каждого блока. Эта организация памяти применяется во всех ADSP-2106x, показанных на рис. 5.8, 5.9a и 5.9б.

Рис. 5.8. Организация памяти и начальные адреса в ADSP21060

141

5 Память

Блок 0 |

|

|

|

|

|

|

|

ADSP-21062 (два блока 4 К ґ16) |

|

|

|

|

|

|

|||||||||||

48-разрядные |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

M |

L |

|

L |

H |

|

M |

H |

|

M |

L |

|

L |

H |

|

M |

H |

|

M |

L |

|

|

|

слова |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x20000 |

|

|

0x21000 |

|

0x22000 |

|

|

0x23000 |

|

0x24000 |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

32/16-разрядные |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

|

слова |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x20000 |

|

0x21000 |

|

0x22000 |

|

0x23000 |

|

0x24000 |

|

0x25000 |

|

0x26000 |

|

0x27000 |

|

|||||||||

Блок 1 |

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48-разрядные |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

M |

L |

|

L |

H |

|

M |

H |

|

M |

L |

|

L |

H |

|

M |

H |

|

M |

L |

|

|

|

слова |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x28000 |

|

|

0x29000 |

|

0x2a000 |

|

|

0x2b000 |

|

0x2c000 |

|

|

|

|

||||||||||

32/16-разрядные |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

|

слова |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x28000 |

|

0x29000 |

|

0x2a000 |

|

0x2b000 |

|

0x2c000 |

|

0x2d000 |

|

0x2e000 |

|

0x2f000 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

Замечание: Все адреса обозначают первый элемент каждого столбца.

Рис. 5.9a. Организация памяти и начальные адреса в ADSP21062

Блок 0 |

|

ADSP-21061 (два блока 4 К ґ16) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48-разрядные |

|

H |

|

M |

L |

|

L |

H |

|

M |

|

|

|

слова |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x20000 |

|

|

0x21000 |

|

0x22000 |

|

||||||

|

|

|

|

|

|

||||||||

32/16-разрядные |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

|

слова |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x20000 |

|

0x21000 |

|

0x22000 |

|

0x23000 |

|

|||||

Блок 1 |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48-разрядные |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||

|

H |

|

M |

L |

|

L |

H |

|

M |

|

|

|

|

слова |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x24000 |

|

|

0x25000 |

|

0x26000 |

|

||||||

32/16-разрядные |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

L |

H |

|

L |

H |

|

L |

H |

|

L |

|

слова |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x24000 |

|

0x25000 |

|

0x26000 |

|

0x27000 |

|

|||||

|

|

|

|

|

|

||||||||

Замечание: Все адреса обозначают первый элемент каждого столбца.

Рис. 5.9б. Организация памяти и начальные адреса в ADSP21061

5.3.2. Смешивание 32- и 48-разрядных слов в одном блоке памяти

32 разрядные данные и 48 разрядные команды могут храниться в одном блоке памяти при условии, что адреса всех команд младше адресов данных. Ни одна команда не может храниться по адресу старше, чем самый младший адрес любого слова данных. Это ограничение необходимо для предотвращения перекрытия

142

Память 5

адресов 32 разрядных и 48 разрядных слов. Правила объединения 48 разрядных слов команд и 32 разрядных слов данных внутри одного блока памяти следующие:

♦Команды должны храниться, начиная с самого младшего адреса блока.

♦Данные должны храниться, начиная с четного номера столбца.

♦Все данные должны размещаться по адресам старше, чем адреса всех команд.

♦Для команд требуются три смежных 16 разрядных столбца.

♦Для слов данных требуются два смежных 16 разрядных столбца.

5.3.3. Основные примеры смешивания 32- и 48-разрядных слов

В ADSP 21060 каждый блок памяти физически организован как шестнадцать 16 разрядных столбцов объемом 8 Кслов каждый (в ADSP 21062 – 4 Кслова каждый). На рис. 5.10 показаны четыре основных комбинации смешивания 48 разрядных команд и 32 разрядных данных внутри одного блока:

A.3 столбца для команд, 1 неиспользуемый столбец и 12 столбцов для данных. Этот вариант обеспечивает 8 Кслов для хранения команд и 48 Кслов для хранения данных в ADSP 21060 (4 Кслова для хранения команд и 24 Кслов для хранения данных в ADSP 21062). Один столбец не используется из за того, что 32 разрядные слова данных должны начинаться со столбца с четным номером (в этом случае со столбца 4). В этом примере столбцы с первого по восьмой относятся к ADSP 21061.

B.6 столбцов для команд и 10 столбцов для данных. Этот вариант обеспечивает 16 Кслов для хранения команд и 40 Кслов для хранения данных в ADSP 21060 (8 Кслов для хранения команд и 20 Кслов для хранения данных в ADSP 21062). В этом примере столбцы с первого по восьмой относятся к ADSP 21061.

C.9 столбцов для команд, 1 неиспользуемый столбец и 6 столбцов для данных. Этот вариант обеспечивает 24 Кслова для хранения команд и 24 Кслова для хранения данных в ADSP 21060 (12 Кслов для хранения команд и 12 Кслов для хранения данных в ADSP 21062). Один столбец не используется из за того, что 32 разрядные слова данных должны начинаться со столбца с четным номером (в этом случае со столбца 10). В связи с тем, что в ADSP 21061 есть только восемь столбцов, этот пример не относится к ADSP 21061.

D.12 столбцов для команд и 4 столбца для данных. Этот вариант обеспечивает 32 Кслова для хранения команд и 16 Кслов для хранения данных в ADSP 21060 (16 Кслов для хранения команд и 8 Кслов для хранения данных в ADSP 21062). В связи с тем, что в ADSP 21061 есть только восемь столбцов, этот пример не относится к ADSP 21061.

143

5 Память

32-разрядные данные должны |

|

|

|

|

|

|

|

|

|

|

|

|

|||

начинаться с четного столбца |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

1 столбец = 16 разрядов |

|

|

|

|

||||

(ADSP-21060) 8 К |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ADSP-21062) 4 К |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

1 |

|||||||||||||||

3 столбца для |

|

|

|

|

|

12 столбцов для 32-разрядных данных |

|

|

|

||||||

48-разрядных команд |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

8 Кслов команд (ADSP-21060) |

|

|

|

48 Кслов данных (ADSP-21060) |

|

|

|

|||||||||

4 Кслова команд (ADSP-21062) |

|

|

|

24 Кслова данных (ADSP-21062) |

|

|

|

|||||||||

(ADSP-21060) 8 К |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ADSP-21062) 4 К |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

|

||||||||||||||||

|

6 столбцов для 48-разрядных команд |

|

|

|

10 столбцов для 32-разрядных данных |

|

||||||||||

16 Кслов команд (ADSP-21060) |

|

|

|

40 Кслов данных (ADSP-21060) |

|

|

||||||||||

8 Кслов команд (ADSP-21062) |

|

|

|

20 Кслов данных (ADSP-21062) |

|

|

||||||||||

(ADSP-21060) 8 К (ADSP-21062) 4 К

С

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

|||

|

||||||||||||||||||

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

||||||||||||

|

9 столбцов для 48-разрядных команд |

|

|

|

6 столбцов для 32-разрядных данных |

|||||||||||||

|

24 Кслова команд (ADSP- |

|

|

|

|

|

24 Кслова данных (ADSP-21060) |

|||||||||||

|

21060) 12 Кслов команд |

|

|

|

|

|

12 Кслов данных (ADSP-21062) |

|

|

|||||||||

32-разрядные данные должны начинаться с четного столбца

(ADSP-21060) 8 К (ADSP-21062) 4 К

D

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

|

|||

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 столбцов для 48-разрядных команд |

|

|

4 столбца для 32-разрядных данных |

|||||||||||||||

|

|

32 Кслова команд (ADSP-21060) |

|

|

|

|

16 Кслов данных (ADSP-21060) |

|||||||||||||

|

|

16 Кслов команд (ADSP-21062) |

|

|

|

|

8 Кслов данных (ADSP-21062) |

|||||||||||||

Рис. 5.10. Основные варианты смешивания команд и данных в блоке памяти

144

Память 5

В табл. 5.3 приведены адреса в блоке 0 в ADSP 21060 (начальный адрес=0x0002 0000) для каждой комбинации команд и данных, показанных на рис. 5.10:

|

48 разрядные команды |

32 разрядные данные |

||

|

начальный адрес |

конечный адрес |

начальный адрес |

конечный адрес |

A. |

0х0002 0000 |

0х0002 1FFF |

0х0002 4000 |

0х0002 FFFF |

B. |

0х0002 0000 |

0х0002 3FFF |

0х0002 6000 |

0х0002 FFFF |

C. |

0х0002 0000 |

0х0002 5FFF |

0х0002 A000 |

0х0002 FFFF |

D. |

0х0002 0000 |

0х0002 7FFF |

0х0002 C000 |

0х0002 FFFF |

Таблица 5.3. Диапазон адресов для команд и данных в ADSP21060

Для определения начального адреса 32 разрядных данных используются следующие уравнения (для ADSP 21060):

i Начальный адрес для 32 разрядных данных 0 B + 8K + m + 1

1 B + 16K + m + 1

2 B + 32K + m + 1

3B + 40K + m + 1

B = начальный адрес блока памяти

n = число ячеек 48 разрядных командных слов i = целая часть от [(n 1) ё 8192]

m = (n 1) mod 8192

В табл. 5.4 приведены адреса в блоке 0 в ADSP 21062 (начальный адрес=0x0002 0000) для каждой комбинации команд и данных, показанных на рис. 5.10:

|

48 разрядные команды |

32 разрядные данные |

||

|

начальный адрес |

конечный адрес |

начальный адрес |

конечный адрес |

A. |

0х0002 0000 |

0х0002 0FFF |

0х0002 2000 |

0х0002 7FFF |

B. |

0х0002 0000 |

0х0002 1FFF |

0х0002 3000 |

0х0002 7FFF |

C. |

0х0002 0000 |

0х0002 2FFF |

0х0002 5000 |

0х0002 7FFF |

D. |

0х0002 0000 |

0х0002 3FFF |

0х0002 6000 |

0х0002 7FFF |

Таблица 5.4. Диапазон адресов для команд и данных в ADSP21062

Чтобы определить начальный адрес 32 разрядных данных, используются следующие уравнения (для ADSP 21062 и ADSP 21061):

145

5 Память

i Начальный адрес для 32 разрядных данных 0 B + 4K + m + 1

1 B + 8K + m + 1

2 B + 16K + m + 1

3B + 20K + m + 1

B = начальный адрес блока памяти

n = число ячеек 48 разрядных командных слов i = целая часть от [(n 1) ё 4096]

m = (n 1) mod 4096

5.3.4. Короткие 16-разрядные слова

Адресация нормальных слов используется при обращении к 32 разрядным или 48 разрядным словам. Все выборки команд и обращение к 32 разрядным данным выполняются по адресам нормальных слов. Адреса коротких слов могут использоваться при обращении к 16 разрядным данным. Возможность адресации коротких слов позволяет увеличить количество 16 разрядных данных, которые могут храниться во внутренней памяти, а также позволяет адресовать старшее слово (MSW) и младшее слово (LSW) 32 разрядных данных. Выбор между MSW и LSW осуществляет нулевой разряд адреса.

К одному участку в памяти (т. е. 16 младшим битам 32 разрядного слова) можно обратиться двумя способами: с помощью адресации нормальных слов или

Рис. 5.11. Адреса коротких слов

146

Память 5

адресации коротких слов. Адрес короткого слова является сдвинутым влево адресом нормального слова. Это упрощает преобразование между адресацией коротких слов и адресацией нормальных слов для одной и той же физической ячейки памяти. На рис. 5.11 показано, как адреса коротких слов соотносятся с адресами нормальных слов для 32 разрядных слов. Заметим, что 16 разрядные слова передаются по линиями 31 16 внутренних шин РМD и DMD, а также внешней шины (DATA47 0).

При арифметическом сдвиге адреса короткого слова вправо на один бит получается соответствующий адрес нормального слова. При арифметическом сдвиге адреса нормального слова влево получается адрес короткого слова для LSW 32 разрядных данных. Для получения адреса короткого слова для MSW после выполнения сдвига влево надо бит 0 установить в 1.

При считывании 16 разрядных коротких слов в регистрах ADSP 2106x слова автоматически расширяются до 32 разрядных чисел. 16 старших разрядов заполняются нулями или дополняются по знаку. Это определяется значением бита SSE в регистре MODE1. Если SSE=0, то 16 старших разрядов заполняются нулями. Если SSE=1, то 16 старших разрядов дополняются по знаку (исключением является считывание короткого слова из регистра PX – в этом случае старшие разряды всегда заполняются нулями).

5.3.5. Более тонкая структура расположения в памяти смешанных 32разрядных и 48-разрядных слов

Если смешанные 48 разрядные команды и 32 разрядные данные должны располагаться в памяти отличающимся от описанных выше основных комбинаций способом, то требуется глубокое понимание структуры внутренней памяти ADSP 2106x. В следующих разделах подробно описывается низкоуровневая организация и адресация блоков внутренней памяти.

5.3.5.1. Низкоуровневое физическое отображение блоков памяти

Каждый блок памяти состоит из 16 столбцов. В ADSP 21060 каждый столбец содержит 8 К 16 разрядных слов; в ADSP 21062 каждый столбец содержит 4 К 16 разрядных слов. При чтении или записи 16 разрядных слов 13 младших бит адреса определяют строку в каждом столбце. Старшие разряды адреса определяют столбец. При чтении или записи 16 разрядных слов адрес сдвигается вправо на один бит перед обращением к памяти (см. рис. 5.12). Это дает возможность использовать нулевой бит для выбора между MSW и LSW 32 разрядных слов.

Какие именно и сколько будет выбрано столбцов при обращении к памяти, зависит от разрядности слова, к которому осуществляется обращение. Для 48

147

5 Память

31 |

24 |

17 16 15 |

|

|

0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1110 |

0001 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выбор |

Сдвиг вправо |

|

|

блока |

|

Адрес короткого слова

15 |

13 12 |

|

|

0 |

|||

|

|

|

|

|

|

|

|

|

|

Адрес |

|

Адрес строки |

|

||

|

|

столбца |

|

|

|||

|

|

|

|

|

|

|

|

Физический адрес, используемый в блоке памяти

Выбор старшее/младшее 16-разрядное слово (MSW/LSW)

Рис. 5.12. Предварительная обработка адреса 16-разрядного слова

разрядных слов 16 разрядные столбцы выбираются группами по три, причем биты 13 15 адреса определяют, какая группа выбрана. Для 32 разрядных слов 16 разрядные столбцы выбираются группами по два, и биты 13 15 адреса также определяют, какая группа выбрана.

Обращение к 16 разрядному короткому слову обрабатывается несколько отличным способом для того, чтобы обеспечить легкий доступ к MSW и LSW 32 разрядного слова. В генераторе адреса данных ADSP 2106x выполняется арифметический сдвиг вправо адреса короткого слова, что дает физический адрес 32 разрядного записываемого слова. Если сдвинутый за границу слова бит равен нулю, то происходит обращение к LSW, иначе к MSW. Для получения адреса выполняется следующее: сначала выбирается группа из двух столбцов с помощью бит 13 15 адреса, затем в зависимости от значения сдвинутого за границу слова бита, получившегося после сдвига вправо адреса короткого слова, выбирается один из столбцов.

5.3.5.2. Ограничения при размещении смешанных 32-разрядных и 48разрядных слов

32 разрядные и 48 разрядные слова сгруппированы внутри блока памяти по разному и пытаются использовать одну и ту же область адресов. Из за этого могут возникать ошибки при смешивании 48 разрядных команд и 32 разрядных данных внутри одного и того же блока (т. к. 32 разрядные и 16 разрядные слова

148

Память 5

используют одинаковую структуру группировки и различные адреса, они могут свободно смешиваться внутри блока памяти). Общим правилом для размещения слов различного размера является то, что все 48 разрядные команды должны находиться по адресам младше, чем все 32 разрядные данные. Это ограничение необходимо, чтобы исключить перекрытие адресов для команд и данных.

На рис. 5.13 показано, как 48 разрядные слова заполняют блок памяти, и где точно могут располагаться 32 разрядные слова в ADSP 21060. На рис. 5.14 приведена подобная информация для ADSP 21062. Если n – число 48 разрядных слов, которые нужно разместить, В – начальный адрес блока, то адрес, где могут располагаться смежные 32 разрядные данные, может быть определен по табл. 5.5:

(n 1)+8192 Начальный адрес для смежных |

Диапазон несмежных адресов блока |

|

|

адресов 32 разрядных данных |

памяти |

0 |

B + 8K + m + 1 |

от (B + n) до (8К 1) |

1 |

B + 16K + m + 1 |

|

2 |

B + 32K + m + 1 |

от (B + 24К + n) до (32К 1) |

3 |

B + 40K + m + 1 |

|

4 |

B + 56K + m + 1 |

от (B + 48К + n) до (56К 1) |

m=(n 1) mod 8192

Таблица 5.5. Начальные адреса для смежных адресов 32разрядных данных в ADSP-21060

На рис. 5.13 показано, что когда для 48 разрядных слов выделяется нечетное число групп по 3 столбца (т. е. одна, три или пять 3 столбцовых групп), то будет существовать доступный для использования, но несмежный блок 32 разрядной памяти. Это также показано в табл. 5.5.

Для полного использования всего блока памяти 48 разрядные слова должны размещаться в объеме 16 Кслов (т. е. в шести столбцах). Даже когда вся память используется, будет существовать диапазон адресов между областью 48 разрядных слов и областью смежных 32 разрядных слов, по которым нельзя размещать истинные данные. Любая запись 48 разрядных слов в эту область разрушит 32 разрядные данные, а любая запись 32 разрядных слов разрушит 48 разрядные слова данных.

Однако чтобы точно определить, какой адрес является истинным, снова требуется провести анализ расположения данных в памяти. Самое простое решение – представить, что 16 разрядные слова отображаются в пространство 32 разрядных слов, а затем уже распределять память методом, описанным выше для 32 разрядных слов.

149

5 Память

Рис. 5.13. Смешивание 48-разрядных и 32-разрядных слов в блоке памяти в ADSP-21060

150