Режимы адресации микропроцессора.

Режим адресации |

Формат операнда |

Регистр сегмента |

регистровый |

регистр |

Не используется |

непосредственный |

данное |

Не используется |

прямой |

Сдвиг Метка |

DS DS |

Косвенный регистровый |

[BX] [BP] [DI] [SI] |

DS SS DS DS |

По базе |

[BX]+ сдвиг [BP]+ сдвиг |

DS CS |

Прямой с индексированием |

[DI]+ сдвиг [SI]+ сдвиг |

DS DS |

По базе с индексированием |

[BX][SI]+сдвиг [BX][DI]+ сдвиг [BP][SI]+ сдвиг [BP][DI]+ сдвиг |

DS DS SS SS |

В таблице приведены форматы операндов языка Ассемблер для всех семи режимов адресации, реализуемых процессором, и для каждого формата указано, какой из регистров сегмента используется для вычисления физиологического адреса. Обратите внимание, что во всех режимах предполагается доступ к сегменту данных ( т.е. регистром сегмента служит регистр DS), и только в тех случаях, когда используется регистр BP, предполагается доступ к сегменту стека (т.е. регистром сегмента служит регистр SS).

Режимы адресации памяти.

название |

Краткое описание |

Исполнительный адрес |

Смещение, которое вычисляется операционным блоком для доступа к находящемуся в памяти операнду. Исполнительный адрес показывает, на каком расстоянии (в байтах) располагается операнд от начала сегмента, в котором он находится. |

Прямая адресация |

Исполнительный адрес является составной часть команды. Микропроцессор добавляет этот исполнительный адрес к сдвинутому содержимому регистра сегмента данных DS и получает 20-битовой физический адрес операнда. |

Косвенная регистровая адресация |

Исполнительный адрес операнда содержится в базовом регистре ВХ, регистре указателя базы ВР или индексном регистре (SI или DI). Косвенные регистровые операнды надо заключать в квадратные скобки, чтобы отличить их от регистровых операндов. |

Адресация по базе |

Ассемблер вычисляет исполнительный адрес с помощью сложения значения сдвига с содержимым регистров ВХ или ВР. |

Прямая адресация с индексированием |

Исполнительный адрес вычисляется как сумма значений сдвига и индексирования регистра (DI или DS). Этот тип адресации удобен для доступа к элементам таблицы, когда сдвиг указывает на начало таблицы, а индексный регистр – на ее элемент. |

Адресация по базе с индексированием |

Исполнительный адрес вычисляется как сумма значений базового регистра, индексного регистра и, возможно, сдвига. |

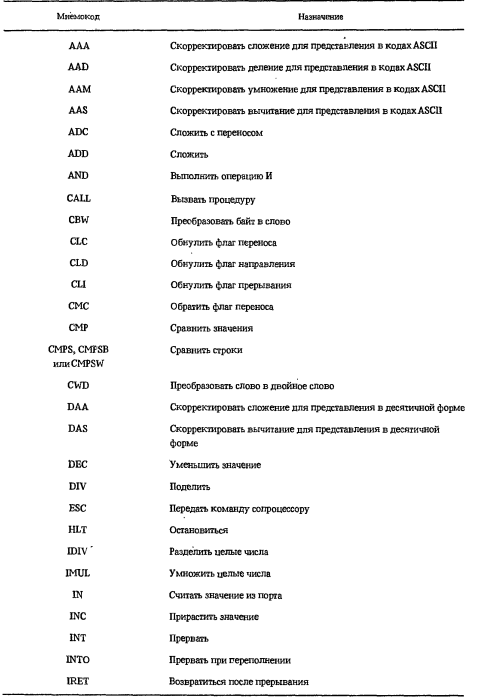

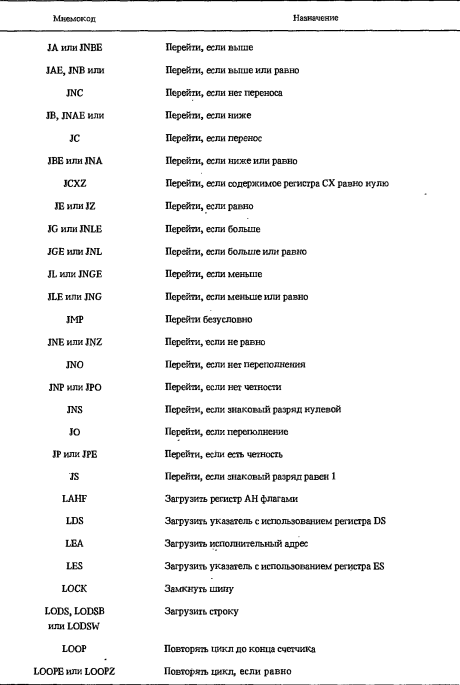

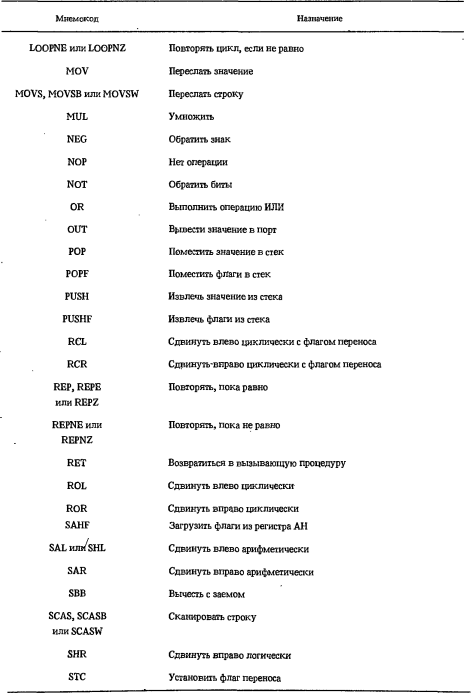

Система команд процессора Intel 80286.

PDP-11.

Первые машины семейства PDP-11 появились в начале 70-х годов.

Форматы команд и данных.

Архитектура миникомпьютеров семейства DEC PDP-11 кратко можно охарактеризовать как 16-битную, с многорегистровой схемой процессора, переменной длинной команд и единой магистралью. Важнейшей особенностью архитектуры PDP-11 является всестороннее развитие системы адресации и использование стекового механизма при обращениях к подпрограммам и при обслуживании прерываний.

Основная единица представления данных и управляющей информации в машинах PDP-11 – 16-битное слово, но наряду с этим процессор может выполнять операции с байтами, а команды могут состоять как из одного, так и из двух, а также из трех 16-битных слов. Второе и третье слова команды – это либо адреса, либо непосредственно заданные значения операндов. Таким образом, 16-битное слово интерпретируется процессором или как команда, или как адрес, или как значение операнда, которое в свою очередь может быть двоичным числом без знака, двоичным числом со знаком в дополнительном коде, булевским вектором и парой байтов. Кроме того, возможны специальные интерпретации, например, слово состояния процессора.

Ядро процессора PDP-11 является массив, состоящий из восьми 16-битных регистров общего назначения, пронумерованных, начиная с нуля: R0, R1,R2, …, R7.содержимое каждого из этих регистров может быть использовано как значения операнда, или как адрес ячейки главной памяти. Выбором способа адресации имеется возможность производить операции над содержимым как регистров, так и ячеек главной памяти с запоминанием результата либо в регистре, либо в ячейке. Другими словами, любая команда пересылки или преобразования данных в зависимости от используемой адресации может быть выполнена в любой из четырех возможных ее разновидностей: регистр-регистр, регистр-память, память –регистр, память-память. Указание операнда в основном командном слове осуществляется 6-битными полями адресации. В таком поле 3 младших бита определяют способ адресации.

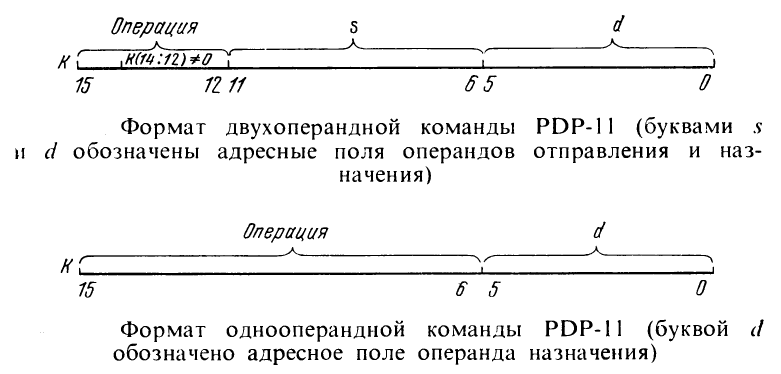

Имеются двухоперандные однооперандные команды преобразования и тестирования данных.