- •Содержание

- •Реферат

- •Введение

- •Постановка задачи

- •Операционный автомат

- •Объединенная граф схема алгоритма

- •2. Проектирование операционного автомата

- •3. Проектирование управляющего автомата

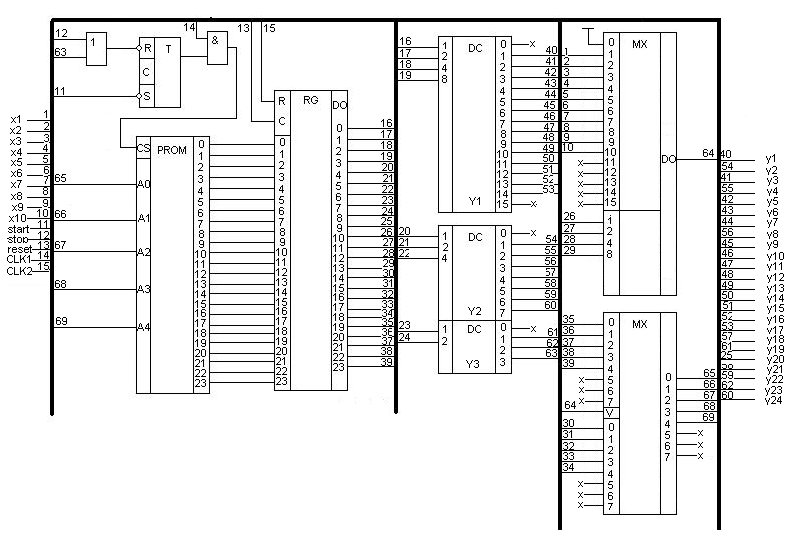

- •4. Проектирование процессорного модуля

- •4.1 Схема объединения операционного и управляющего автоматов

- •4.2 Результаты тестирования

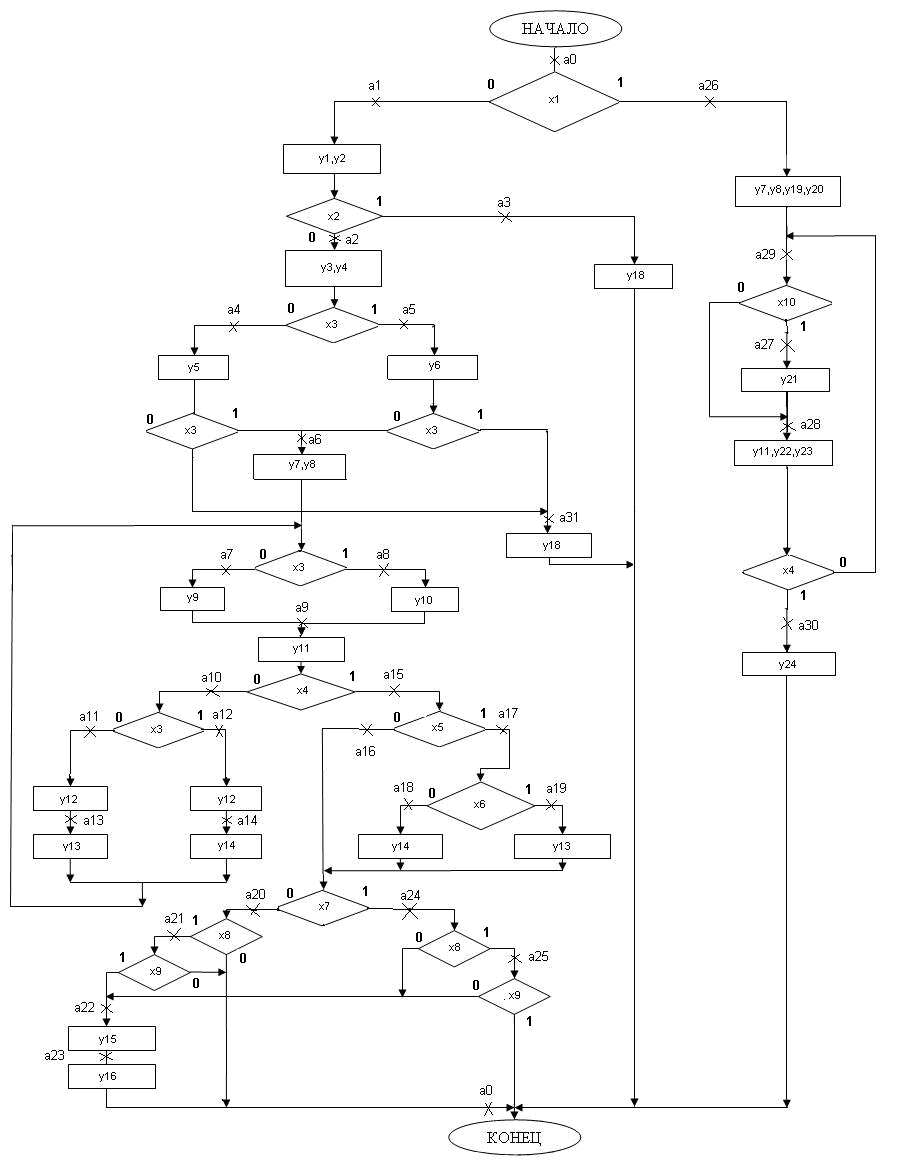

3. Проектирование управляющего автомата

Рис. 3.1 – Размеченная ГСА для П-автомата с принудительной адресацией

1) Таблица 3.1 - Матрица совместимости S

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

2 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

3 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

4 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

5 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

6 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

8 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

9 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

10 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

11 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

12 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

13 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

14 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

15 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

17 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

18 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

19 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

20 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

21 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

22 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

23 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

24 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

2) Нахождение матрицы включения:

Таблица 3.2 - Матрица включения R

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

Y1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

Y2 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

Y3 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

Y4 |

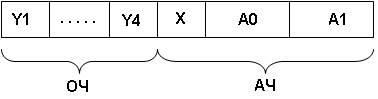

![]()

![]()

Рис. 3.2 – Структура микрокоманды

3) Таблица 3.3 - Кодирование микроопераций

Y1 |

K(Y1) |

Y2 |

K(Y2) |

Y3 |

K(Y3) |

X |

K(X) |

y1 |

0001 |

y2 |

001 |

y19 |

01 |

x1 |

0001 |

y3 |

0010 |

y4 |

010 |

y23 |

10 |

x2 |

0010 |

y5 |

0011 |

y8 |

011 |

yF |

11 |

x3 |

0011 |

y6 |

0100 |

y18 |

100 |

|

|

x4 |

0100 |

y7 |

0101 |

y21 |

101 |

|

|

x5 |

0101 |

y9 |

0110 |

y22 |

110 |

|

|

x6 |

0110 |

y10 |

0111 |

y24 |

111 |

|

|

x7 |

0111 |

y11 |

1000 |

|

|

|

|

x8 |

1000 |

y12 |

1001 |

|

|

|

|

x9 |

1001 |

y13 |

1010 |

|

|

|

|

x10 |

1010 |

y14 |

1011 |

|

|

|

|

|

|

y15 |

1100 |

|

|

|

|

|

|

y16 |

1101 |

|

|

|

|

|

|

y17 |

1110 |

|

|

|

|

|

|

4) Таблица 3.4 - Карта программирования памяти

|

Y1 |

Y2 |

Y3 |

Y4 |

X |

A0 |

A1 |

0 |

0000 |

000 |

00 |

0 |

0001 |

00001 |

11010 |

1 |

0001 |

001 |

00 |

0 |

0010 |

00010 |

00011 |

2 |

0010 |

010 |

00 |

0 |

0011 |

00100 |

00101 |

3 |

0000 |

000 |

00 |

0 |

0000 |

00000 |

00000 |

4 |

0011 |

000 |

00 |

0 |

0011 |

00110 |

11111 |

5 |

0100 |

000 |

00 |

0 |

0011 |

00110 |

11111 |

6 |

0101 |

011 |

00 |

0 |

0011 |

00111 |

01000 |

7 |

0110 |

000 |

00 |

0 |

0000 |

01001 |

01001 |

8 |

0111 |

000 |

00 |

0 |

0000 |

01001 |

01001 |

9 |

1000 |

000 |

00 |

0 |

0100 |

01010 |

01111 |

10 |

0000 |

000 |

00 |

0 |

0011 |

01011 |

01100 |

11 |

1001 |

000 |

00 |

0 |

0000 |

01101 |

01101 |

12 |

1001 |

000 |

00 |

0 |

0000 |

01110 |

01110 |

13 |

1010 |

000 |

00 |

0 |

0011 |

00111 |

01000 |

14 |

1011 |

000 |

00 |

0 |

0011 |

00111 |

01000 |

15 |

0000 |

000 |

00 |

0 |

0101 |

10000 |

10001 |

16 |

0000 |

000 |

00 |

0 |

0111 |

10100 |

11000 |

17 |

0000 |

000 |

00 |

0 |

0110 |

10010 |

10011 |

18 |

1011 |

000 |

00 |

0 |

0000 |

10000 |

10000 |

19 |

1010 |

000 |

00 |

0 |

0000 |

10000 |

10000 |

20 |

0000 |

000 |

00 |

0 |

1000 |

00000 |

10101 |

21 |

0000 |

000 |

00 |

0 |

1001 |

00000 |

10110 |

22 |

1100 |

000 |

00 |

0 |

0000 |

10111 |

10111 |

23 |

1101 |

000 |

00 |

0 |

0000 |

00000 |

00000 |

24 |

0000 |

000 |

00 |

0 |

1000 |

10110 |

11001 |

25 |

0000 |

000 |

00 |

0 |

1001 |

10110 |

00000 |

26 |

0101 |

011 |

01 |

1 |

1010 |

11100 |

11011 |

27 |

0000 |

101 |

00 |

0 |

0000 |

11100 |

11100 |

28 |

1000 |

110 |

10 |

0 |

0100 |

11101 |

11110 |

29 |

0000 |

000 |

00 |

0 |

1010 |

11100 |

11011 |

30 |

0000 |

111 |

00 |

0 |

0000 |

00000 |

00000 |

31 |

0000 |

000 |

00 |

0 |

0000 |

00000 |

00000 |

Рис. 3.3 - Структурная схема управляющего автомата