- •Содержание

- •Реферат

- •Введение

- •Постановка задачи

- •Операционный автомат

- •Объединенная граф схема алгоритма

- •2. Проектирование операционного автомата

- •3. Проектирование управляющего автомата

- •4. Проектирование процессорного модуля

- •4.1 Схема объединения операционного и управляющего автоматов

- •4.2 Результаты тестирования

Постановка задачи

В данном курсовом проекте необходимо разработать процессорный модуль на основе синтеза управляющего автомата и операционного автомата. Необходимо построить управляющий автомат П-автомат с принудительной адресацией и операционный автомат класса I для устройств деления целых двоичных знаковых чисел без восстановления остатка и умножения целых двоичных беззнаковых чисел.

Операционный автомат

Операционные автоматы, структура которых обеспечивает возможность одновременного выполнения всех функционально совместимых микроопераций при использовании минимального числа комбинационных схем, называют операционные автоматы класса I.

Операционный автомат осуществляют вычислительные действия над операндами. Структурно операционный автомат состоит из элементов памяти (регистров), осуществляющих хранение значений операндов, и комбинационных схем, отвечающих за выполнение микроопераций. Входной информацией для операционного автомата являются линии данных {D} и множество выполняемых в данном такте микроопераций {Y}, выходами являются линии результата {R} и выработанные признаки результата {X}, используемые в управляющем автомате.

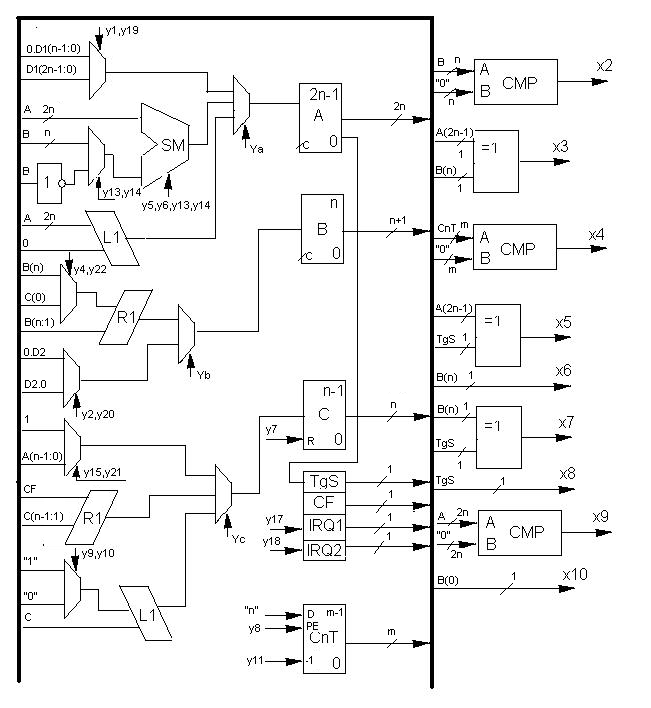

Структура операционного автомата класса I представлена на рис. 1.1.

Рис. 1.1 - Структура операционного автомата класса I.

1.2 Управляющий автомат типа П с принудительной адресацией

П-автомат строится на основе принципа микропрограммного управления, использующего операционно-адресную структуру управляющих слов, которые хранятся в памяти. Управляющее слово определяет порядок работы устройства в течение одного такта и называется микрокомандой. Микрокоманда содержит информацию о микрооперации, которая выполняется в текущем такте работы устройства, а также адрес следующей микрооперации (при принудительной адресации). Формат микрокоманды показан на рисунке 1.2

![]()

Рис. 1.2.1 – Формат микрокоманды при принудительной адресации

В поле Y содержится код микрооперации. Адрес следующей микрооперации зависит от кода, расположенного в поле X. Переход осуществляется либо по адресу, занесенному в А0, либо - в А1.

Рисунок 1.2.2 – Структура управляющего П-автомата с принудительной адресацией

Объединенная граф схема алгоритма

Рис 1.3 - Объединенная ГСА

2. Проектирование операционного автомата

1) Список операций:

y1: A(2n-1:0):=D1(2n-1:0)

y2: B(n:0):= D2(n-1:0).0

y3: TgS:= A(2n-1)

y4: B(n:0):=R1(B(n).B(n:1))

y5: A(2n-1:n-1):=A(2n-1:n-1)+B(n:0)+1

y6: A(2n-1:n-1):=A(2n-1:n-1)+B(n:0)

y7: C(n-1:0):=0

y8: CnT(m-1:0):=n

y9: C(n-1:0):=L1(C(n-1:0).1)

y10: C(n-1:0):=L1(C(n-1:0).0)

y11: CnT:=CnT-1

y 12:

A:=L1(A.0)

12:

A:=L1(A.0)

y13: A:=A+B+1

y14: A:=A+B

y15: C(n-1:0):=C(n-1:0)+1

y16: R(2n-1:0):=0000000.C(n-1:0)

y17: IRQ1:=1

y18: IRQ2:=1

y19: A(2n-1:0):=0.D1(n-1 :0)

y20: B(n:0):=0.D2

y21: C(n-1:0):=C(n-1:0)+A(n-1:0)

y22: B(n-1:0):=R1(C(0).B(n-1:1))

y23: C(n-1:0):=R1(CF.C(n-1:1))

y24: R(2n-1:0):=C(n-1:0).B(n-1:0)

x1: F=1

x2: B=0

x3: A(2n-1) ÅB(n)

x4: CnT=0

x5: A(2n-1)ÅTgS

x6: B(n)

x7: f3=B(n) ÅTgS

x8: TgS

x9: A=0

x10: B(0)

2) A(2n-1:0), B(n:0), C(n-1), CnT(m-1:0), TgS, R(2n-1:0), IRQ1,IRQ2

3) YA = {y1, y5, y6, y12, y13, y14, y19};

YB = {y2, y4, y20, y22} ;

YC = {y7, y9, y10, y15, y21, y23} ;

YCnT = {y8, y11} ;

YTgS = {y3} ;

YR = {y16, y24} ;

YIRQ1 = {y17} ;

YIRQ2 = {y18}

4) KA1 = {y1, y19} ; KA2 = {y5,y6} ; KA3 = {y13, y14} ; KB1 = {y2, y20} ;

KB2 ={y4,y22} ; KC1 = {y9, y10} ; KC2 = {y15,y21}

5)

A:= F1,

где

A:= F1,

где

А:=

A+F2+F3,

где

А:=

A+F2+F3,

где

B:=

F4,

где

B:=

F4,

где

B:=

R1(F5.B(n:1)),

где

B:=

R1(F5.B(n:1)),

где

C:=

L1(C.F6),

где

C:=

L1(C.F6),

где

С:=

C+F7,

где

С:=

C+F7,

где

Рис. 2.1 – Структурная схема операционного автомата I