- •Лабораторная работа №3 Изучение триггеров

- •1. Краткие теоретические сведения.

- •1.2 Классификация триггеров.

- •2. Триггеры.

- •2.1.2 Создание принципиальной схемы

- •2.2 Синхронный rs-триггер

- •2.3 Универсальный jk-триггер.

- •3. Реализация схем, используя vhdl-программу, на примере d-триггера.

- •3.Задание к работе

- •Контрольные вопросы

2.2 Синхронный rs-триггер

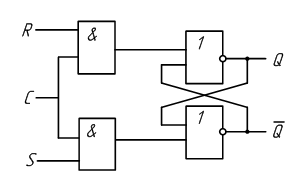

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс, то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера изображена на рис.10.

Рис. 10. Схема синхронного RS-триггера

Таблица 4 - Таблица переходов синхронного RS-триггера

R (S) |

S |

Q(t) |

Q(t+1) |

Пояснения |

0 |

0 |

0 |

0 |

Режим сохранения информации R=S=0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

Режим установки нуля R=1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

1 |

1 |

1 |

* |

Под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние. При С=0 триггер отключен от управляющих S и R входов и находится в режиме хранения ранее полученной информации. При С=1 схема функционирует как обычный RS-триггер.

Характерной особенностью схемы является то, что в течение всего отрезка времени, когда синхросигнал равен 1, как сами потенциалы на управляющих S и R входах, так и любые их изменения тут же передаются на выход.

По аналогии с RS-триггером проверяем работоспособность синхронного RS-триггера. Для примера воспользуемся теми же параметрами входных информационных сигналов, какие были в примере работоспособности RS-триггера, а для сигнала синхронизации зададим следующие данные (рис.11).

Рис. 11. Параметры синхронизирующего сигнала.

2.3 Универсальный jk-триггер.

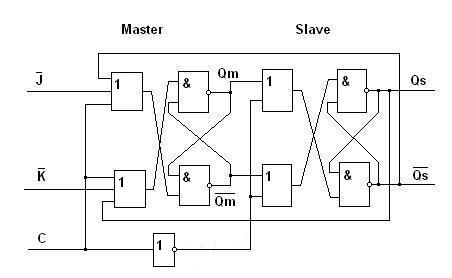

Универсальный JK-триггер, схема которого (рис.12) представляет собой двухступенчатый синхронный триггер. Как видно из рисунка, JK-триггер состоит из двух асинхронных RS-триггеров с инверсными входами и двух КЦУ, каждое из которых содержит две схемы И-НЕ с тремя входами каждая.

Закон функционирования JK-триггера задается (табл. 4). JK-триггер отличается от синхронного RS-триггера тем, что не имеет запрещенных комбинаций сигналов на входах J и К. Кроме того, при J=1 и K=1 триггер изменяет свое состояние на противоположное, т. е. работает как триггер со счетным входом (T-триггер).

Таблица 4 – Таблица переходов JK триггера

Сt |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

Jt |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

Kt |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

Qt |

Qt |

Qt |

Qt |

Qt |

Qt |

Qt |

Qt |

Qt |

Рис. 12 - Структура схема универсального JK-триггера

При С=0 входы J и К заблокированы и, следовательно, оказываются заблокированными входы S и R ведущего триггера 1. При С=1 в соответствии с информационными сигналами на входах J и К устанавливается состояние ведущего триггера. При этом на входы S и R ведомого триггера 2 поступают сигналы, при которых его предыдущее состояние сохраняется. При С=0, когда входы триггера 1 закрыты для входной информации, входы триггера 2 открываются и состояние ведущего триггера воспринимается ведомым триггером. В качестве запускающего импульса используем R, представляющий собой импульс небольшой длительности. Графическое обозначение JK-триггера (рис.13).

Рис. 13. Графическое обозначение JK-триггера.

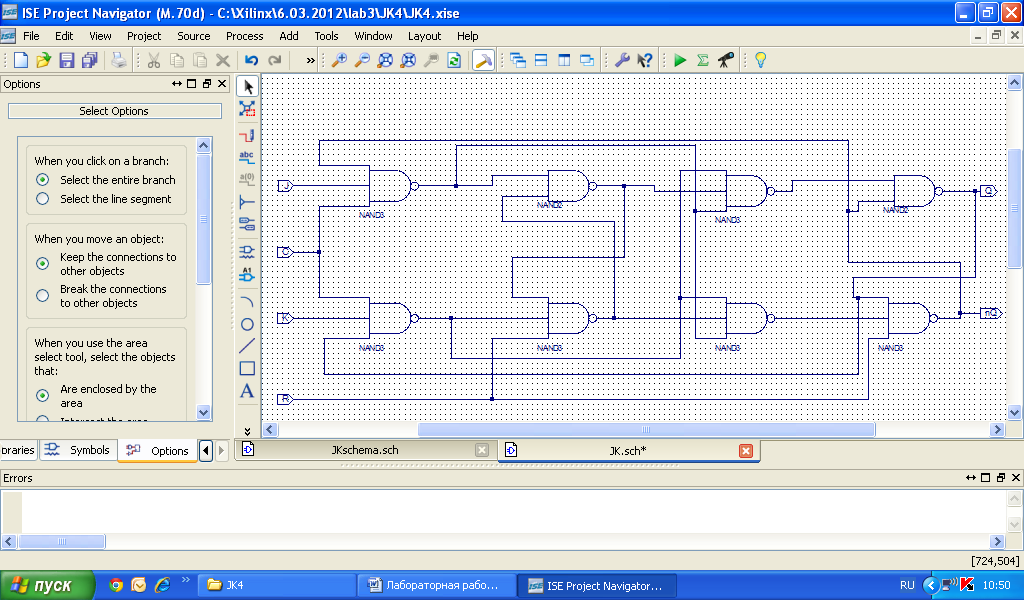

Нарисуем принципиальную схему триггера (рис. 14).

Рис.14

Принципиальная схема JK-триггера.

Рис.14

Принципиальная схема JK-триггера.

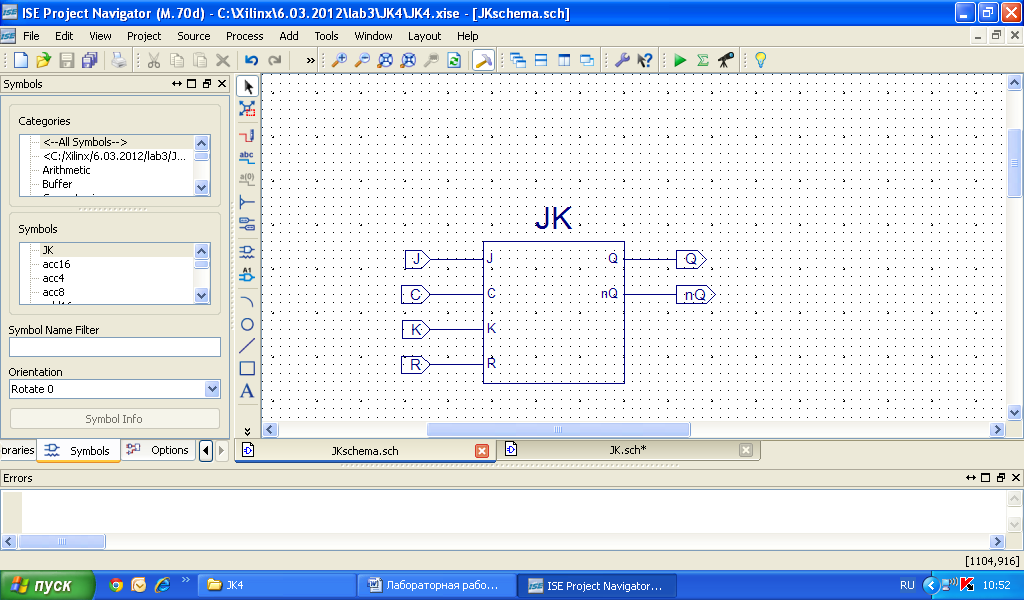

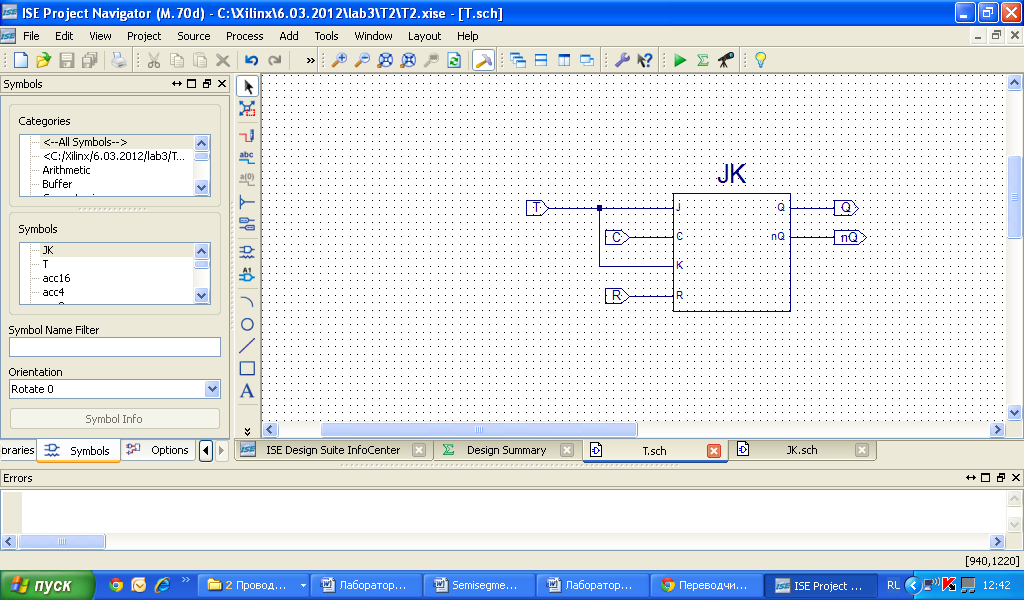

Создаем отдельный элемент JK-триггер (рис. 15).

Рис.15. Элемент JK-триггер.

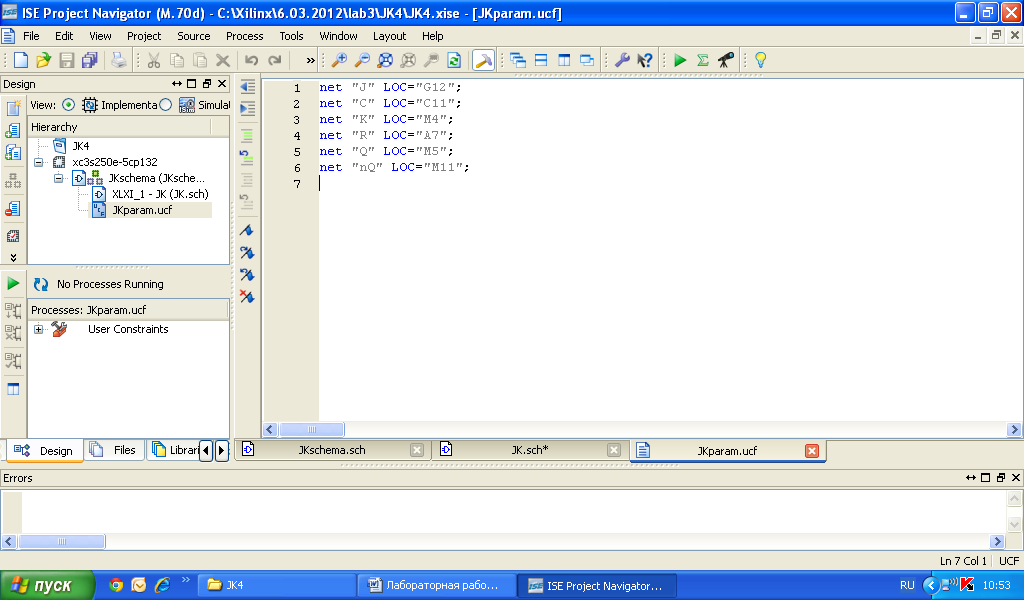

Осталось создать файл param с расширением *.ucf. В нём опишем привязку выводов проекта к входам-выводам кристалла. Пропишем в нём следующие строки (рис.16).

Рис.16

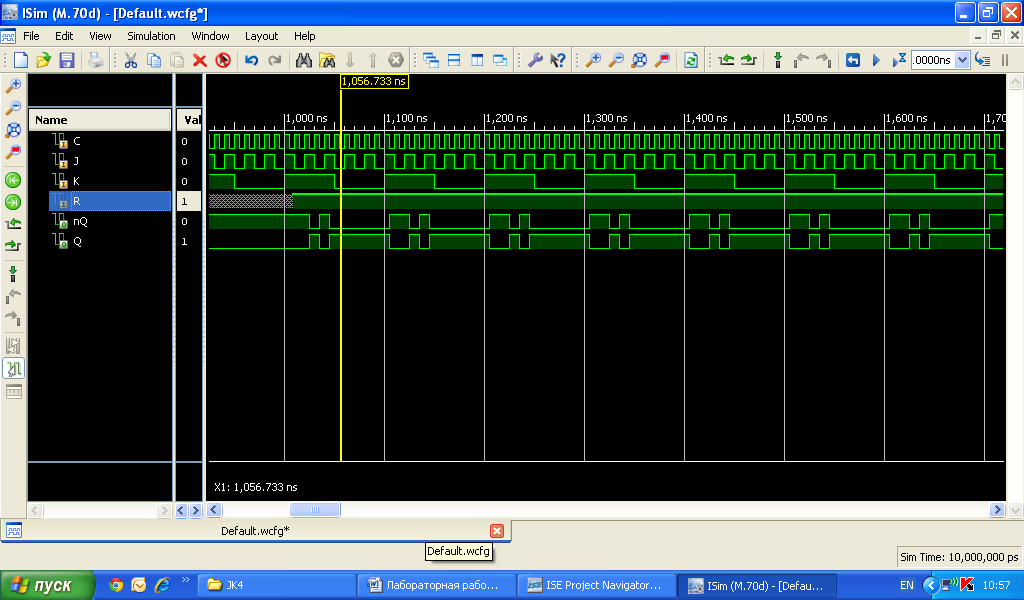

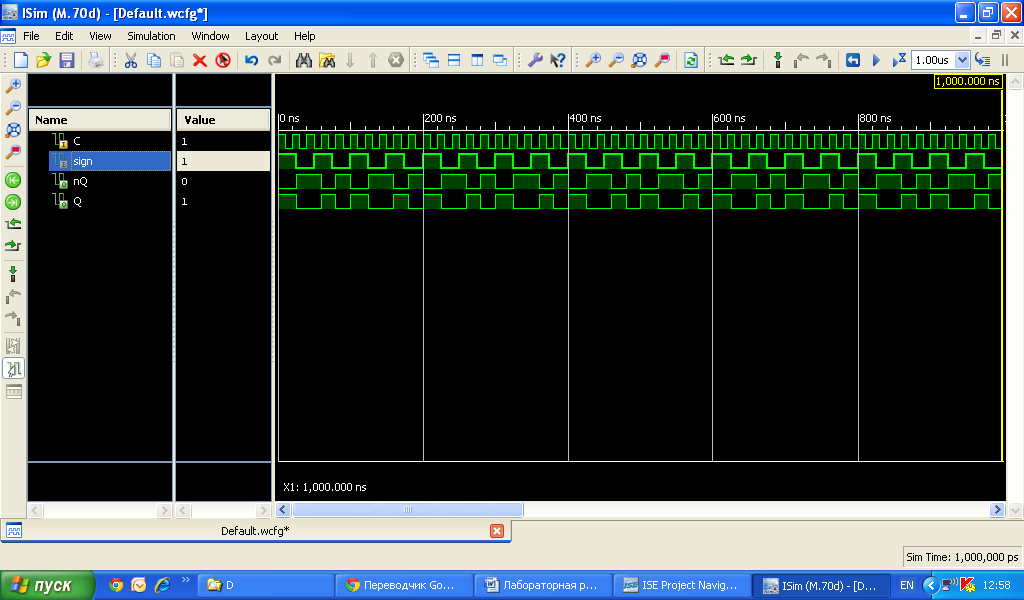

Дальнейший шаг – проверка работоспособности схемы, для этого производим симулирование. Для входных сигналов вводим исходные значения и получаем результат в виде графиков (рис.17).

Рис.17. Симулирование работы схемы

2.4 Т-триггер.

T-триггеры, или триггеры со счетным входом, могут быть получены из JK-триггера при соединении обоих информационных входов J и K. и подаче на них уровня 1. Функционирование T-триггера описывается (табл. 5) В качестве счетного входа T используется вход С. При подаче сигнала на вход T-триггер будет переключаться в состояние, противоположное предыдущему. JK-триггер в таком режиме выполняет функцию T-триггера.

Таблица 5 – Таблица переходов Т триггера

Сt |

Jt |

Kt |

Qt |

Qt+1 |

0 |

1 |

1 |

Qt |

Qt |

1 |

1 |

1 |

Qt |

|

Рис. 18 - Построение Т-триггера на базе JK-триггера.

Следует заметить, что уровень 1 для входов J и К (входов элементов И-НЕ) является пассивным сигналом. Поэтому для получения T-триггера из JK-триггера можно не предусматривать входы J и К в схеме.

После создания элемента, как и в предыдущих случаях, следует проверить его работоспособность, а также написать VHDL-программу, в тексте программы вместо сигналов J и K указывается один сигнал Т, который при симуляции будут иметь вид единичного сигнала.

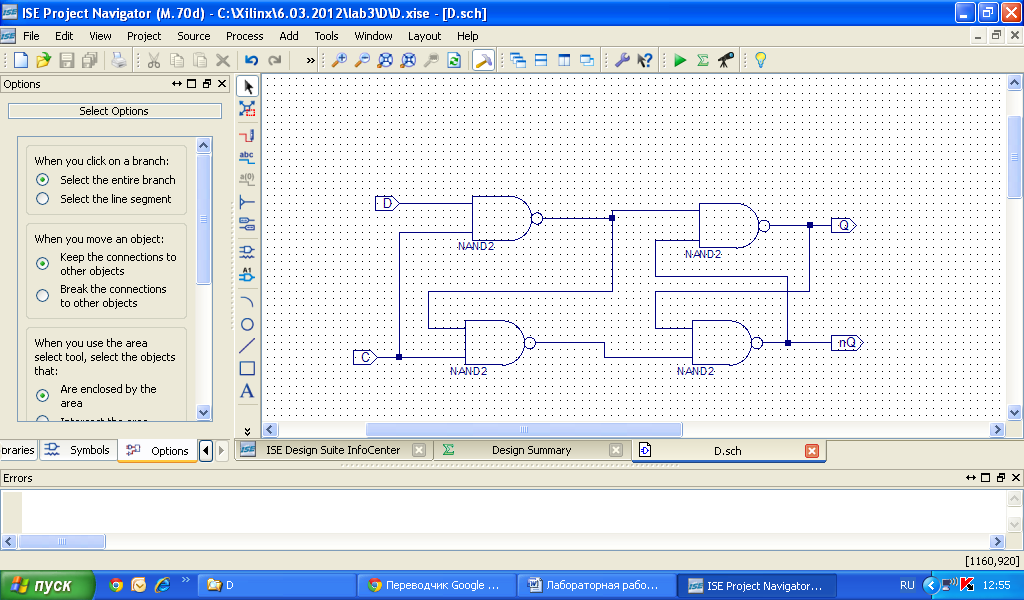

2.5 D – триггер

D-триггер имеет 1 информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход С).

Рис. 19 - Схема D-триггера на основе RS-триггера

Создаем схему, изображенную на рис. 19. Проверяем работоспособность данной схемы (рис.20), результаты сравниваем с таблицей истинности для D-триггера (Табл. 6).

Таблица 6 - Таблица переходов D-триггера

C |

D |

Q(t) |

Q(t+1) |

Пояснения |

0 |

* |

0 |

0 |

Режим хранение информации |

0 |

* |

1 |

1 |

|

1 |

0 |

* |

0 |

Режим записи информации |

1 |

1 |

* |

1 |

Рис. 20. Результат проверки работы D-триггера.