2.3.1. Коммутация в процессорных матрицах

Коммутационные (соединительные) сети в вычислительной технике стали использоваться сравнительно недавно - вместе с появлением параллельных ЭВМ. Помимо соединений процессор - память, сети коммутации применяются для соединений процессор - процессор. В общем случае сеть имеет М входов и L выходов и состоит из групп коммутационных элементов и линий связи между ними. Соединительные возможности сетей могут быть разными: в одной сети они ограничиваются несколькими вариантами коммутации входов с выходами, в других - представляют произвольные варианты соединений для передачи данных.

При малом числе соединяемых устройств коммутация (соединение) не представляет больших трудностей и может быть обеспечена различными способами. Однако при большом числе устройств, а их в современных вычислительных системах может быть несколько тысяч, организация необходимых связей между ними представляет серьезную проблему и требует тщательных решений.

В архитектуре параллельных вычислительных систем коммутационным сетям отводится одно из центральных мест. По своей сложности, стоимости и влиянию на основные характеристики параллельных систем они выступают наравне с такими основными компонентами, как устройства памяти и процессоры.

Выделяют три класса устройств, используемых для коммуникации в параллельных системах, которые могут быть применены и для упорядочения данных в параллельной памяти:

1) p-мерные конвейерные соединители;

2) матричные коммутаторы:

3) многоярусные сети (они являются более перспективными для упорядочения данных в параллельной памяти).

1) p-мерные конвейерные соединители.

В конвейерном соединителе p-мерная структура узлов связывается в каждом измерении таким образом, чтобы обеспечивалась последовательная конвейерная передача данных между ними. Продвижение данных происходит, как правило, синхронно. При передаче данных в 1-м измерении от узла i к узлу i+v данные последовательно проходят через все i+v-1 узлов.

Каждый узел конвейерного соединителя должен содержать элементы памяти, обеспечивающие временное хранение данных. В простейшем случае это просто триггер со схемами занесения, в более сложных системах - многорегистровая буферная намять.

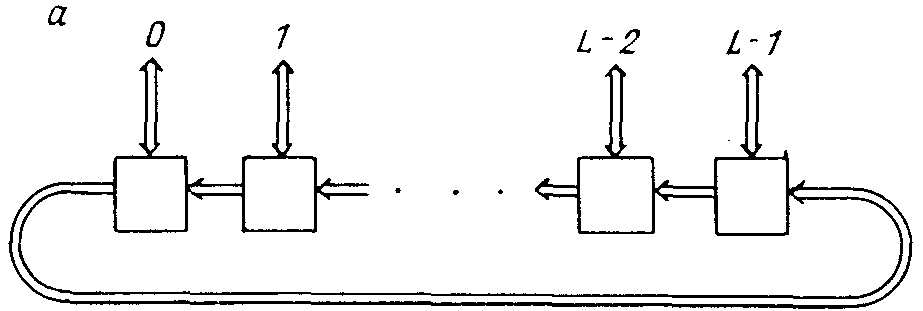

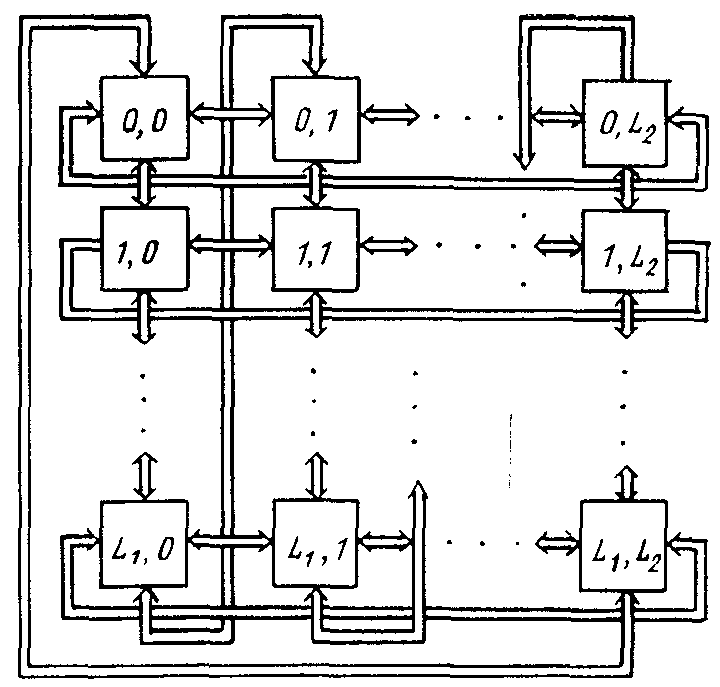

Примером одномерного конвейерного соединителя могут служить соединительная сеть мультипроцессора «ZMOB» и «Кембриджское кольцо», а двухмерного—система связи в матрице процессорных элементов вычислительной системы «ILLIAC-IV». Соответствующие структурные схемы приведены на рис. 1.

Рис. 1. Структуры одномерного (а) и двухмерного (6) конвейерных соединителей

К достоинствам конвейерных соединителей можно отнести их простоту и регулярность, к существенным недостаткам - зависимость времени передачи данных от расстояния между узлами. Так, например, в системе ZMOB это время колеблется от 100 нс до 25.6 мкс. Кроме того, существуют проблемы с обеспечением надежности таких структур, так как сбой в одном узле может привести к искажению множества сообщений.

Рассматривая применимость p-мерных конвейерных структур для упорядочения данных в параллельной памяти, можно отметить, что они достаточно просто позволяют производить необходимые перестановки данных в тех случаях, когда при формировании запоминающей среды используются линейные периодические размещения. Известно, что соответствующие таблицы размещения строятся с использованием линейных сдвигов, которые и составляют основу алгоритмов упорядочения данных. Однако при этом приходится считаться с отмеченной выше зависимостью времени сдвига (упорядочения данных) от величины сдвига. В памяти это приводит к зависимости времени доступа от вида обращения, что нежелательно. Дополнительные трудности возникают, когда число модулей памяти в многоблочной запоминающей среде больше ширины доступа (M>L). В таком случае, приходится решать задачу маскирования «лишних» узлов конвейерного соединителя.