Министерство высшего и среднего специального образования РФ

Санкт – Петербургский

Государственный электротехнический университет

Кафедра МО ЭВМ

Дисциплина:

Архитектура вычислительных систем и сетей ЭВМ

Тема: «Соединительные сети: сети Бенеша, Омега-сети,

сети типа n-Куб и другие»

Преподаватель: Горячев Г.А.

Санкт - Петербург

2004

Коммутационные (соединительные) сети в вычислительной технике стали использоваться сравнительно недавно - вместе с появлением параллельных ЭВМ. Помимо соединений процессор - память, сети коммутации применяются для соединений процессор - процессор. В общем случае сеть имеет М входов и L выходов и состоит из групп коммутационных элементов и линий связи между ними. Соединительные возможности сетей могут быть разными: в одной сети они ограничиваются несколькими вариантами коммутации входов с выходами, в других - представляют произвольные варианты соединений для передачи данных.

При малом числе соединяемых устройств коммутация (соединение) не представляет больших трудностей и может быть обеспечена различными способами. Однако при большом числе устройств, а их в современных вычислительных системах может быть несколько тысяч, организация необходимых связей между ними представляет серьезную проблему и требует тщательных решений.

В архитектуре параллельных вычислительных систем коммутационным сетям отводится одно из центральных мест. По своей сложности, стоимости и влиянию на основные характеристики параллельных систем они выступают наравне с такими основными компонентами, как устройства памяти и процессоры.

Выделяют три класса устройств, используемых для коммуникации в параллельных системах, которые могут быть применены и для упорядочения данных в параллельной памяти:

1) p-мерные конвейерные соединители;

2) матричные коммутаторы:

3) многоярусные сети (они являются более перспективными для упорядочения данных в параллельной памяти).

1) p-мерные конвейерные соединители.

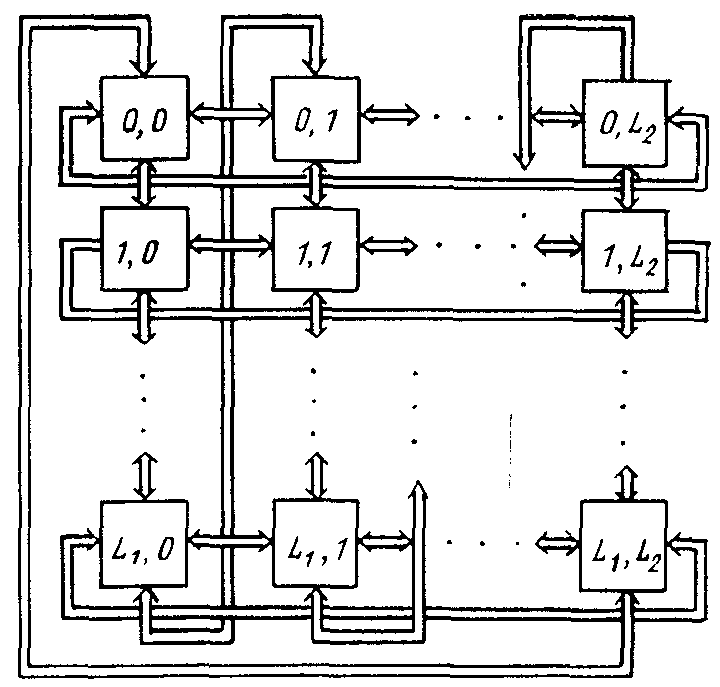

В конвейерном соединителе p-мерная структура узлов связывается в каждом измерении таким образом, чтобы обеспечивалась последовательная конвейерная передача данных между ними. Продвижение данных происходит, как правило, синхронно. При передаче данных в 1-м измерении от узла i к узлу i+v данные последовательно проходят через все i+v-1 узлов.

Каждый узел конвейерного соединителя должен содержать элементы памяти, обеспечивающие временное хранение данных. В простейшем случае это просто триггер со схемами занесения, в более сложных системах - многорегистровая буферная намять.

Примером одномерного конвейерного соединителя могут служить соединительная сеть мультипроцессора «ZMOB» и «Кембриджское кольцо», а двухмерного—система связи в матрице процессорных элементов вычислительной системы «ILLIAC-IV». Соответствующие структурные схемы приведены на рис. 1.

Рис. 1. Структуры одномерного (а) и двухмерного (6) конвейерных соединителей

К достоинствам конвейерных соединителей можно отнести их простоту и регулярность, к существенным недостаткам - зависимость времени передачи данных от расстояния между узлами. Так, например, в системе ZMOB это время колеблется от 100 нс до 25.6 мкс. Кроме того, существуют проблемы с обеспечением надежности таких структур, так как сбой в одном узле может привести к искажению множества сообщений.

Рассматривая применимость p-мерных конвейерных структур для упорядочения данных в параллельной памяти, можно отметить, что они достаточно просто позволяют производить необходимые перестановки данных в тех случаях, когда при формировании запоминающей среды используются линейные периодические размещения. Известно, что соответствующие таблицы размещения строятся с использованием линейных сдвигов, которые и составляют основу алгоритмов упорядочения данных. Однако при этом приходится считаться с отмеченной выше зависимостью времени сдвига (упорядочения данных) от величины сдвига. В памяти это приводит к зависимости времени доступа от вида обращения, что нежелательно. Дополнительные трудности возникают, когда число модулей памяти в многоблочной запоминающей среде больше ширины доступа (M>L). В таком случае, приходится решать задачу маскирования «лишних» узлов конвейерного соединителя.

2). Матричные коммутаторы

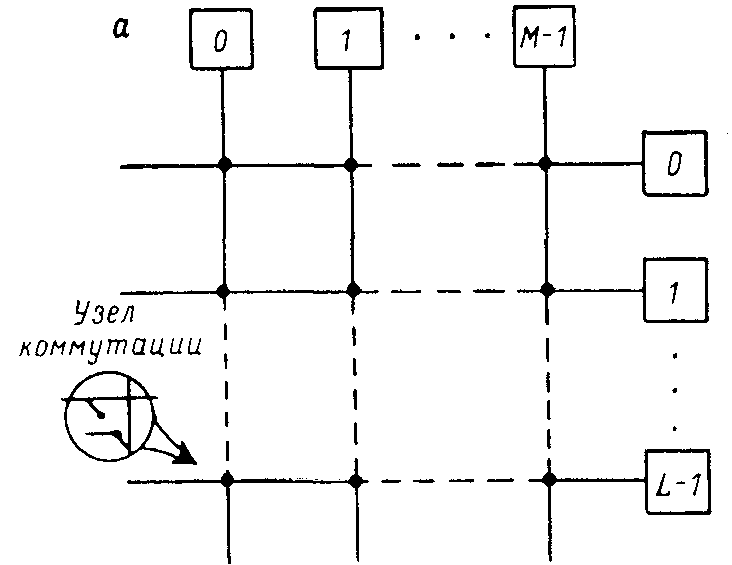

Матричные коммутаторы (crossbar network) являются одним из наиболее гибких типов соединительных сетей. Обобщенная структура матричного коммутатора, обеспечивающего соединение М на L портов, представлена на рис.2.

Сеть коммутации представляет собой множество связей между двумя наборами узлов, которые называются входами и выходами. Всего между M входами и L выходами существует ML раз личных связей, включая парные связи («один — одному»), связи «один—многим», смешанные связи.

Рис.3.

Варианты соединений в обобщенной

соединительной сети для M=3,

L=2:

a

— связи «ОДИН — МНОГИМ» ;

б,

в

— парные связи

Сеть, осуществляющая ML соединений, называется обобщенной соединительной сетью (рис. 3). Если сеть осуществляет только парные связи, она называется соединительной, в ней возможно M! соединений (рис. 3, б, в). В соединительных сетях любой допустимый набор связей (перестановка) выполняется за один такт и без конфликтов.

Организация матричного коммутатора такова, что при отсутствии конфликтов все необходимые связи обеспечиваются одновременно. Конфликты возникают, когда два или более абонента требуют коммутации одного и того же узла. Понятно, что в каждом узле необходимо разрешать возникающие конфликты. Поэтому узел коммутации может представлять собой достаточно сложную схему.

Одной из разновидностей матричного коммутатора является сеть, называемая «полное соединение» (complete connection). В ней для установления связи каждого из М портов с L портами используются собственные L линий связи (рис. 2,б). Легко заметить, что число узлов коммутации в этом случае остается прежним.

Так как число узлов коммутации растет пропорционально произведению ML, то стоимость матричных коммутационных сетей при большом количестве портов весьма высока. Однако при малом числе соединяемых блоков они эффективно используются, в частности, и для упорядочения данных в параллельной памяти.

3). Многоярусные коммутационные сети

Когда количество портов, соединяемых коммутационной сетью, исчисляется сотнями или тысячами, использование матричных коммутаторов не представляется возможным из-за их высокой сложности и стоимости. Не эффективными оказываются и конвейерные соединители, обладающие в этом случае весьма низким быстродействием. Решением проблемы является использование многоярусных коммутационных сетей. Многоярусные сети строятся из нескольких ярусов коммутационных элементов (КЭ). КЭ может сам представлять некоторую соединительную сеть, например матричный переключатель. Чаще всего на практике используются простые КЭ с двумя входами и двумя выходами.

Выделяют три основных вида многоярусных сетей: неблокируемые сети, перестраиваемые и блокируемые сети.

Неблокируемые сети.

Если коммутационная сеть находится в состоянии, при котором невозможно найти путь соединения определенного незанятого входного порта с незанятым выходным, то говорят, что эта сеть заблокирована. Неблокируемыми, следовательно, называются такие сети, в которых всегда можно найти путь соединения для свободной пары портов.

Неблокируемые структуры получаются путем введения дополнительных ярусов коммутации. Несмотря на это многоярусные неблокируемые сети часто более экономичны, чем матричные коммутаторы. Так, например, число КЭ в матричном коммутаторе для М = L = 25 (двадцать пять входов соединяются с двадцатью пятью выходами) равно 625, в трехярусной схеме Клоза - 675, но при М = L = 100 для матричного коммутатора число КЭ уже 10000, a в схеме Клоза - 5700.

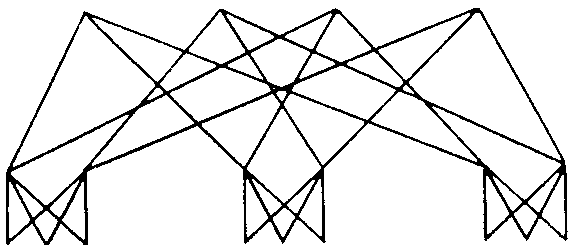

Перестраиваемые сети.

Близки к неблокируемым. Перестраиваемыми они называются потому, что могут выполнить, все возможные соединения между входными и выходными

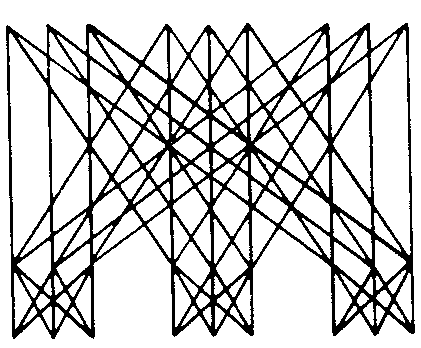

Рис. 4. Сеть Бенеша

портами, перестраивая существующие связи так, как этого требует установление незаблокированного пути для новой заданной пары портов. Структурная схема такой сети, называемой сетью Бенеша, представлена на рис. 4.

Неблокируемые и перестраиваемые сети, обеспечивая высокую гибкость и полноту коммутации, остаются все же достаточно сложными по структуре и соответственно требуют сложного управления. Они безусловно могут использоваться для упорядочения данных в параллельной памяти, однако их применение не всегда целесообразно. В большинстве случаев задача упорядочения решается при некотором ограниченном наборе коммутации и не требует выполнения условий неблокируемости. В связи с этим большой интерес представляют блокируемые многоярусные сети.

Блокируемые сети.

Одним из обобщений блокируемых сетей являются Бэнян-сети, которые введены Р. Гоуком и К. Липовским и использовались для построения мультипроцессорной архитектуры. Свое название они получили oт фигового дерева (banyan-tree). Авторы, очевидно, имели в виду определенное топологическое сходство индийской смоковницы и соответствующего графа.

Граф, описывающий структуру Бэнян-сети, содержит три типа вершин: начальные, не имеющие входящих ребер, конечные, не имеющие исходящих ребер, и промежуточные. Последние имеют и входящие, и выходящие ребра. На рис. 5. приведены примеры Бэнян-сетей. Во всех диаграммах начальные вершины размещены внизу, а конечные - наверху.

Отметим некоторые топологические особенности Бэнян-сетей. Сеть, в которой каждый путь, от начальной вершины к конечной имеет длину l и для каждой пары <начальная вершина—конечная вершина> этот путь является единственным,

Рис. 5. Бэнян-сети.

называется l-уровневой Бэнян-сетью. В такой сети имеется l уровней (ярусов) ребер и l + 1 уровней вершин. В l -уровневых Бэнян-сетях ребра связывают только вершины соседних уровней. Примем, что начальные вершины размещаются на уровне 0, а конечные - на уровне l. В дальнейшем рассматриваются только однородные Бэнян-сети, в которых для всех вершин одного уровня число входящих и число выходящих ребер есть величины постоянные. Структуру однородной Бэнян-сети можно охарактеризовать, если указать число вершин на каждом уровне L0, L1, …,Ll и для вершин каждого уровня число входящих (c) и выходящих (0) ребер. Так как в l-уровневой сети l ярусов ребер, то соответствующее описание всей сети задается l-компонентными векторами с= (с1, с2, ..., сl), о= (o1, o2, ..., ol) и вектором L= (L0, L1, ..., Ll).

Бэнян-сеть называется регулярной, если с1= с2= ...= сl и o1= o2= ...= ol (рис. 5,а), в противном случае сеть нерегулярна (pиc. 5,б). Важное место в классе Бэнян-сетей занимают прямоугольные сети. Сеть является прямоугольной, если L0= L1= ...= Ll и с = о. Нерегулярные прямоугольные Бэнян-сети называются слабо прямоугольными (pиc. 5,в), регулярные - строго прямоугольными (рис. 5,г).

Еще одним обобщенным видом блокируемых многоярусных систем являются Дельта-сети.

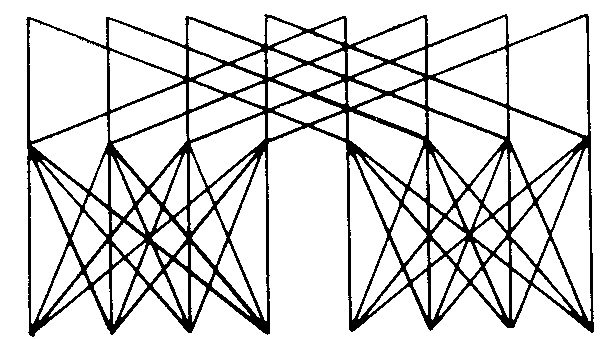

Строго прямоугольные Бэнян-сети с числом узлов на каждом уровне L = 21, построенные на 2 X 2-матричных переключателях, составляют особый подкласс сетей. Эти сети называются двоичными перестановочными (или просто перестановочными) сетями. К ним можно отнести такие широко известные сети как Омега-сеть, сеть типа двоичный n-Куб, модифицируемый манипулятор данных, базисная сеть.

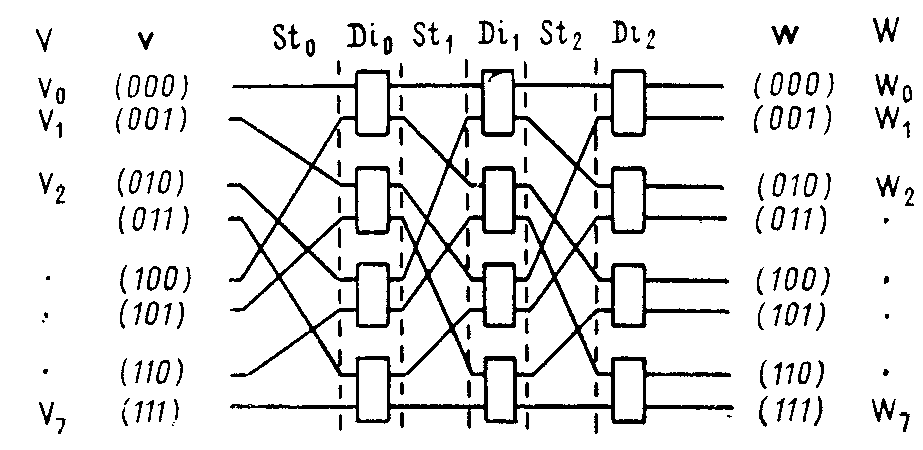

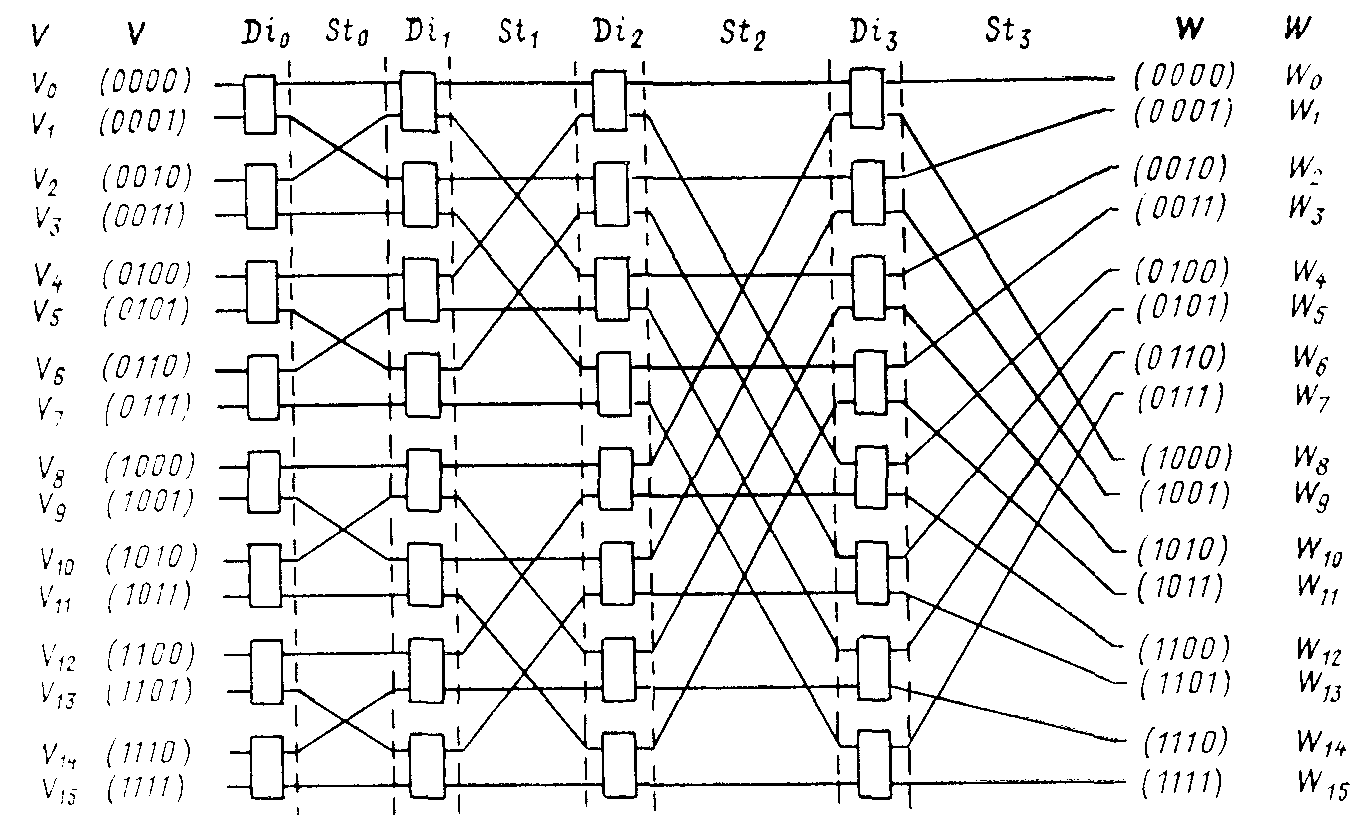

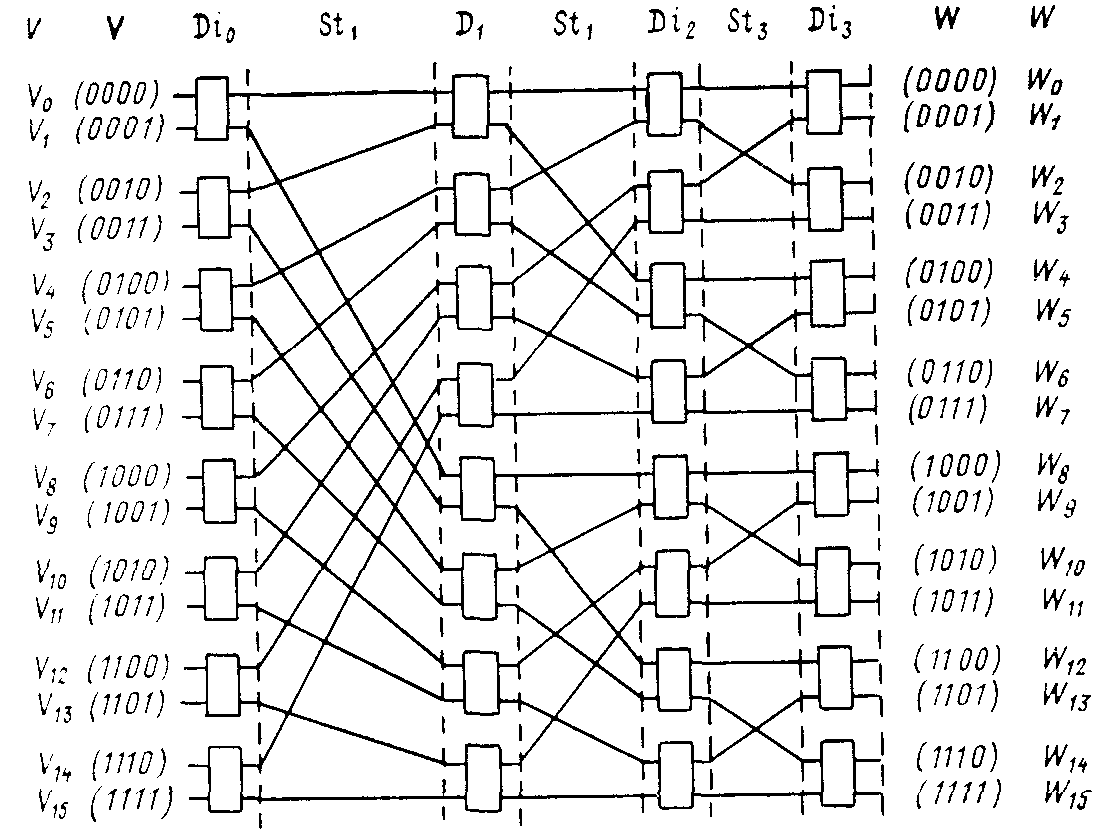

Рис. 6. Обобщенная структура двоичной перестановочной сети.

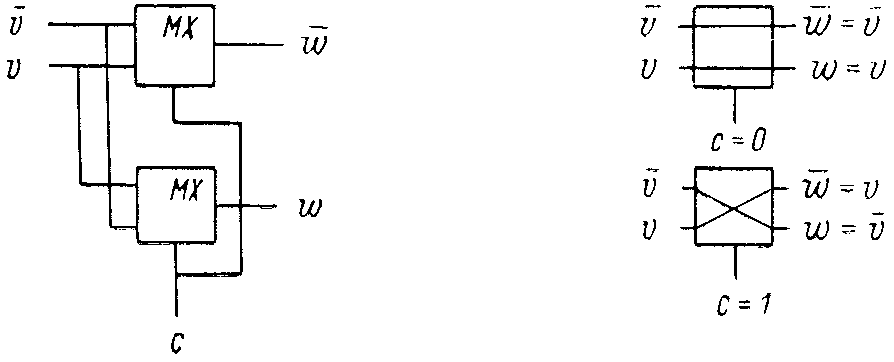

Обобщенная двоичная перестановочная сеть может быть представлена log2L = l ярусами коммутационных элементов, соединенных между собой по определенному закону. Сеть, рассматриваемая как однонаправленная, осуществляет передачу данных от входа к выходу. Каждый ярус сети может быть представлен как два устройства, выполняющих последовательно две перестановки (рис. 6). Одна из них - статическая (St) осуществляется за счет того, что линии связи между ярусами могут изменять позицию при входе в следующий ярус. Статическая перестановка определяется выбранным законом межярусных соединений, она зафиксирована для конкретного вида сети. Вторая, динамическая перестановка (Di), осуществляется коммутационными элементами, и ее содержание определяется выбранным способом управления сетью, а также видом КЭ.

В двоичных перестановочных сетях в качестве КЭ используются 2 Х 2-переключатели двух типов (рис. 7, а, б). Модель КЭ первого типа составлена из двух мультиплексоров 2 X 1, управляемых независимо. Такой КЭ может находиться в четырех различных состояниях, определяемых управляющим сигналами c1, c0. Коммутационные элементы второго типа имеют только два состояния включения и управляются единственным управляющим сигналом с. Мы рассматриваем двоичные перестановочные сети как устройства упорядочения данных в параллельной памяти.

а)

б)

Рис. 7. Структуры коммутационных элементов

Динамическая перестановка полностью определяется состоянием управляющих сигналов, подаваемых на коммутационные элементы соответствующих ярусов, и, следовательно, при одинаковом управлении динамические перестановки в разных l-ярусных двоичных перестановочных сетях совпадают. Общие перестановки, выполняемые этими сетями, различаются только вследствие разных межярусных соединений, т. е. разных статических перестановок.

Рассмотрим и сравним между собой несколько конструкций сетей. На рис. 8 - 10 показаны соответственно Омега-сеть, базисная сеть и n-Куб-сеть.

Рис. 8. Омега-сеть, L = 8.

Рис. 9. Базисная сети, L = 16.

Рис. 10. n – Куб-сеть, L = 16.

Рассмотрим двумерный коммутатор. Каждый процессорный элемент (ПЭ) соединен двусторонними связями с четырьмя соседними (справа, слева, снизу, сверху) (рис. 11, а). Внешние связи могут в зависимости от решаемой задачи программно замыкаться по-разному: вытягиваться в цепочку (рис. 11, б), замыкаться в виде вертикально (рис. 11, в) и горизонтально (рис. 2.11, г) расположенных цилиндров, в виде тороида (рис. 11, д). Коммутационный элемент (КЭ) здесь обычно соединен с оборудованием ПЭ, и объем оборудования всего коммутатора растет пропорционально числу процессоров M.

Рис. 11. Коммутатор с матричной схемой соединений

Быстродействие любого коммутатора во многом определяется максимальным расстоянием D, под которым понимается число промежуточных узлов или тактов передачи информации между самыми удаленными процессорами.

Под кубическим коммутатором понимается пространственная трехмерная структура, где каждый процессор соединен с шестью соседними: четырьмя в своей плоскости и двумя в прилегающих плоскостях.

В общем случае все среды можно назвать n-мерными кубами, тогда кольцевой коммутатор имеет размерность п=1, а матрица - п=2 и т. д. Большое распространение в параллельной вычислительной технике получили среды с размерностями 2 и 3. Чем больше п при неизменном числе процессоров, тем больше радиус связей и тем меньше D. Под радиусом связи понимается число процессоров, напрямую связанных с данным ПЭ.

Величина п может быть и больше трех. Покажем общий прием построения n-кубов произвольной размерности (рис. 2.28).

Для примера рассмотрим возможные связи элемента 9 матрицы, изображенной на рис. 11, а. Этот элемент в своей строке связан с элементами 8 и 10, адреса которых отличаются на -1 и +1. Если бы данная строка составляла независимый коммутатор с размерностью 4 (n=1, M=4), то связи любого ПЭi такого коммутатора описывались бы рангом 1. Если элемент 9 находится в матрице, то его связи с элементом 5 верхней строки и элементом 13 нижней строки отличаются на +M и -M, где M=4 - размер строки. Следовательно, связи элемента ПЭi матричного коммутатора описываются рангом 2 (см. рис. 2.28).

Если бы элемент 9 находился в кубе, то номера смежных элементов соседних плоскостей отличались бы на ±M2, в кубе степени 4 - на ±M3 и т. д., что и показано на рис. 2.28. Такая методика позволяет построить куб любой степени и вычислить величину D.

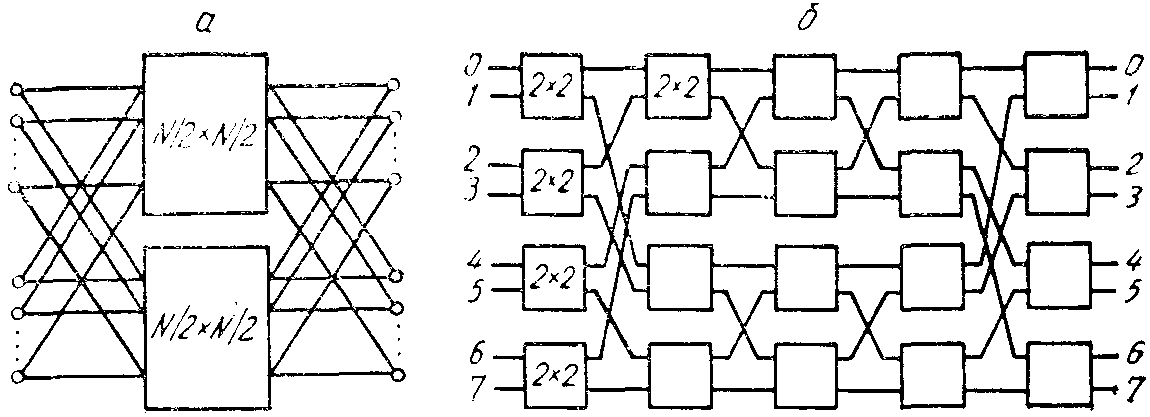

Многокаскадные коммутаторы помогают создать более дешевые варианты соединительных и обобщенных соединительных сетей. Координатный переключатель nxn можно свести к двум (N/2XN/2) переключателям с замещением (рис. 13, а). В свою очередь переключатели N/2XN/2 могут быть разложены на более мелкие подобным же образом. Пример сети, приведенной до уровня стандартных 1<Э размерностью 2х2, дан на рис. 13, б. По определению, это полная соединительная сеть (сеть Бенеша), обеспечивающая N! возможных перестановок, каждая из которых выполняется за один такт работы сети. В такой сети отсутствуют конфликты для любых парных соединений.

Стандартный КЭ размерностью 2Х2 и возможные в нем соединения показаны на рис. 14. Иногда для построения больших сетей применяются элементы 4Х4 или 8Х8. Основной недостаток сети Бенеша - большое количество элементов, необходимых для ее построения.

Рис. 13. Способ построения сети Бенеша

Рис. 14. Коммутационный элемент размерностью 2Х2 и допустимые перестановки.

Внизу приведены коды для нумерации перестановок

Широко используются неполные соединительные сети: омега-сеть, сеть Бенеша, R-сеть и др. Омега-сеть относится к типу сетей тасовки с замещением.

Коммутационные сети могут работать в двух режимах: коммутация каналов и коммутация сообщений. В первом случае сначала с помощью адресной системы устанавливается прямой электрический тракт между парой соединяемых точек, а затем по этому тракту передастся информация. Такой вид связи используется, например, в телефонных сетях. Во втором случае каждая передаваемая единица информации снабжается адресом требуемого выхода и перемещается от узла ni, к узлу ni+1, где i - номер каскада; п и т - номера коммутационных узлов в каскадах. После того как информация принята узлом mi+1, линия, соединявшая ni и mi+1, становится доступной для других соединении. Узел mi+1 по адресной части сообщения определяет дальнейший маршрут сообщения. В матрицах процессоров используется как коммутация каналов, так и коммутация сообщений.

Для описания сетей вводят некоторые обозначения. Пусть входы перестановочной сети обозначаются метками V0, V1, ..., V L-1, а выходы - W0, W1, ..., WL-1. При нумерации входов и выходов целыми числами эти метки принимают значения, соответствующие их индексам, т. е. Vo = 0, V1 = 1, .... VL-1 = L-1 и Wo = 0, W1 = 1, .... WL-1=L-1. Обозначим двоичные коды номеров входов и выходов сети l-компонентными двоичными векторами v = (vl-1 vl-2 ... v0) и w = (wl-1 wl-2 ... w0). Тогда множества всех входных и выходных портов сети есть V = {V0, V1, … , VL-1} и W = { W0, W1, … , WL-1}, или в двоично-векторной форме V = {v0, v1, … , vL-1} и W = { w0, w1, … , wL-1}.

Опишем перестановку, выполняемую двоичной перестановочной сетью как преобразование кодов v, т. е. W = V == {v0, v1, ... , vL-1}. Так как общая перестановка является комбинацией статических (S1) и динамических (Di) перестановок, то, например, для Омега-сети (рис. 8) можно записать

v = v(St0Di0St1Di1St2Di2),

или в общем виде

v = v(St0Di0St1Di1 … Stl-1Dil-1) .

Перестановки, выполняемые базовыми и n-Куб-сетями, описываются выражениями

vбазисные = v(Di0St1Di1St2 … Dil-1)базисные,

vn-Куб = v(Di0St0Di1St1 … Dil-1 Stl-1) n-Куб .

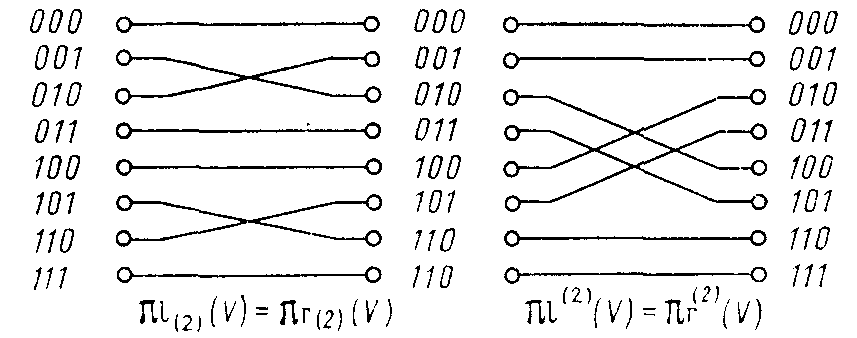

При одинаковом управлении динамические перестановки для всех трех сетей одинаковы. Поэтому, чтобы сравнить работу перестановочных сетей, необходимо раскрыть содержание статических перестановок. Преобразование vSt имеет связь с перестановками типа полной тасовки, получившими свое название от того, что перестановка выполняется посредством разрезания одного набора на два и чередованием их элементов как при полной тасовке карт (рис. 15).

Рис. 15. Перестановки типа полной тасовки.

Еще несколько перестановок этого типа: k-я левая (l(k)) и правая (r(k)) подтасовки и k-я левая (l(k)) и правая (r(k)) надтасовки, которые могут быть охарактеризованы циклическими сдвигами влево и вправо младших и старших разрядов двоичного представления Vv.

В Омега-сети в качестве статических перестановок на всех ярусах используется перестановка полной тасовки , а в базисной сети - правая подтасовка при k = l-v, где v - номер яруса. В n-Куб-сети перестановка полной тасовки выполняется на последнем ярусе, а на всех предыдущих статические перестановки описываются несколько другим выражением выражением.

Описания перестановок, выполняемых Омега-, базисными- и n-Куб-сетями, различаются только порядком разрядов двоичных векторов и могут быть легко приведены друг к другу. Это значит, что, зная управляющий вектор для одной сети, мы можем выполнить такую перестановку на другой сети, переставив соответствующим образом разряды вектора управления и перенумеровав входы.

Применение перестановочных сетей в параллельной памяти требует параллельного выполнения коммутаций (перестановок) для всех L входов. Одни из вариантов такой работы сети получится, если принять, что все КЭ одного яруса имеют общее управление, т. е. управляются одним сигналом cv. Тогда, такое управление сетью будем называть поярусным.

При поярусном управлении n-Куб-сеть может реализовать всего 2l различных перестановок. В то же время в l-ярусной сети l * 2l-1 коммутационных элементов, поэтому при раздельном управлении число различных коммутаций сети составит 2k, где k=l*2l-1. В таком случае управление сетью значительно усложняется. В связи с этим встает вопрос об анализе и синтезе перестановок для заданной сети.

Будем рассматривать перестановки, выполняемые над L элементами за один проход сети. Любая перестановка будет допустима, если она требует для каждого КЭ сети единственного управляющего сигнала, т. е. если не возникает конфликтов при управлении КЭ. Приведем описание указанного условия для n-Куб-сети.

Возьмем любой КЭ нулевого яруса. Пара линий, подходящих к нему, различаются по номеру (адресу) только в одном младшем разряде двоичного представления. Выходы также различаются только младшим разрядом. Причем, если этот разряд не изменился на КЭ нулевого яруса, то он уже нe может измениться на остальных КЭ сети. Например, если после нулевого яруса рассматривать верхний выход КЭ, которому соответствует значение 0 в младшем разряде номера линии, то после прохождения всей сети эта линия может быть скоммутирована только на те выходы сети, в которых младший разряд двоичного представления номера выхода w0 = 0, что легко