- •Министерство образования рф эту (лэти)

- •Современных эвм”

- •Содержание

- •1. Задание на курсовое проектирование

- •4. Форматы данных, команд и способы адресации

- •5.1. Логика установки флажков

- •6. Архитектура внешних выводов кристалла цп

- •7. Временные диаграммы выполнения основных операций на шине

- •9 Ао уПi квв ло бп бпв Ост Нет Да Нет Да Рис. 7. Обобщённый алгоритм функционирования

- •10. Алгоритмы выполнения отдельных операций

- •10.1. Выборка команды

- •10.2. Обработка адресной части команды

- •10.3. Арифметические и логические операции

5.1. Логика установки флажков

При выполнении арифметических или логических операций, результаты некоторым образом отражаются в регистре флагов:

Если в результате предыдущей операции получился 0, то флаг Zустанавливается в единицу, в противном случае в 0.

Если в результате предыдущей операции произошло переполнение, то флаг Oустанавливается в 1, в противном случае в 0.

Если в результате предыдущей операции произошёл перенос из старшего разряда, то флаг Cустанавливается в 1, в противном случае в 0.

Если в результате предыдущей операции получено отрицательное число, то флаг Sустанавливается в 1, в противном случае в 0.

6. Архитектура внешних выводов кристалла цп

Н

Рис. 5

Тактовые импульсы для работы процессора подаются на вход CLC.

Имеется возможность сброса (инициализации) процессора по сигналу RESET.

На контакт READY приходит сигнал готовности от медленных устройств.

Сигнал ALE используется для фиксации адреса, выданного в шину адреса, на внешнем регистре – защёлке.

Линии RD, WR, IN, OUT задают выполняемую на шине операцию.

Для изготовления процессора был выбран стандартный корпус на 68 контактов. Все неиспользуемые контакты используются для дублирования контактов “Земля” (GND) и “Напряжение питания” (+5V).

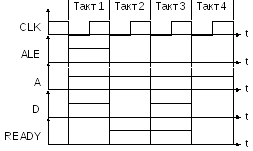

7. Временные диаграммы выполнения основных операций на шине

Т

CLK

D

A

t

t

t

t

t

ALE

READY

Такт 1

Такт 2

Такт 3

Такт 4

ип

операции на шине определяется словом

состояния процессора, которое в начале

каждого цикла выдаётся на шину данных

и запоминается на внешнем регистре

системы. В исходном состоянии,

под действием сигнала “Сброс”, счётчик

команд и регистр команд установлены в

0.

ип

операции на шине определяется словом

состояния процессора, которое в начале

каждого цикла выдаётся на шину данных

и запоминается на внешнем регистре

системы. В исходном состоянии,

под действием сигнала “Сброс”, счётчик

команд и регистр команд установлены в

0.

7.1. Чтение

Операция чтения включает в себя 4 такта:

На шину данных выдаётся слово состояния процессора, которое запоминается на внешнем регистре системы, а на шину адреса – содержимое счётчика команд.

Если память готова к выполнению цикла чтения, то появляется управляющий сигнал “READY”.

Происходит чтение из памяти.

Подготовка очердного состояния.

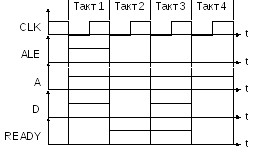

7 .2.

Запись

.2.

Запись

Операция записи включает в себя 4 такта:

На шину данных выдаётся слово состояния процессора, которое запоминается на внешнем регистре системы, а на шину адреса – содержимое счётчика команд.

Если память готова к выполнению цикла записи, то появляется управляющий сигнал “READY”.

Происходит запись в память.

Подготовка очердного состояния.

7 .3.

Ввод

.3.

Ввод

Операция ввода включает в себя 4 такта:

На шину данных выдаётся слово состояния процессора, которое запоминается на внешнем регистре системы, а на шину адреса – номер устройства ввода/вывода.

Если устройство готово к выполнению цикла ввода, то появляется управляющий сигнал “READY”.

Происходит ввод из устройства.

Подготовка очердного состояния.

7 .4.

Вывод

.4.

Вывод

Операция вывода включает в себя 4 такта:

На шину данных выдаётся слово состояния процессора, которое запоминается на внешнем регистре системы, а на шину адреса – номер устройства ввода/вывода.

Если устройство готово к выполнению цикла вывода, то появляется управляющий сигнал “READY”.

Происходит вывод в устройства.

Подготовка очердного состояния.

7

CLK

D

A

t

t

t

t

t

ALE

READY

Такт 1

Такт 2

Такт 3

Такт 4

INT

INTA

t

t

Такт 6

Такт 5

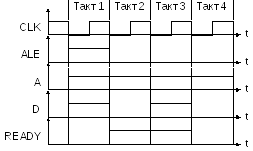

.5.

Прерывание

.5.

Прерывание

Цикл прерывания включает в себя 6 тактов:

Происходит запрос прерывания.

На шину адреса поступает адрес вектора прерывания.

Если память готова к чтению вектора, то появляется управляющий сигнал “READY”.

Происходит чтение вектора прерывания.

Происходит разрешение прерывания.

Подготовка очердного состояния.

7

HLD

HLDA

t

t

Такт 3

.6.

Захват шины

.6.

Захват шины

Ц

CLK

t

Такт 1

Такт 2

Происходит запрос захвата.

Происходит разрешение захвата шины.

Подготовка очердного состояния.

8 .

Структурно-функциональная схема

процессора

.

Структурно-функциональная схема

процессора

А

Рис. 6

Сумматор накапливающего типа СМ, на котором находится 1-й операнд и формируется результат выполнения операции;

Регистр Р1, на котором находится 2-й операнд;

Регистр кода операции РКОП;

Устройство управления УУ АЛУ, которое вырабатывает последовательность управляющих сигналов в соответствии с заданным кодом операции.

ОП – оперативная память (см. рис. 6). Она предназначена для хранения команд и данных. Она включает в себя:

ОП – запоминающая часть, в которой хранятся команды и данные;

Регистр адреса РА, на котором находится адрес ячейки памяти, к которой производится обращение;

Регистр данных РД, на котором находится записываемое в ОП или считываемое из ОП слово;

Устройство управления УУ ОП вырабатывает управляющие сигналы для выполнения операций записи или чтения.

В нижней части рисунка расположено центральное устройство управления, предназначенное для управления ходом процесса решения задач. Оно включает в себя:

Регистр команд РК, на котором находится очередная команда;

Счётчик адресов команд IP, на котором формируется адрес очередной команды;

Дешифратор группы операций ДШ. Его выходами являются признаки групп операций (АО, ЛО, … ,Ост).

Устройство управления УУ вырабатывает последовательность управляющих сигналов для обработки соответствующей группы операций.