Курсовой проект по дисциплине «Архитектура современных ЭВМ

.docМинистерство общего и профессионального образования РФ

Санкт-Петербургский Государственный Электротехнический

Университет им. В.И.Ульянова (Ленина)

«ЛЭТИ»

Курсовой проект по дисциплине: «Архитектура современных ЭВМ»

«Разработка архитектуры однокристального RISC процессора».

Выполнил:

XXX X.X.

Факультет: КТИ

Кафедра: АСОИУ

Группа:9331

Преподаватель:

Анисимов А.В.

![]()

Санкт-Петербург

2001 г.

Оглавление

Задание на курсовое проектирование

Формат и структура данных

Формат и структура команд

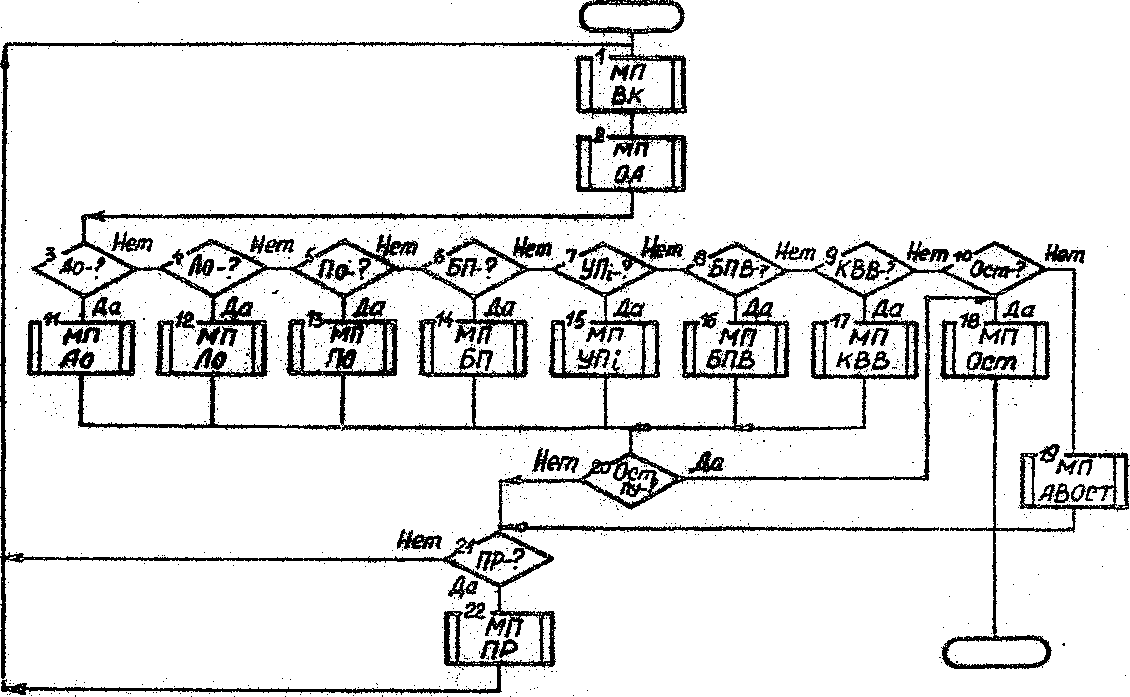

Обобщенная схема алгоритма функционирования процессора

Выборка команды

Обработка адресной части команды

Выполнение команд арифметических операций

Выполнение команд логических операций

Выполнение команды пересылки

Выполнение команд передачи управления

Безусловный переход

Условный переход

Безусловный переход к подпрограмме

Выполнение команд ввода-вывода

Прерывание программы

Сигналы управления

Флаги

Задание на курсовое проектирование

Номер варианта: 9

-

Формат данных: 8, 16, 32

-

Адресность: 3

-

Способы адресации: относительная, прямая, косвенная

-

Регистровая память:

-

количество – 32

-

тип – универсальные

-

разрядность – 16

-

-

Шина адрес- данные: раздельная

-

Основная память:

-

объем – 1024 Мб

-

ШД – 16

-

-

Ввод- вывод: по аналогии с ячейками памяти

-

Прерывания: равные приоритеты

Формат и структура данных

Представление данных с фиксированной запятой (дробная часть):

![]()

где

![]() - значение i – го разряда

числа X

- значение i – го разряда

числа X

q – основание системы счисления

k – количество цифр после запятой

|

|

x-1 |

… |

x-i |

… |

x-k |

Представление данных с фиксированной запятой (целые числа):

![]()

где

![]() - значение i – го разряда

числа X

- значение i – го разряда

числа X

q – основание системы счисления

k – количество старших цифр

|

|

xk-1 |

… |

xi |

… |

x0 |

Представление данных с плавающей запятой:

![]()

где

![]() -

нормализованная мантисса числа X

-

нормализованная мантисса числа X

![]() -

целочисленный порядок числа X

-

целочисленный порядок числа X

q – основание системы счисления

Формат и структура команд

|

КОП |

ПА1 |

А1 |

ПА2 |

А2 |

ПА3 |

А3 |

Распределение полей:

КОП – поле кода операции (7 разрядов)

А1, А2, А3 – поля адресов оперативной памяти, соответственно, 1-го, 2-го операндов и результата (16 разрядов на каждое поле)

ПА1, ПА2, ПА3 – признаки адресации, соответственно, адресов А1, А2, А3 (3 разряда на признак)

Обобщенная схема алгоритма функционирования процессора

Выборка команды

Одна команда размещается в нескольких ячейках ОП.

В данном случае при выборке требуется столько обращений к ОП, сколько ячеек ОП занимает одна команда. Для подсчета числа обращений к ОП вводится счетчик СЧ + к выходу счетчика подключается дешифратор.

Разрядность ячейки ОП равна 16, разрядность команда равна 64, следовательно одна команда занимает 4 ячейки ОП.

[ Y5:Сч:=2

[ Y2:PA:= СчАК

[Y1:

СчАК:= СчАК+1

[Y1:

СчАК:= СчАК+1

[Y3:чтение

из ОП?

[Y3:чтение

из ОП?

[X1:ОП закончила

[ работу ?

[ работу ?

[Y6:CЧ:=

Сч-1

[Y6:CЧ:=

Сч-1

[Y4:

Pк[Cч]:=РД

[Y4:

Pк[Cч]:=РД

[X2:Cч=0

?

[X2:Cч=0

?

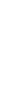

Обработка адресной части команды

(ПА +КА1) – число ступеней(глубина) КА задано признаком адресации в поле команды

(ПА + ОА2) – для модификации адреса используется восемь индексных регистров (РИ0 -РИ7) и специальное индексное АУ (ИАУ)

[ X3 : FL = 1 ?

[ Y7 : PA := PK[0:15]

[ Y3 : Чтение из ОП

[

X1 : ОП закончила работу ?

[

X1 : ОП закончила работу ?

[ Y8 : PK[0:16] := РД[0:16]

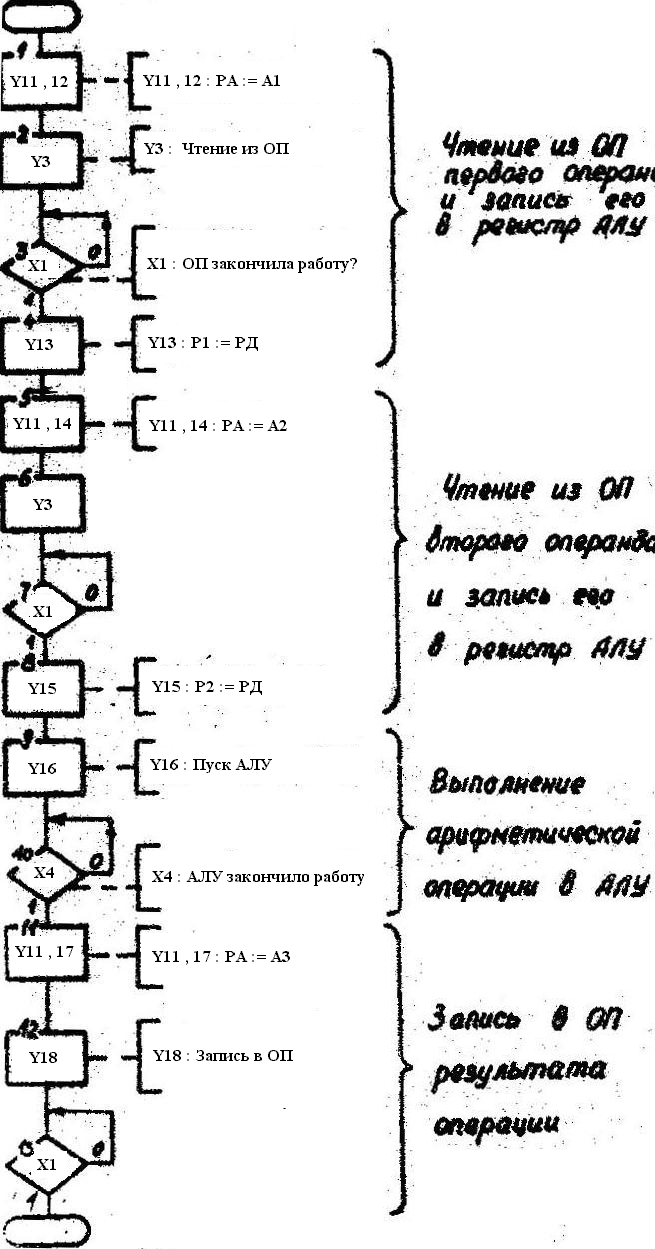

Выполнение команд арифметических операций

К арифметическим операциям относятся операции сложения, вычитания, умножения, деления. Содержание процедуры выполнения команды арифметической операции состоит из выборки двух исходных данных из памяти ЭВМ, выполнение исчисления результата операции и сохранение результата либо на специально выделенном для этого регистре, либо в ячейке памяти ЭВМ. Исходным состоянием процессора для выполнения любой команды является наличие команды на регистре команд РК после выборки команды.

Выполнение команд логических операций

К типичным логическим операциям относятся логическое сложение «ИЛИ», логическое умножение «И», сложение по модулю 2, инверсия, сравнение.

Все логические операции являются поразрядными, т.е. такими, в которых отсутствует связь между разрядами, как это имеет место при выполнение арифметических операций. Поэтому каждый из логических операторов может быть описан системой логических уравнений, определяющих содержание основной решающей операции:

![]() ;

;

![]() ;

;

![]() ;

;

![]()

Логические операции с фиксированной длиной операндов выполняются аналогично арифметическим операциям. Полностью совпадают с приведенными в предыдущем пункте структурой и микропрограммой. В АЛУ логическая обработка реализуется путем использования определенного числа логических схем типа «ИЛИ», «И», «НЕ» и др. Реализация операторов в АЛУ происходит за один такт, в течение которого осуществляется одновременная передача из RG1 и RG2 АЛУ на соответствующие логические схемы, с выхода которых результат операции записывается в RG4 АЛУ.

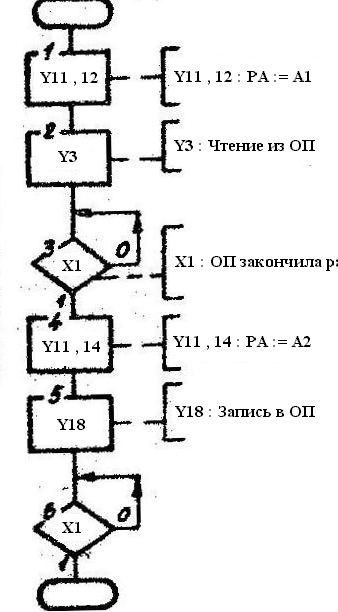

Выполнение команды пересылки

Содержание процедуры пересылки данных заключается в создании новых данных, идентичных оригиналу. При выполнении операции содержимое ячейки памяти, в которой хранится оригинал, пересылается в ячейку памяти, в которой будет хранится копия, а оригинал остается нетронутым. Таким образом, команда пересылки данных осуществляет дублирование данных.

Выполнение команд передачи управления

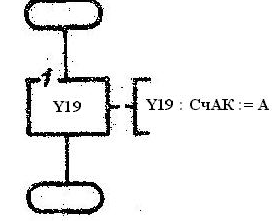

Безусловный переход

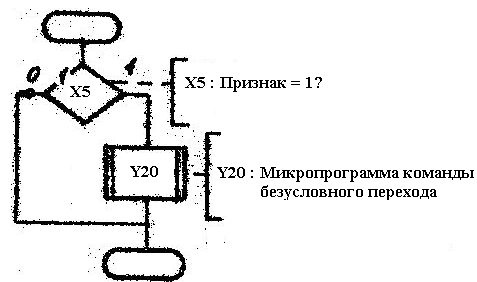

Условный переход

Безусловный переход к подпрограмме

Выполнение команд ввода-вывода

Прерывание программы

Сигналы управления

Y1 : СчАК := СчАК + 1 ; Увеличение счетчика адреса команд на единицу

Y2 : РА := СчАК ; Передача содержимого СчАК в регистр адреса оперативной памяти

Y3 : Чтение из ОП хранящейся в ней информации на регистр данных ОП

Y4 : РК Сч := РД ; Передача данных из РД ОП в регистр команд

Y5 : Сч := 3 ; В счетчик записывается код, значение которого равно количеству ячеек, минус единица

Y6 : Сч := Сч-1; Уменьшение счетчика на единицу после очередного считывания

Y7 : РА := РК [0:15]

Y8 : РК [0:16]:= РД [0:16]

Y9 : СмИ := РК [0-15]

Y10 : Сложение

Y11 : СмИ := РИ (РК[FL2-FL4])

Y12 : РА := СмИ

Y13, Y14 : РА := А1

Y15 : Р1 := РД

Y16, Y17 : РА := А2

Y18 : Р2 := РД

Y19 : Пуск АЛУ

Y20, Y21 : РА := А3

Y22 : Запись в ОП

Y23 : СчАК := А

Y24 : Микропрограмма команды безусловного перехода

Y25 : СчАК := А1

Y26 : РАВВ := РК[А1]

Y27 : Чтение ВВ

Y28 : РА := РДВВ

Y29 : РДВВ := РА

Y30 : Запись ВВ

Y31 : Прием запросов

Y32 : Выявление приоритетного запроса и формирования его номера

Y33 : Сброс запросов

Y34 : Разрешение прерывания

Y35 : Внутренний запрос

Y36 : Внутренний запрос

Флаги

X1 : ОП закончила работу ?

X2 : Cч=0 ?

X3 : FL = 1 ? (признак адресации)

X4 : АЛУ закончила работу ?

X5 : Признак = 1 ?

X6 : Готово ?

X7 : Наличие запроса