- •Министерство образования рф эту (лэти)

- •Современных эвм”

- •Содержание

- •1. Задание на курсовое проектирование

- •4. Форматы данных, команд и способы адресации

- •5.1. Логика установки флажков

- •6. Архитектура внешних выводов кристалла цп

- •7. Временные диаграммы выполнения основных операций на шине

- •9 Ао уПi квв ло бп бпв Ост Нет Да Нет Да Рис. 7. Обобщённый алгоритм функционирования

- •10. Алгоритмы выполнения отдельных операций

- •10.1. Выборка команды

- •10.2. Обработка адресной части команды

- •10.3. Арифметические и логические операции

Министерство образования рф эту (лэти)

Курсовая работа

по предмету

“Архитектура

Современных эвм”

Выполнил: Колпаков Д. Ю.

гр. 9362

Проверил: Анисимов А.В.

Санкт-Петербург 2001

Содержание

1. Задание на курсовое проектирование 3

1.1. Исходные данные 3

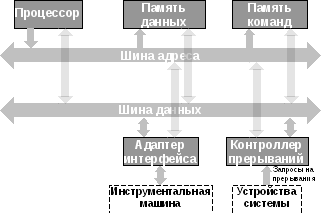

2. Структурная схема разрабатываемой системы 4

3. Структура регистровой памяти 5

4. Форматы данных, команд и способы адресации 6

4.1. Форматы данных 6

4.2. Формат команд 6

4.3. Способы адресации 7

5. Система команд 8

5.1. Логика установки флажков 10

6. Архитектура внешних выводов кристалла ЦП 11

7. Временные диаграммы выполнения основных операций на шине 13

7.1. Чтение 13

7.2. Запись 14

7.3. Ввод 15

7.4. Вывод 16

7.5. Прерывание 17

7.6. Захват шины 18

8. Структурно-функциональная схема процессора 19

9. Обобщённый алгоритм функционирования 21

10. Алгоритмы выполнения отдельных операций 23

10.1. Выборка команды 23

10.2. Обработка адресной части команды 24

10.3. Арифметические и логические операции 25

10.4. Передача управления 26

11. Заключение 28

1. Задание на курсовое проектирование

Разработать архитектуру однокристального RISCпроцессора для встроенных применений, который может использоваться, например, в составе систем управления в реальном масштабе времени.

1.1. Исходные данные

Формат данных:16 разрядов с ФТ, 32 разряда с ФТ, 32 разряда с ПТ.

Адресность: 1.

Способ адресации:относительный, прямой и косвенный.

Регистровая память:32 универсальных 16-ти разрядных регистра.

Шина адрес – данные:раздельные шины адреса и данных.

Память данных:объём – 4 Кб, 16 разрядов шины данных.

Память команд:объём – 4 Кб, 16 разрядов шины команд.

Ввод – вывод:изолированный.

Прерывания:одноуровневая система прерываний.

2. Структурная схема разрабатываемой системы

В

Рис. 1

3

IP 15 0 Flags

РК

31 0

РД

31 0

В

R0 R1 R2 . . . R29 R30 R31 15 0

Рис. 2

СМ

15 0

Р1

15 0

РА

15 0

РКОП

15 0

Регистры R0 – R31доступны для пользователя, как на чтение, так и на запись.

Регистры IP,Flags, СМ, Р1, РКОП, РК,РД и РАявляются системными (см. рис. 2).

Регистр IPпредставляет собой счётчик команд, в котором постоянно хранится адрес следующей команды, которую необходимо выполнить. Данный регистр недоступен для пользователя, однако существует один из способов его изменения – это команды перехода.

В регистре Flagsхранится состояние процессора (см. рис. 2).

Z– признак нулевого результата;

C– признак переноса из старшего разряда;

S– знак результата;

O– признак переполнения результата;

I– разрешение прерывания;

T– пошаговый режим;

U– режим супервизор/пользователь.

Регистр РК представляет собой регистр команд, в который записывается выполняемая команда.

Регистр РД – регистр данных.

Регистр РКОП – регистр кода операции.

Регистр РА– регистр адреса.

Регистры СМ и Р1 предназначены для хранения 1-го и 2-го операндов.