МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

Санкт-Петербургский государственный университет аэрокосмического

приборостроения

Кафедра № 22 «Радиотехнических систем»

Методические указания по выполнению лабораторной работы

«Исследование последовательностных цифровых устройств»

(Реализация счетчиков и регистров с заданными характеристиками на базе триггеров и ИМС средней степени интеграции.)

2003 г.

Цель работы: ознакомление с функциональными особенностями

цифровых устройств последовательностного типа,

получение навыков синтеза счетчика с заданным

коэффициентом пересчета, моделирование получен-

ных результатов с помощью пакета программ

Electronics Workbench (EWB).

Задание на лабораторную работу.

Разработать на базе триггеров и ИМС средней степени интеграции счетчик требуемого типа с заданным коэффициентом пересчета.

Последовательностным цифровым устройством (ПЦУ) называется устройство, у которого состояние выходов в некоторый момент дискретного времени зависит не только от комбинаций сигналов на его входах в тот же момент времени, но и от состояния входов и выходов в предыдущий момент времени.

Все ПЦУ делятся на два основных класса:

1) Счетчики

a. По структуре: b. По направлению счета: - последовательные; - прямого счета

(суммирующие);

- параллельные; - обратного счета

(вычитающие);

- параллельно-последовательные. - с управляемым

направлением счета

(реверсивные).

Счетчики могут быть с естественным порядком счета и с требуемым порядком счета.

2) Регистры

Параллельные регистры (регистры хранения).

Последовательные регистры (регистры сдвига).

Параллельно-последовательные регистры с управляемым направлением сдвига (универсальные).

Элементарной структурной единицей всех ПЦУ является триггер,

который может находиться в одном из двух устойчивых состояний.

Основные виды используемых триггеров представлены в таблице 1.

Таблица 1.

СХЕМА |

Условное графическое |

Таблица истинности |

|||||||||||||

обозначение |

|||||||||||||||

|

|

|

|

|

|

|

|

|

входы |

выходы |

|||||

|

|

|

|

|

|

|

|

Режим |

S |

R |

Q |

_ |

|||

|

|

|

|

|

|

|

|

работы |

Q |

||||||

RS-триггер |

|

|

S |

T |

Q |

|

|

Запрещенное |

1 |

1 |

- |

- |

|||

(асинхронный) |

|

|

|

|

_ |

|

|

состояние |

|||||||

|

|

|

R |

|

Q |

|

|

Установка лог.0 |

0 |

1 |

0 |

1 |

|||

|

|

|

|

|

|

|

|

Установка лог.1 |

1 |

0 |

1 |

0 |

|||

|

|

|

|

|

|

|

|

Хранение |

0 |

0 |

Q |

_ |

|||

|

|

|

|

|

|

|

|

Q |

|||||||

|

|

|

|

|

|

|

|

|

входы |

выходы |

|||||

|

|

|

|

|

|

|

|

Режим |

C |

D |

S |

R |

Q |

_ |

|

|

|

|

|

|

|

|

|

работы |

Q |

||||||

|

|

|

|

|

|

|

|

Запрещенное |

- |

- |

0 |

0 |

- |

- |

|

|

|

|

|

|

|

|

|

состояние |

|||||||

D-триггер |

|

|

S |

T |

Q |

|

|

Асинхронная |

- |

- |

1 |

0 |

0 |

1 |

|

(синхронный) |

|

|

D |

|

|

|

|

установка лог.0 |

|||||||

|

|

|

C |

|

_ |

|

|

Асинхронная |

- |

- |

0 |

1 |

1 |

0 |

|

|

|

|

R |

|

Q |

|

|

установка лог.1 |

|||||||

|

|

|

|

|

|

|

|

Cинхронная |

|

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

установка лог.0 |

|||||||

|

|

|

|

|

|

|

|

Cинхронная |

1 |

1 |

1 |

1 |

0 |

||

|

|

|

|

|

|

|

|

установка лог.1 |

|||||||

|

|

|

|

|

|

|

|

|

входы |

выходы |

|||||

|

|

|

|

|

|

|

|

Режим |

C |

J |

K |

S |

R |

Q |

_ |

|

|

|

|

|

|

|

|

работы |

Q |

||||||

|

|

|

|

|

|

|

|

Запрещенное |

- |

- |

- |

0 |

0 |

- |

- |

|

|

|

|

|

|

|

|

состояние |

|||||||

|

|

|

|

|

|

|

|

Асинхронная |

- |

- |

- |

1 |

0 |

0 |

1 |

JK-триггер |

|

|

S |

|

Q |

|

|

установка лог.0 |

|||||||

(синхронный) |

|

|

J |

T |

|

|

|

Асинхронная |

- |

- |

- |

0 |

1 |

0 |

1 |

|

|

|

C |

|

|

|

|

установка лог.1 |

|||||||

|

|

|

K |

|

_ |

|

|

Хранение |

|

0 |

0 |

1 |

1 |

Q |

_ |

|

|

|

R |

|

Q |

|

|

Q |

|||||||

|

|

|

|

|

|

|

|

Cинхронная |

0 |

1 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

установка лог.0 |

|||||||

|

|

|

|

|

|

|

|

Cинхронная |

1 |

0 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

установка лог.1 |

|||||||

|

|

|

|

|

|

|

|

Переключение |

1 |

1 |

1 |

1 |

_ |

Q |

|

|

|

|

|

|

|

|

|

Q |

|||||||

У словные

обозначения:

словные

обозначения:

0 -низкий

уровень; 1-высокий уровень;

-низкий

уровень; 1-высокий уровень;  -

переход от низкого уровня к высокому;

- переход от высокого уровня к низкому;

-

переход от низкого уровня к высокому;

- переход от высокого уровня к низкому;

Алгоритм синтеза счетчика с заданным коэффициентом пересчета.

1) Составление таблицы состояний для заданного счетчика, выделив первый код лишнего и разрешенного состояния в зависимости от направления счета.

2) Разработка в соответствии с первым кодом лишнего состояния деши-фратора, выходы которого поступают в соответствии с первым кодом разрешенного состояния на входы предварительной установки триггеров, входящих в состав счетчика.

3) Реализация требуемого счётчика на базе триггеров и ИМС средней степени интеграции:

- синтез рабочей схемы при помощи пакета программ Electronics Workbench;

- синтез рабочей схемы на основе отечественных интегральных микросхем.

4) Анализ работы полученного устройства, выводы по полученным результатам.

Выполнение работы.

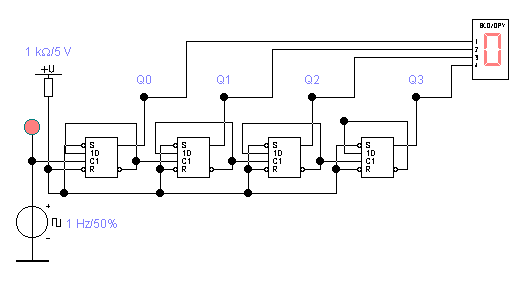

Схема заданного асинхронного четырёхразрядного двоичного счетчика на базе D-триггеров представлена на рис.1.

Необходимо разработать двух декадное цифровое устройство, выполня-ющее функции секундомера, поэтому работу желательно разделить на две части:

реализация счетной декады младших разрядов с коэффициентом пересчёта десять;

р

еализация

счетной декады старших разрядов с

коэффициентом пересчёта шесть;

еализация

счетной декады старших разрядов с

коэффициентом пересчёта шесть;

Рис.1 Рабочая схема асинхронного двоичного счетчика на базе D-триггеров.

Синтез счетной декады младших разрядов.

1.Составление таблицы состояния заданного двоичного счетчика.

Выделение кодовых комбинаций, соответствующих разрешенному состоянию.

Таблица 2.

16-код |

Двоичное представление 16-го кода |

Примечание

|

|||

N |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

1-й код разрешенного состояния |

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

|

A |

1 |

0 |

1 |

0 |

1-й код запрещённого состояния |

b |

1 |

0 |

1 |

1 |

|

C |

1 |

1 |

0 |

0 |

|

d |

1 |

1 |

0 |

1 |

|

E |

1 |

1 |

1 |

0 |

|

F |

1 |

1 |

1 |

1 |

|

- разрешённые кодовые комбинации;

-

запрещённые кодовые комбинации;

-

запрещённые кодовые комбинации;

2. Разработка дешифратора.

Для дешифрации первого кода лишнего состояния необходимо разработать цифровое устройство, работа которого описывается выражением:

_

_

_

_

A=Q0*Q2*Q1*Q3

Для синтеза рабочей схемы дешифратора необходимы следующие КЦУ:

- три схемы НЕ (инверторы);

- схема 4И;

Рабочая схема

дешифратора представлена на рис.2.

Рабочая схема

дешифратора представлена на рис.2.

Рис.2 Рабочая схема синтезированного дешифратора.

3.1 Реализация счётной декады младших разрядов с помощью пакета

программ EWB.

Функциональная схема счетчика представлена на рис.3.

Р ис.3

Рабочая схема счётной декады младших

разрядов.

ис.3

Рабочая схема счётной декады младших

разрядов.

Временные диаграммы сигналов для счётчика приведены на рис.4.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вход |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Двоичный счёт |

0000 |

0001 |

0010 |

0011 |

0100 |

0101 |

0110 |

0111 |

1000 |

1001 |

0000 |

|||||||||||

Рис.4 Временная диаграмма полученного счётчика.

- граница

одного полного цикла преобразованного

счётчика.

- граница

одного полного цикла преобразованного

счётчика.

3.2 Синтез рабочей схемы на основе отечественных интегральных

микросхем.

При выборе ИМС рекомендуется воспользоваться справочной литера-турой, список которой приведён в конце данного пособия.

Необходимо выбрать следующие ИМС и триггеры:

три схемы НЕ (инверторы);

схема 4И;

четыре D-триггера;

Выбраны:

- схемы НЕ: микросхемы типа ЛН1, ЛН2, ЛН3, ЛН5 (графическое обозначение микросхем ЛН дано на рис.5.)

-

J1

J11

1

2

Y1

J2

3

1

4

Y2

J3

5

1

6

Y3

J4

9

1

8

Y4

J5

11

1

10

Y5

J6

13

1

12

Y6

14-питание

7-общий

Рис.5 Условное обозначение и цоколевки микросхем типа ЛН.

- схема 4И: микросхемы типа ЛИ6 (графическое обозначение микросхем ЛИ дано на рис.6.)

-

A1

1

B1

2

&

6

A1B1C1D1

C1

4

D1

5

A2

9

B2

10

&

8

A2B2C2D2

C2

12

D2

13

14-питание

7-общий

Рис.6 Условное обозначение и цоколевки микросхем типа ЛИ.

- четыре схемы D-триггера: микросхемы типа ТМ2 (графическое обозначение триггеров ТМ2 дано на рис.7.)

-

R1

1

R

5

Q

TT

D1

2

D

C1

3

C

S1

4

S

6

_

Q

R2

13

R

9

Q

TT

D2

12

D

C2

11

C

S2

10

S

8

_

Q

14-питание

7-общий

Рис.7 Условное обозначение и цоколевки триггеров ТМ2.

Принципиальная схема счётной декады младших разрядов представлена на рис.8.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

Q1 |

Q2 |

Q3 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+U |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD1.1 |

|

|

|

|

|

|

DD2.1 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD1.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD3.1 |

|

|

|

|

|

|

DD3.2 |

|

|

|

|

|

|

DD3.3 |

|

|

|

|

|

|

DD3.4 |

|

|

|

||||

|

|

|

|

|

R |

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

TT |

|

|

|

|

|

|

TT |

|

|

|

|

|

|

TT |

|

|

|

|

|

|

TT |

|

|

|

||||

|

|

|

|

|

D |

|

|

|

|

|

|

D |

|

|

|

|

|

|

D |

|

|

|

|

|

|

D |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

C |

|

|

|

|

C |

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

S |

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.8 Принципиальная схема счётной декады на основе отечественных ИМС.

3.3 Синтез рабочей схемы с использованием специальных ИМС.

Существуют специальные ИМС, которые заведомо выполняют необходи-мые нам операции. В нашем случае весьма хорошо подходят микросхемы типа ИЕ2 и ИЕ4. Цоколевка и условное графическое обозначение микро-схем типа ИЕ2 и ИЕ4 приведена на рис.9.

-

ИЕ2

14

C1

CT10

ИЕ4

1

C2

1

12

14

C1

1

12

CT10

2

&

2

9

1

C2

2

11

3

R

4

8

6

&

4

9

6

&

8

11

7

R

8

8

7

R9

5-питание

10-общий

5-питание

2,3,4,13-свободные

10-общий

4,13-свободные

Рис.9 Цоколевка и условное обозначение микросхем типа ИЕ2 и ИЕ4.

Принципиальная схема на базе выбранных специальных ИМС представлена на рис.10.

???

Рис.10 Принципиальная схема счётной декады на основе специальных ИМС.

4.Выводы по полученным результатам.

@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@