ПРАКТИЧЕСКОЕ ЗАНЯТИЕ

Построение блока памяти микропроцессорной системы.

1 Цель работы

- закрепление теоретических знаний о построении МПСУ;

- получение навыков построения блоков памяти МПСУ;

- привитие навыков работы со справочной литературой;

2 Краткие теоретические сведения

Содержание работы связано с построением интерфейса микропроцессора (МП) с блоком запоминающих устройств (ЗУ), состоящего из оперативного запоминающего устройства (ОЗУ) и постоянного запоминающего устройства (ПЗУ).

Последовательность разработки блока ЗУ:

Рассмотрим содержание первого этапа разработки блока ЗУ. Пусть необходимо разработать блок ЗУ заданной емкости N байт и форматом входных - выходных данных в n бит.

При выборе типа микросхем ЗУ необходимо стремиться к тому, чтобы их организация N1 x n1 (байт x бит) была кратна соответственно N и n , а быстродействие соответствовало бы быстродействию процессора.

Требуемое число микросхем М для построения блока ЗУ определяется в соответствии с выражением:

M = (N x n)/(N1 x n1) = M1 x m, (1)

где M1 - число групп микросхем с одинаковым адресом в адресном пространстве блока ЗУ;

m - число микросхем в группе.

Например, для блока ЗУ 16 Кбайт x 16 бит можно выбрать микросхемы с организацией 2 Кбайт x 8 бит, тогда

M = (16 Кбайт x 16 бит)/( 2 Кбайт x 8 бит) = 8 x 2, (2)

При реализации второго и третьего этапов, связанных с распределением линий шины адреса, вся совокупность линий адреса разделяется на три множества L1 , L2 и L3. Линии шины адреса, входящие в данные множества, имеют следующие назначения:

L1 - множество разрядов шины адреса, подключаемых непосредственно к адресным входам микросхем ЗУ;

L2 - множество разрядов шины адреса, подключаемых к входам дешифратора адреса для выбора каждой группы микросхем;

L3 - множество разрядов шины адреса, подключаемых ко входам селектора адреса для блокирования дешифратора адреса.

Количества линий шины адреса, входящих в множества L1 , L2 и L3 определяются следующими выражениями:

L1 = log2 N1, (3)

L2 = ]log2 M1[, (4)

где ] [ - означает округление до ближайшего большего целого числа.

L3 = L- (L2 + L1), (5)

где L – число разрядов шины адреса.

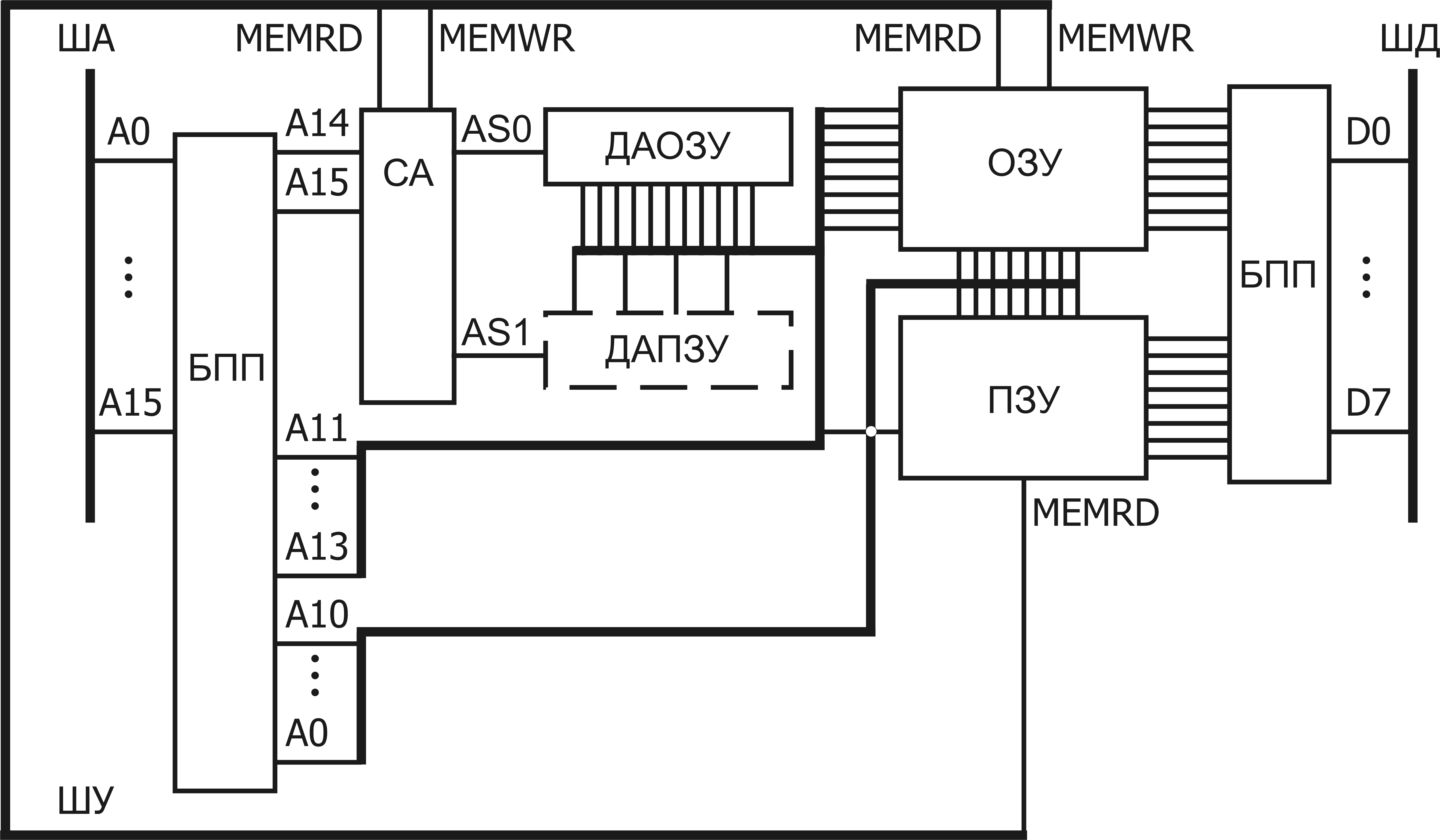

В разрабатываемом блоке память подключена к микропроцессору (МП) посредством трех шин: шины данных (ШД), шины адреса (ША) и шины управления (ШУ). При обращении к памяти МП выставляет по ША адрес ячейки памяти (ЯП), а по ШУ - сигнал MEMRD в цикле чтения памяти или MEMWR в цикле записи. Причем эти сигналы управления активно низкие и одновременно никогда не могут быть активными. В цикле чтения информация передается по ШД из памяти в МП, а в цикле записи - из МП в память. Если же к памяти обращения нет, то ее выходы отключены от ШД. Описанный алгоритм работы памяти можно реализовать при помощи схемы селектора адреса, которая входит в состав разрабатываемого блока. Для управления работой селектора адреса используем сигналы MEMWR и MEMRD, т.е определенный блок (все микросхемы ОЗУ или все микросхемы ПЗУ) выбирается низким уровнем сигнала. Селектор адреса вырабатывает сигналы AS0 и AS1, при обращении к ПЗУ и ОЗУ, соответственно. При этом оба этих сигнала активно низкие. Сигналы AS0 или AS1 только тогда будут выбирать один из блоков памяти, когда один из сигналов MEMWR или MEMRD будет активным низким. Если же оба сигнала будут активно высокими, то обращение к памяти будет запрещено.

При реализации третьего этапа выбирается дешифратор с L2 входами 2L2 выходами, которые подключаются к входам "выбор микросхемы" соответствующей микросхемы ЗУ. L3 линий адресов подключаются к селектору адреса, выходы которого AS0 и AS1 подсоединены соответственно к входу "выбор микросхемы" для дешифратора адреса ОЗУ и ПЗУ соответственно.

Рассмотрим пример построения блока ЗУ объемом 16 Кбайт x 8 бит, из которых 2 Кбайт занимает ПЗУ, а 14 Кбайт - ОЗУ. Для ПЗУ отведем адреса в диапазоне 0000 - 07FF, а ОЗУ - 0800 - FFFF.

В качестве элементной базы выберем микросхемы КР556РТ7 для ПЗУ и К573РУ10 для ОЗУ, имеющие организацию 2 Кбайт x 8 бит. Тогда для построения данного блока ЗУ необходимо взять одну микросхему КР556РТ7 и семь микросхем К573РУ10, т.е. M1 = 8 и m = 1. При этом распределение линий шины адреса будет иметь вид:

![]()

Рисунок

1 – Распределение линий шины адреса

Поскольку в данный блок ЗУ входит восемь микросхем, то для их выбора необходимо использовать восемь адресов, для кодирования которых используются разряды 11 - 13 шины адреса, подаваемые на дешифратор. В качестве дешифратора ОЗУ выберем микросхему К555ИД7. Поскольку в данном случае блок ПЗУ состоит всего из одной микросхемы, то его выбор можно осуществлять непосредственно сигналом AS0.

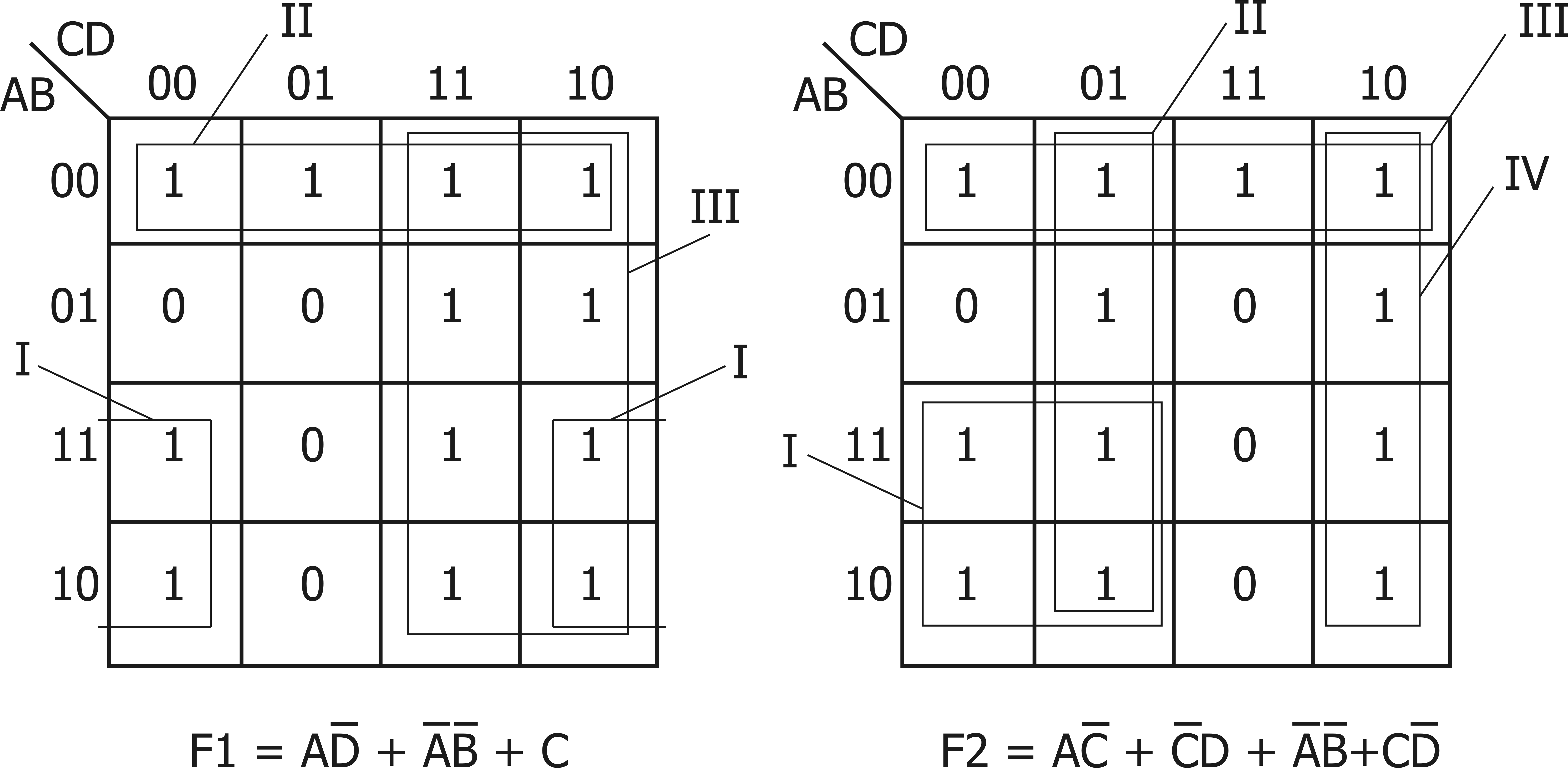

Так как выбор между блоками ПЗУ и ОЗУ осуществляется разрядами адреса (А14, А15), будем использовать эти адреса для синтеза схемы селектора адреса. Синтезируем схему селектора адреса с помощью карт Карно.

Таблица 1 – Таблица истинности селектора адреса

MEMRD (A) |

MEMWR (B) |

A14 (C) |

A15 (D) |

AS0 (F1) |

AS1 (F2) |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Рисунок

2 – Синтез селектора адреса при помощи

карт Карно

Рисунок

3 - Структурная схема блока памяти:

СА-селектор адреса; БПП – буферный

приемо-передатчик; ДАОЗУ, ДАПЗУ –

дешифратор адреса ОЗУ и ПЗУ соответственно.