- •Классификация Микропроцессоров.

- •Функциональная схема эвм

- •Понятие об архитектуре микропроцессоров.

- •Характеристики и особенности процессоров с микропрограммным управлением и с фиксированным набором команд. Risc процессоры

- •Общие принципы выполнения команд в мп. Временные интервалы.

- •Состав и назначение регистров в микропроцессорах.

- •Набор и характеристики команд в мп.

- •Аримфетико-логическое устройство. Блок управления и синхронизации.

- •Организация стековой памяти

- •Регистровый и косвенно-регистровый методы адресации на примере Электроники-60.

- •Режим адресации с автоувеличением и косвенная адресация с автоувеличением на примере Электроники 60.

- •Режим адресации с автоуменьшением и косвенная адресация с автоуменьшением на примере Электроники 60

- •Индексные методы адресации на примере электроники 60.

- •Методы адресации с использованием программного счетчика в мЭвм электроника 60.

- •Методы адресации, используемые в микропроцессорах.

- •Характеристики команд пересылки данных в микропроцессорах.

- •Выполнение команд пересылки данных в мп

- •Характеристики команды преобразования данных в микропроцессоре.

- •Программирование на машинном языке.

- •Программирование на языке ассемблер.

- •Недостатки

- •Директивы и макрокоманды ассемблера

- •Понятие о прерываниях в микропроцессорах. Принципы организации обслуживания прерываний.

- •Структуры прямого доступа к памяти. Функции, выполняемые котроллером прямого доступа к памяти.

Характеристики и особенности процессоров с микропрограммным управлением и с фиксированным набором команд. Risc процессоры

По набору выполняемых команд, МП делятся на МП с гибкой и жесткой логикой.

МП с гибкой логикой:

Они же МП с микропрограммным управлением, имеют возможность модифицировать систему команд. За счет счет этого достигается максимальная производительность при решении частной задачи.

Это компенсируется высокой ценой и временем

МП с жесткой логикой:

CISC (англ. Complex Instruction Set Computing) — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

Нефиксированным значением длины команды.

Арифметические действия, кодируется в одной инструкции.

Небольшим числом регистров, каждый из которых выполняет строго определённую функцию.

RISC

Характерные особенности RISC-процессоров:

Фиксированная длина машинных инструкций (например, 32 бита) и простой формат команды.

Специализированные команды для операций с памятью — чтения или записи. Операции вида «прочитать-изменить-записать» отсутствуют. Любые операции "изменить" выполняются только над содержимым регистров (т.н. load-and-store архитектура).

Большое количество регистров общего назначения (32 и более).

Отсутствие поддержки операций вида "изменить" над укороченными типами данных - байт, 16-битное слово. Так, например, система команд DEC Alpha содержала только операции над 64-битными словами, и требовала разработки и последующего вызова процедур для выполнения операций над байтами, 16- и 32-битными словами.

Отсутствие микропрограмм внутри самого процессора. То, что в CISC процессоре исполняется микропрограммами, в RISC процессоре исполняется как обыкновенный (хотя и помещенный в специальное хранилище) машинный код, не отличающийся принципиально от кода ядра ОС и приложений. Так, например, обработка отказов страниц в DEC Alpha и интерпретация таблиц страниц содержалась в так называемом PALCode (Privileged Architecture Library), помещенном в ПЗУ. Заменой PALCode можно было превратить процессор Alpha из 64-битного в 32-битный, а также изменить порядок байт в слове и формат входов таблиц страниц виртуальной памяти.

Сокращенный набор команд (от 80 до 150 команд).

Большинство команд выполняется за 1 такт.

Большое количество регистров общего назначения.

Наличие жестких многоступенчатых конвейеров.

Все команды имеют простой формат, и используются немногие способы адресации.

Наличие вместительной раздельной кэш-памяти.

Применение оптимизирующих компиляторов, которые анализируют исходный код и частично меняют порядок следования команд.

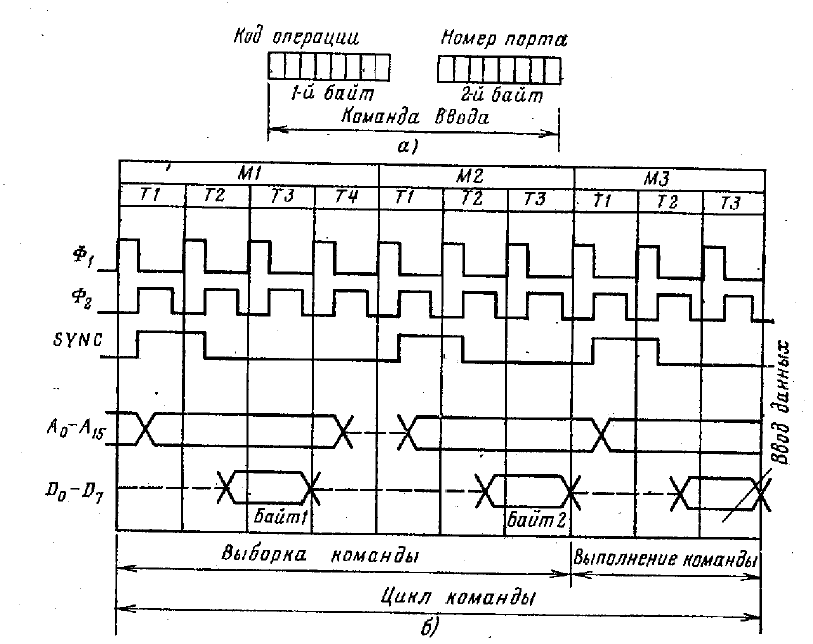

Общие принципы выполнения команд в мп. Временные интервалы.

Выполнение любой команды состоит из трех фаз.

Фаза выборки инструкции команды.

При подаче rst/после включения должен быть задан адрес стартующей ячейки – той, в которой находится первая инструкция. Этот адрес вшивается при изготовлении процессора.

СУиС подает сигнал чтения в память, на шине адреса выставлен первый адрес, на шине данных появляются данные.

Содержимое ячейки переносится во внутреннюю память процессора. PC увеличивается на 1.

Фаза дешифрации.

Полученная информация из регистра команд переносится в дешифратор команд, который в свою очередь связан со СУСиС.

Наступает фаза выполнения команды: выполняется нужное действие = задействуется АЛУ и тп.

Синхронизация бывает двухфазной (8080), как на рисунке и однофазной.

Временные интервалы:

Машинный такт – минимальный интервал времени, за который выполняется микрооперация.

Машинный цикл – минимальный интервал времени, необходимый дл обращения к системной шине ( ВУ, внешней памяти).

Командный цикл – время, требуемое, для исполнения команды.