- •Реализуем логическую функцию, заданную в лабораторной работе № 1. Для этого реализуем дешифратор 4×16 на основе двух дешифраторов 3×8 при помощи каскадирования.

- •Синтезируем дешифратор из 1 в 2, низкого уровня, входы разрешения прямой и инверсный на основе дискретных логических элементов.

- •Задание №2.

- •Задание №3.

- •Синтезируем шифратор из 4 в 2 низкого уровня с выходом разрешения на основе дискретных элементов.

Синтезируем дешифратор из 1 в 2, низкого уровня, входы разрешения прямой и инверсный на основе дискретных логических элементов.

Составим таблицу истинности дешифратора:

Таблица № 4

E2 |

E1 |

A |

y1 |

y0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

× |

× |

1 |

1 |

× |

0 |

× |

1 |

1 |

Из таблицы запишем значения y1, y0:

![]()

На основе полученных уравнений составим схему дешифратора из 1 в 2, низкого уровня, входы разрешения работы прямой и инверсный, на дискретных элементах:

Рисунок 5 – Схема дешифратора из 1 в 2

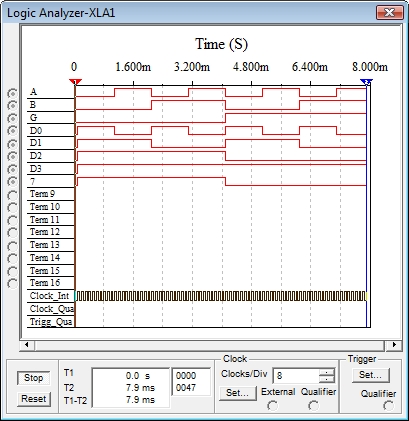

Временные диаграммы данного дешифратора имеют следующий вид:

Рисунок 6 – Временные диаграммы дешифратора

Условное графическое обозначение синтезированного дешифратора:

X0

1

0 1

DC

E1

E2

X1

E

Задание №2.

Соберем схему для анализа работы мультиплексора и построим временные диаграммы, для этого выберем мультиплексор MUX_4TO1 и соединим его адресные входы и вход разрешения работы с генератором слов, а выходы с цифровым анализатором.

Рисунок 7 – Схема анализа работы мультиплексора

Рисунок 8 – Временные диаграммы работы мультиплексора

Составим таблицу истинности для данного мультиплексора

Таблица № 5

i |

E |

A1 |

A0 |

Y |

0 |

0 |

0 |

0 |

D0 |

1 |

0 |

0 |

1 |

D1 |

2 |

0 |

1 |

0 |

D2 |

3 |

0 |

1 |

1 |

D3 |

4 |

1 |

× |

× |

0 |

Синтезируем мультиплексор из 2 в 1 с двумя прямыми входами разрешения работы на основе дискретных элементов.

Составим таблицу истинности данного мультиплексора, получим:

Таблица № 6

i |

E2 |

E1 |

A0 |

Y |

0 |

1 |

1 |

0 |

D0 |

1 |

1 |

1 |

1 |

D1 |

2 |

0 |

0 |

× |

0 |

На основе таблицы № 6 соберем схему мультиплексора из 2 в 1 с двумя прямыми входами разрешения работы на основе дискретных элементов.

Рисунок 9 – Схема мультиплексора из 2 в 1

Временные диаграммы работы данного мультиплексора представлены на рисунке 10.

Рисунок 10 – Временные диаграммы мультиплексора из 2 в 1

Условное графическое обозначение синтезированного мультиплексора имеет вид:

E2

X0

X1

0

1

MUX

E1

A0

A0

E1

E2

На основе мультиплексора из 8 в 1 синтезируем схему из лабораторной работы № 1.

Таблица истинности заданного мультиплексора имеет вид:

Таблица №7

i |

E |

A2 |

A1 |

A0 |

Y |

0 |

0 |

0 |

0 |

0 |

D0 |

1 |

0 |

0 |

0 |

1 |

D1 |

2 |

0 |

0 |

1 |

0 |

D2 |

3 |

0 |

0 |

1 |

1 |

D3 |

4 |

0 |

1 |

0 |

0 |

D4 |

5 |

0 |

1 |

0 |

1 |

D5 |

6 |

0 |

1 |

1 |

0 |

D6 |

7 |

0 |

1 |

1 |

1 |

D7 |

8 |

1 |

× |

× |

× |

0 |

Произведем процедуру синтеза схемы, для этого составим следующую таблицу:

Таблица № 8

i |

D |

C |

B |

A |

Y |

|

|

0 |

0 |

0 |

0 |

0 |

1 |

|

|

1 |

0 |

0 |

0 |

1 |

1 |

||

2 |

0 |

0 |

1 |

0 |

1 |

|

|

3 |

0 |

0 |

1 |

1 |

0 |

||

4 |

0 |

1 |

0 |

0 |

0 |

|

|

5 |

0 |

1 |

0 |

1 |

0 |

||

6 |

0 |

1 |

1 |

0 |

1 |

|

|

7 |

0 |

1 |

1 |

1 |

0 |

||

8 |

1 |

0 |

0 |

0 |

0 |

|

|

9 |

1 |

0 |

0 |

1 |

1 |

||

10 |

1 |

0 |

1 |

0 |

0 |

|

|

11 |

1 |

0 |

1 |

1 |

0 |

||

12 |

1 |

1 |

0 |

0 |

0 |

|

|

13 |

1 |

1 |

0 |

1 |

1 |

||

14 |

1 |

1 |

1 |

0 |

1 |

|

|

15 |

1 |

1 |

1 |

1 |

0 |

||

Т.к. число адресных входов мультиплексора

на 1 меньше числа переменных функции, в

таблице № 8 строки были сгруппированы

по 2 и записаны настроечные сигналы

![]() .

.

На основе полученной таблицы, составим схему:

Рисунок 11 – Схема на мультиплексоре из 8 в 1

Рисунок 12 – Временные диаграммы схемы

Из временных диаграмм видно, что выходные значения схемы идентичны таблице истинности исходной функции, следовательно, схема синтезирована, верно.