- •Типы шин.

- •Компьютерная шиина (англ. computer bus) в архитектуре компьютера — подсистема, служащая для передачи

- •Используемые в настоящее время шины отличаются по разрядности, способу передачи сигнала (последовательные или

- •Шинная архитектура

- •Разрядность шины адреса определяет адресное пространство процессора, т.е. количество ячеек оперативной памяти, которые

- •Шина управления

- •Система шин ЭВМ

- •Шинауправле

- •Шинауправле

- •Шинауправле

- •Типичная структура микропроцессорной системы

- •Архитектура компьютера определяет принцип действия, информационные связи и взаимное соединение основных логических узлов

- •Типы обмена информацией по шинам

- •В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив

- •Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки

- •Системная

- •Back side bus (BSB) — шина кэш- памяти второго уровня в процессорах с

- •Front Side Bus (FSB, системная шина) — шина, обеспечивающая соединение между x86- и

- •Частоты, на которых работают центральный процессор и FSB, имеют общую опорную частоту, и

- •Direct Media Interface, сокр. DMI — последовательная шина, разработанная фирмой Intel для соединения

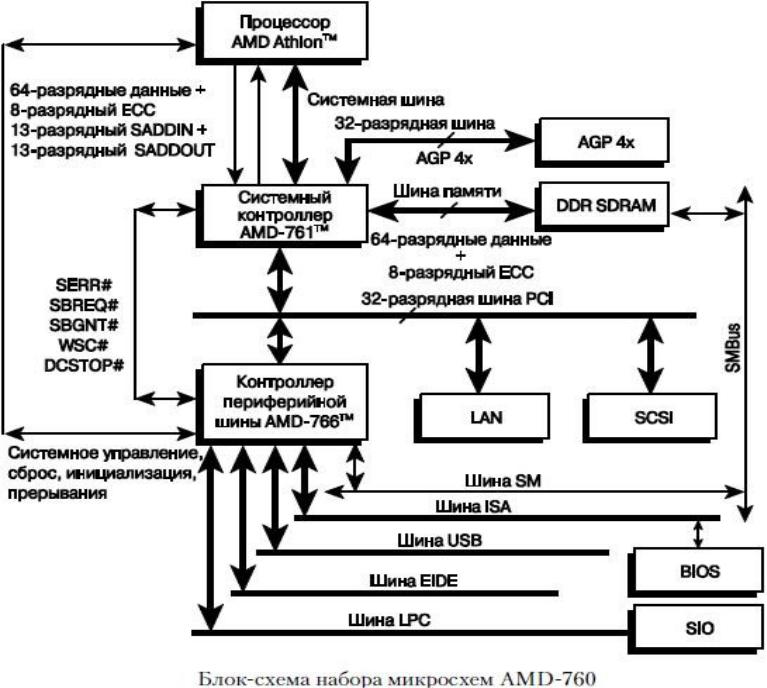

- •HyperTransport (ранее известная как Lightning Data Transport (LDT)) —

- •Шина HyperTransport основана на передаче пакетов. Каждый пакет состоит из 32- разрядных слов,

- •Пакеты HyperTransport передаются по шине последовательно. Увеличение пропускной способности влечёт за собой увеличение

- •Intel QuickPath Interconnect или просто QuickPath, сокр. QPI (ранее Common System Interface, CSI)

- •Каждое соединение шины QuickPath состоит из пары односторонних каналов, каждый из которых физически

- •MultiDrop шина (MDB) является компьютерной шиной, в которой все компоненты подсоединены в одной

- •Шина расширения — компьютерная шина, которая используется на системной карте компьютеров или промышленных

- •Локальная шина

- •Шина PCI

- •Создатели PCI отказались от традиционной концепции, введя еще одну шину между процессором и

- •Шина PCI добавляет к традиционной конфигурации шин еще один уровень. При этом обычная

- •В спецификации PCI определено три типа системных плат, каждая из которых разработана для

- •Обратите внимание, что универсальная плата PCI может устанавливаться в разъем, предназначенный для любой

- •PCI Express, или PCIe, или PCI-E (также известная как 3GIO for 3rd Generation

- •В течение 2001 года специалисты группы компаний, получившей название Arapahoe Work Group (изначально

- •Основные особенности PCI Express таковы:

- •Особенностью архитектуры шин предыдущих поколений является параллельная компоновка, при которой биты данных одновременно

- •В шине PCI Express используется разработанная IBM схема кодирования “8–10”, предусматривающая автосинхронизацию сигналов

- •PCI-Express пока не заменила полностью шину PCI и все остальные интерфейсы, и вряд

- •Гибкие удлинители и переходники для шин PCI Express x16,x8,x4,x1, PCI32, PCI64, PCI-

- •PCIEXP1-X1, PCIEXP4-X1, PCIEXP8-X1, PCIEXP16-X1, PCIEXP16-RX1, PCIEXP16-CE1, - Удлинители для шин PCI Express X1,

- •PCIEXP1-X2, PCIEXP4-X2, PCIEXP8-X2, PCIEXP16-X2, PCIEXP16-RX1, - Удлинители для шин PCI Express X1, X4,

- •PCIEXP1-X3, PCIEXP4-X3, PCIEXP8-X3 и PCIEXP16-X3 - Удлинителидля шин PCI Express X1, X4, X8

- •PCIEXP1-SX, PCIEXP4-SX, PCIEXP8-SX и PCIEXP16-SX- Удлинители для шин PCI Express X1, X4, X8

- •PCIEXP4-SX-4/1, PCIEXP8-SX-8/4,PCIEXP16-SX-16/8и PCIEXP16-SX-16/1 - Конвертеры для шин PCI Express, предназначенные для установки плат

- •PCIEXP16-SL057

- •Плата адаптер с PCI на PCI-Express 16x.

- •Угловой переходник для шины PCI-Express 16Х

- •Гибкий удлинитель слота PCI 32

- •Гибкий адаптер PCI-Express 8x на PCI-Express 16х

- •Райзер карта расширитель двух слотов PCI

- •Гибкий удлинитель слота PCI-X / PCI 64

- •Гибкий удлинитель слота PCI-X / PCI 64

- •Гибкий удлинитель для разъма AGP

- •Адаптер для тестирования плат PCI Express 16X

- •PCI-Express 4.0 обеспечит передачу 16 ГТ/с

Шинауправле |

Отпериферийныхустройств |

Порт- |

|

|

входы |

|

Микропроцесор, |

|

управлениеиАЛУ |

Адреснаяши |

Память |

|

програм |

|

Память |

|

даных |

|

Порт- |

|

выходы |

|

Кпериферийнымустройствам |

Шина управления - координирует работу всех устройств. |

|

Типичная структура микропроцессорной системы

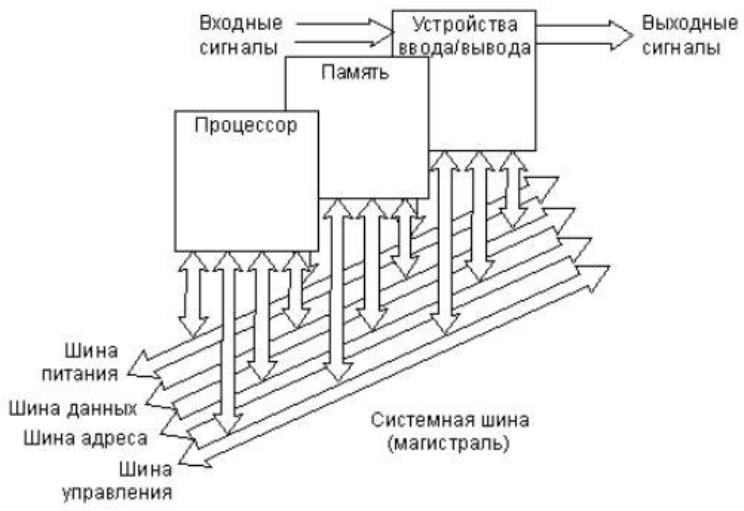

Системная магистраль включает в себя четыре основные шины нижнего уровня:

шина адреса (Address Bus);шина данных (Data Bus);

шина управления (Control Bus);шина питания (Power Bus).

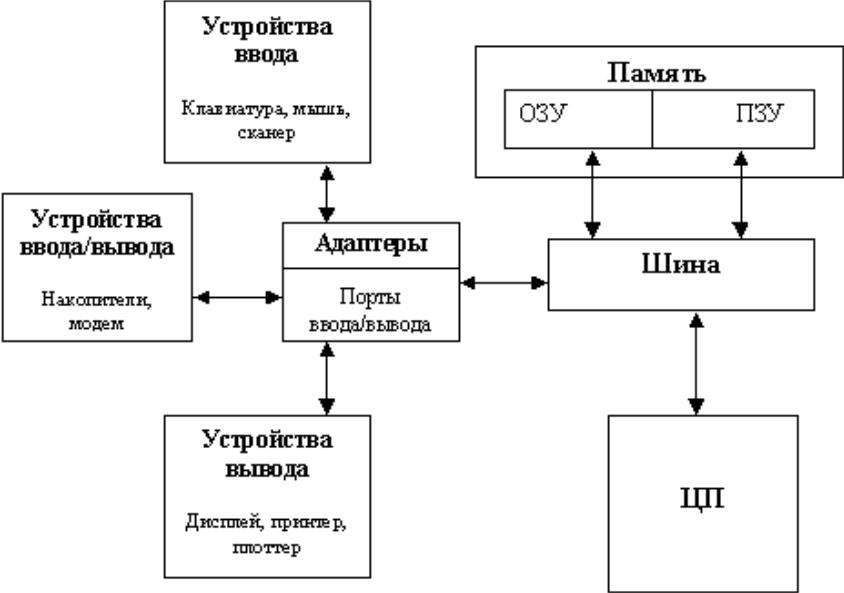

Архитектура компьютера определяет принцип действия, информационные связи и взаимное соединение основных логических узлов компьютера, к которым относятся:

•центральный процессор;

•основная память;

•внешняя память;

•периферийные устройства.

Типы обмена информацией по шинам

В шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий — логическому нулю. При отрицательной логике — наоборот.

Сигналы шины управления также могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще).

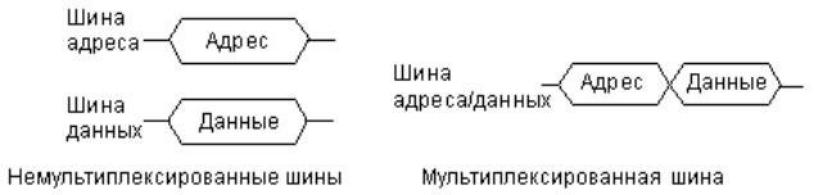

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления.

Мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена. По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

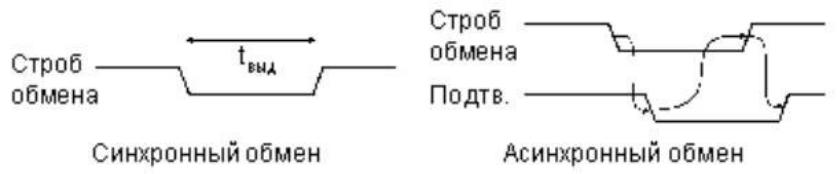

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными. Чаще всего в магистрали используются два различных строба обмена:

·Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных;

·Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который буде прочитан процессором.

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения:

1.При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

2.При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки — отсутствие гарантии, что исполнитель выполнил требуемую операцию, а также высокие требования к быстродействию исполнителя.

Достоинства асинхронного обмена — более надежная пересылка данных, возможность работы с самыми разными по быстродействию исполнителями. Недостаток — необходимость формирования сигнала подтверждения всеми исполнителями, то есть дополнительные аппаратурные затраты.

Системная

шина  Процессоры

Процессоры

Внутренние

Ноутбуки

Ноутбуки  Накопители

Накопители

Периферия

Универсальны

е

Компьютерные шины  Шина адреса • Шина данных • Шина управления •Шина питания

Шина адреса • Шина данных • Шина управления •Шина питания

BSB • FSB • DMI • HyperTransport • QPI

AGP • EISA • ISA • LPC • MBus • MCA • NVLink • NuBus • PCI • PCIe • PCI- X • Q-Bus • SBus • SMBus • VLB • VMEbus • Zorro III

ExpressCard • MXM • PC Card

ST-506 • ESDI • ATA • eSATA • Fibre Channel • HIPPI • NVMe • SAS • SATA • SCSI

1-Wire • ADB • I²C • IEEE 1284 (LPT) • IEEE

1394 (FireWire) • Multibus • PS/2 • UART (RS-232, RS- 485) • SPI • USB • Игровой порт

Futurebus • InfiniBand • Omni-Path • QuickRing • SCI • RapidIO • IEEE- 488 • Thunderbolt (Light Peak)

Back side bus (BSB) — шина кэш- памяти второго уровня в процессорах с

двойной независимой шиной (англ. DIB — dual independed bus).

Для связи с контроллером памяти предназначена FSB (front side bus), работающая в качестве магистрального канала между процессором и чипсетом.