Контрольная ВМИС вар 8

.docxЗадание 1. Устройство микропроцессора.

-

Разрядность, быстродействие.

-

Структура памяти, объем основной памяти.

-

Система команд.

КР580ВМ80А — 8-разрядный микропроцессор, полный аналог микропроцессора Intel i8080A (1974 год). Является основным элементом микропроцессорного комплекта серии КР580. Разработка Киевского НИИ микроприборов. В различных вариантах выпускался с конца 1970-х годов (наиболее раннее из упоминаний — использован в прототипе компьютера СМ1800, 1979 год) до середины 1990-х годов.

Микросхема

КР580ВМ80А представляет собой 8-разрядное

центральное процессорное устройство

(ЦПУ) параллельной обработки данных.

Устройство не обладает возможностью

аппаратного наращивания разрядности

обрабатываемых данных, но позволяет

осуществлять это программным способом.

Структурная схема КР580ВМ80А представлена

на рисунке 1.

Рисунок 1- Структурная схема КР580ВМ80А.

Основные параметры МП КР580ВМ80А

система счисления — двоичная;

форма представления чисел — с фиксированной запятой;

разрядность шины данных — 8;

разрядность шины адреса — 16;

число команд — базовых 78, общее число — 244;

максимальная емкость адресуемой памяти — 64 Кбайта;

максимальное число адресуемых внешних устройств

ввода/вывода — 256/256;

число уровней прерывания — 8;

тактовая частота, МГц <= 2,5;

количество операций в секунду — 0,5*106 ;

длительность цикла, мкс — 1,6;

напряжение питания, В — +5; 5; +12;

потребляемая мощность, Вт — 1,25 – 1,5.

емкость оперативного запоминающего устройства (ОЗУ) – 1 Кбайт;

емкость постоянного запоминающего устройства (П3У) – 2 Кбайта;

Система команд — соглашение о предоставляемых архитектурой средствах программирования, а именно: определённых типах данных, инструкций, системы регистров, методов адресации, моделей памяти, способов обработки прерываний и исключений, методов ввода и вывода.

Система команд представляется спецификацией соответствия (микро)команд наборам кодов (микро)операций, выполняемых при вызове команды, определяемых (микро)архитектурой системы. (При этом, на системах с различной (микро)архитектурой может быть реализована одна и та же система команд.

Базовыми командами являются, как правило, следующие:

- арифметические, например «сложения» и «вычитания»;

- битовые, например «логическое и», «логическое или» и «логическое не»;

- присваивание данных, например «переместить», «загрузить», «выгрузить»;

- ввода-вывода, для обмена данными с внешними устройствами;

- управляющие инструкции, например «переход», «условный переход», «вызов подпрограммы», «возврат из подпрограммы».

Задание 2. Передать управление программе (табл. 1), вычисляющей выражение (а + b) - с при а = -5, b = 9, с = 2, размещенных в ячейках 0820, 0821 и 0822 соответственно, с остановом по адресу 080A.

|

Адрес |

Содержимое (машинный код) |

Ассемблерный код (мнемокод) |

Комментарий |

|

0800 |

21 |

LXI H, 0820 |

Занесение адреса числа а в пару регистров |

|

0801 |

20 |

|

HL |

|

0802 |

00 |

|

|

|

0803 |

7Е |

MOV A, M |

Пересылка числа а из ячейки памяти в аккумулятор |

|

0804 |

23 |

INX H |

Инкриминирование содержимого регистра HL |

|

0805 |

86 |

ADD M |

Сложение а + в |

|

0806 |

23 |

INX H |

Инкриминирование содержимого регистра HL |

|

0807 |

96 |

SUB M |

Вычитание (а + в) – с |

|

0808 |

23 |

INX H |

Инкриминирование содержимого регистра HL |

|

0809 |

77 |

MOV M, A |

Пересылка содержимого аккумулятора в ячейки 0823 |

|

080А |

76 |

HLT |

Останов. |

|

... |

|

|

|

|

0820 |

FB |

A |

|

|

0821 |

09 |

B |

Числовая информация |

|

0822 |

02 |

C |

|

Задание 3.

Вариант 21

Записать в последовательные ячейки ОЗУ микропроцессора 10 целых чисел, положительных и отрицательных (количество тех и других по выбору, в соответствии с задачей), это массив a1, a2, … , a10.

Найти количество отрицательных элементов массива.

Даны числа : -4, 7, 3, -8, 2, -7, 9, -10, 6, 1.Отрицательные записаны в дополнительном коде. По количеству отрицательных элементов массива 4.

Программа 3 [0800h-0824h]

|

Адрес |

Код |

Мнемокод |

Комментарий |

|

0800 |

21 |

LXI H,d16 |

Адресация к памяти |

|

0801 |

1A |

|

Адрес |

|

0802 |

08 |

|

HL |

|

0803 |

86 |

ADD M |

Сложение регистра А с памятью |

|

0804 |

CC |

CZ adr |

Массивы закончились, вывод результата |

|

0805 |

12 |

|

Адрес |

|

0806 |

08 |

|

подпрограммы |

|

0807 |

FC |

CM adr |

Если массив отрицательный добавляется 1 |

|

0808 |

10 |

- |

Адрес |

|

0809 |

08 |

NOP |

подпрограммы |

|

080A |

23 |

INX H |

Инкремент HL |

|

080B |

3E |

MVI A, d8 |

Обнуление регистра А |

|

080C |

00 |

NOP |

|

|

080D |

F4 |

CP adr |

Повторение операции со следующим массивом |

|

080E |

03 |

INX B |

Адрес |

|

080F |

08 |

NOP |

Возврата |

|

0810 |

04 |

INR B |

Считается количество отрицательных массивов |

|

0811 |

C9 |

RET |

Безусловный выход |

|

0812 |

78 |

MOV A, B |

Занесение значения регистра В в А |

|

0813 |

32 |

STA adr |

Вывод результата по адресу |

|

0814 |

17 |

RAL |

Адрес |

|

0815 |

08 |

NOP |

Результата |

|

0816 |

76 |

HLT |

Стоп |

|

0817 |

04 |

INR B |

Результат |

|

0818 |

08 |

NOP |

|

|

0819 |

08 |

NOP |

|

|

081А |

FC |

CM adr |

Массивы из условия |

|

081В |

07 |

RLC |

|

|

081С |

03 |

INX B |

|

|

081D |

F8 |

RM |

|

|

081E |

02 |

STAX B |

|

|

081F |

F9 |

SPHL |

|

|

0820 |

09 |

DAD B |

|

|

0821 |

F6 |

ORI d8 |

|

|

0822 |

06 |

MVI B, d8 |

|

|

0823 |

01 |

LXI B, d16 |

|

|

0824 |

08 |

NOP |

|

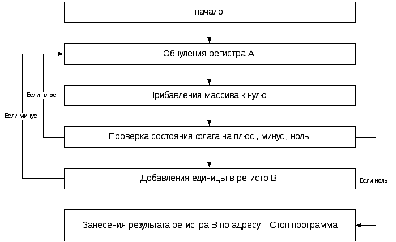

В программе использовали регистр В для подсчета результата, пару регистров HL , как ячейка памяти. Были применены условные команды перехода по состоянию флага

(плюс, минус и ноль ).

Работа программы: по адресу 001А – 0023 занесли значения массивов. Прибавляем значение первого массива к АК (к 0) проверяем значение по состоянию флага на положительное , отрицательное число либо содержимое АК равно ноль. Если число положительное берем следующий массив обнуляем АК и повторяем операцию. Если число отрицательное прибавляем в регистр В единицу , начальное его значение ноль. Адрес подпрограммы 0010 – 0011.Повторяем операцию со следующим массивом, АК обнуляется.

Если АК равен 0, то это говорит ,что массивы закончились, по условию массив не равен нулю, переходим в подпрограмму 0012 - 0015, где значение регистра В записываем в регистр А и передаем в ячейку памяти этот результат по адресу 0017. Программа останавливается.