- •Лабораторна робота № 1 Тема: структура учбової мікропроцесорної лабораторії, клавіатура керування, індикація

- •Коротка інформація

- •Порядок виконання лабораторної роботи

- •Лабораторна робота № 2 Тема: пам’ять учбової мікропроцесорної лабораторії, дослідження виконання програм в покроковому I автоматичному режимах

- •Коротка інформація

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 3 Тема: дослідження програмно-доступних регістрів мікропроцесора кр580ик80

- •Коротка інформація

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 4 Тема: вивчення команд пересилання даних.

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 5 Тема: вивчення арифметичних команд

- •Коротка інформація

- •Індивідуальні завдання

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 6 Тема: вивчення логічних команд

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 7 Тема: вивчення команд переходів

- •Коротка інформація

- •Індивідуальні завдання

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 8 Тема: вивчення команд введення / виведення, керування і рестарту

- •Коротка інформація

- •Індивідуальне завдання

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 9 Тема: вивчення зв’язків мікролабораторії із зовнішнім середовищем

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 10 Тема: керування клавіатурою і індикаторами мікро лабораторії

- •Коротка інформація

- •Індивідуальні завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 11 Тема: програмування тимчасових затримок

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 12 Тема: програмне керування пристроями введення / виведення

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 13 Тема: динамічне керування об’єктами введення / виведення

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 14 Тема: імітаційне моделювання передньої панелі вимірювального приладу з вбудованим мп

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 15 Тема: тестування пам’яті мікропроцесорної системи

- •Коротка інформація

- •Індивідуальні завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 16 5 Тема: макет мікропроцесорної системи охоронної сигналізації на автомобілі

- •Коротка інформація Постановка задачі

- •Інженерна інтерпретація

- •Оцінка системи

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Додаток. Система команд 8–розрядного однокристального мікропроцесора к580ик80а.

- •Література

Індивідуальні завдання

1. Скласти програму на основі команд арифметичних операцій з використанням команд пересилань. Програма повинна показати роботу всіх типів команд арифметики.

2. Закодувати програму і занести її в таблицю, аналогічну таблиці 3.1.

Порядок виконання лабораторної роботи

Завантажити в пам’ять мікро лабораторії програми, що розглянуті в теоретичному розділі, і перевірити правильність їх роботи.

Завантажити індивідуальну програму і здійснити її виконання в покроковому режимі. Заповнити таблицю, вказуючи стан кожного з регістрів, що використовуються, на кожному кроці виконання.

При читанні вихідних даних і запису результатів в пам’ять здійснити контроль вмісту цих вічок. Результати занести в таблицю.

Здійснити циклічне виконання програми задану кількість разів з зупинкою за фіксованою адресою. Для цього за адресами 83F0 і 83F1 занести молодший і старший байти адреси команди, що контролюється, а за адресою 83F2 — кількість проходів.

Зробити висновки по роботі.

Контрольні питання

Відмінність команд арифметичних операцій без врахування і з врахуванням переносу.

Призначення команд зміни на 1 вмісту пар регістрів.

Як виглядає алгоритм інкрементування пари регістрів, реалізований за допомогою команд INR r ?

Як виконуються команди подвійного додавання?

Як виконується додавання операндів довжиною понад один байт?

Призначення безпосередніх арифметичних команд.

Лабораторна робота № 6 Тема: вивчення логічних команд

Мета: вивчити групу логічних команд, набути навичок складання програм з їх використовуванням.

Коротка інформація

Група логічних команд призначена для виконання операцій логічного перетворення інформації, яка розміщена в регістрах. До них відносяться операції зсуву, логічного «І», «АБО» та інші. Перелік команд та їх коди показані на рис. 6.1.

1. Логічні |

|

2. З безпосередніми даними |

|

4. Спеціальні |

||||||||||||||||

Мнемоніка |

Код |

|

Мнемоніка |

Код |

|

Мнемоніка |

Код |

|

Мнемоніка |

Код |

||||||||||

ANA «І» |

A |

A7 |

|

ORA «АБО» |

A |

B7 |

|

ADI |

# |

C6 |

|

DAA |

27 |

|||||||

B |

A0 |

|

B |

B0 |

|

ACI |

# |

CE |

|

CMA |

2F |

|||||||||

C |

A1 |

|

C |

B1 |

|

SUI |

# |

D6 |

|

STC |

37 |

|||||||||

D |

A2 |

|

D |

B2 |

|

SBI |

# |

DE |

|

CMC |

3F |

|||||||||

E |

A3 |

|

E |

B3 |

|

ANI |

# |

E6 |

|

|

|

|||||||||

H |

A4 |

|

H |

B4 |

|

XRI |

# |

EE |

|

|

|

|||||||||

L |

A5 |

|

L |

B5 |

|

ORI |

# |

F6 |

|

|

|

|||||||||

M |

A6 |

|

M |

B6 |

|

CPI |

# |

FE |

|

|

|

|||||||||

XRA « mod 2» |

A |

AF |

|

CMP «=? » |

A |

BF |

|

|

|

|

|

|

|

|||||||

B |

A8 |

|

B |

B8 |

|

|

|

|

|

|

|

|||||||||

C |

A9 |

|

C |

B9 |

|

3. Зсув |

|

|

|

|||||||||||

D |

AA |

|

D |

BA |

|

Мнемоніка |

Код |

|

|

|

|

|||||||||

E |

AB |

|

E |

BB |

|

RLC |

|

07 |

|

|

|

|||||||||

H |

AC |

|

H |

BC |

|

RRC |

|

0F |

|

|

|

|||||||||

L |

AD |

|

L |

BD |

|

RAL |

|

17 |

|

|

|

|||||||||

M |

AE |

|

M |

BE |

|

RAR |

|

1F |

|

|

|

|||||||||

Рис. 6.1. Логічні команди МП.

Якщо нема особливих вказівок при описі команди, то команди впливають на стан прапорців нуля, парності, знаку, переносу і допоміжного переносу відповідно стандартних правил.

Логічні команди операції «І» над вмістом акумулятора і регістра (ANA r) розміщують результат операції в регістрі А. При цьому скидається прапорець переносу C і встановлюється прапорець допоміжного переносу. Команда займає в пам’яті 1 байт. Зчитування її з пам’яті виконується за три перші такти циклу M1, а в такті Т4 команда виконується. Особливість команди ANA M полягає в тому, що операція «І» виконується з вмістом акумулятора і вмістом вічка пам’яті, адреса якого розміщена в парі регістрів H, L. Оскільки для зчитування з пам’яті операнду потрібен додатковий машинний цикл, то команда буде виконана за сім тактів. Операція «І» також може бути виконана над безпосереднім операндом за допомогою команди ANI #. Її результат також розміщується в регістрі акумулятора. Для зчитування команди потрібно два машинних цикли, або за сім тактів.

При виконанні команди «Виключаюче АБО» (сума за модулем 2) результат розміщується в акумуляторі. Для цих команд характерна очистка прапорців переносу і допоміжного переносу. Відрізняють групу команд XRA r, які виконуються за чотири такти, команду XRA M, що здійснює операцію над акумулятором і вмістом вічка пам’яті за адресою, яка міститься в парі регістрів H, L (два цикли, або сім тактів), і команду безпосередньої операції «Виключаюче АБО» XRI # (два цикли, або сім тактів). Особливу увагу треба приділити операції XRA A, за допомогою якої можна очистити акумулятор і прапорці переносу. Команда використовується програмістами для підготовки акумулятора і прапорців переносу перед виконанням арифметичних перетворень, коли є необхідність виконувати аналіз переповнень.

Для формування логічного байту на основі вмісту кількох регістрів (наприклад, виконання зчеплення бітів) застосовуються команди логічного додавання («АБО»). Команди ORA r забезпечують логічне додавання акумулятора з регістром r, причому скидаються прапорці основного та допоміжного переносів (один цикл і чотири такти). Команди ORA M і ORI # впливають на тригери переносу аналогічно і виконуються за два цикли, або сім тактів.

Порівняння вмісту акумулятора і операнду, яким може бути вміст регістра, вічка пам’яті або безпосередній операнд, робиться командами порівняння. При виконанні цих команд, якщо операнди рівні, зводиться тригер нуля (Z=1), а якщо вміст акумулятора менше другого операнду команди, зводиться регістр переносу (C=1). Команди CMP r порівнюють акумулятор з регістром (один цикл, чотири такти), CMP M — вміст акумулятора і вічка пам’яті з адресою, що є в парі регістрів H, L (два цикли, сім тактів), CMI # — акумулятор з безпосереднім операндом (два цикли і сім тактів).

Відомо, що арифметичні операції над двійковими словами доцільно виконувати в зворотному або додатковому коді. Виконання операції перетворення кодів зручно здійснювати з використанням команди доповнення акумулятора CMA, при виконанні якої вміст акумулятора інвертується (біт, що дорівнює 1, стає рівним 0, а біт, що дорівнює 0, стає рівним 1). Прапорці при виконанні цієї команди не використовуються. Для її виконання треба один цикл, або чотири такти. Команда входить до складу спеціальних команд.

До спеціальних команд також відноситься команда, що встановлює прапорці переносу – STC (C=1), і команда, що доповнює прапорець переносу – CMC. При виконанні цих команд інші прапорці не використовуються. На їх виконання витрачається один машинний цикл М1, або чотири такти.

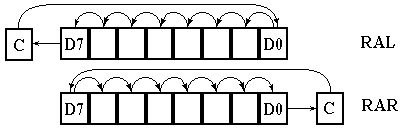

Часто виникає потреба виконати функцію зсуву вправо або вліво на один розряд. В системі команд МП КР580ИК80А є по дві команди лівого і правого зсуву. Зсув вмісту акумулятора вліво RLC і вправо RRC показані на рис. 6.2. При виконанні цих зсувів використовуються тільки прапорець переносу С, в якому дублюється вміст старшого або молодшого біту акумулятора.

Рис. 6.2. Виконання команди логічного зсуву акумулятора вліво RLC і вправо RRC.

Зсув може бути також виконаний з включенням в цей процес біту переносу С, як звичайного біту (рис. 6.3).

Рис. 6.3. Виконання команди логічного зсуву вмісту акумулятора з

включенням біту переносу вліво RAL і вправо RAR.

Адреса |

Мнемоніка команди |

|

8000 |

LXI |

H, 8020 |

8003 |

MOV |

A, M |

8004 |

INX |

H |

8005 |

MOV |

B, M |

8006 |

ANA |

B |

8007 |

STA |

8022 |

|

Вміст вічка |

|

8020 |

5F |

|

8021 |

F5 |

|

8022 |

55 |

|

Р

Рис. 6.4. Приклад програми для виконання

операції «І» над вмістом двох вічок.

Перед виконанням програми запишемо вихідні дані, над якими виконується операція «І», у двійковому коді. Очевидно, що виконання цієї логічної операції над числами 01011111 і 11110101 дасть результат 01010101, тобто 55 в 16-ковому коді. Виконавши програму, прочитаємо вміст ОЗП за адресою 8022 і впевнимось, що в цьому вічку дійсно записане число 55. Змінивши коди вихідних даних, можна заново виконати програму і отримати у вічку ОЗП з адресою 8022 новий результат.

Якщо модифікувати програму, замінивши команду за адресою 8006 на команду «АБО»

8006 ORA B

то при тих же вихідних даних (див. рис. 6.4) у вічку з адресою 8022 буде результат FF, що і повинно бути після виконання програми.

Приклад програми, що використовує команду зсуву, наведена на рис. 6.5. Програма виконує читання вічка ОЗП з адресою 8040 і, виконавши лівий зсув, розміщує результат в тому ж вічку ОЗП. Якщо занести у вічко байт AA, то після виконання програми в ній буде записаний байт 55. При повторному виконанні програми вміст вічка з адресою 8040 відновлюється.

-

Адреса

Мнемоніка команди

8000

LDA

8040

8003

RLC

8004

STA

8040

8007

JMP

8000

Вміст вічка

8040

AA

Рис. 6.5. Приклад програми, що використовує команди зсуву.

В цій програмі можна використати команду RRC, тобто зсув вправо. Результат програми буде такий же, в чому повинні впевнитись користувачі мікро лабораторії.

Схемна реалізація логічних операцій

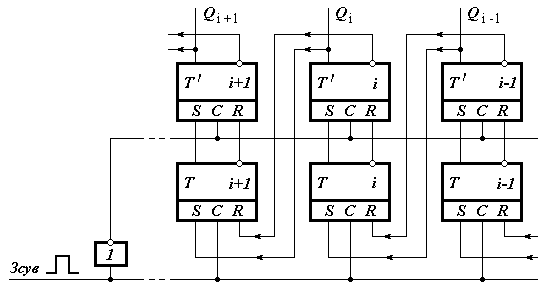

Зсуваючий регістр має такі ж вхідні і вихідні схеми, як і регістри прийому і видачі інформації, але вихід i-го розряду з’єднаний з настановними входами сусіднього розряду ліворуч для реалізації зсуву вліво, або сусіднього розряду праворуч для реалізації зсуву вправо. Тригери зсуваючих регістрів повинні бути складними з проміжним внутрішнім запам’ятовуванням. Якщо в зсуваючому регістрі використовуються прості тригери, наприклад RS-тригери, то необхідно використовувати ще один додатковий регістр для проміжного запам’ятовування слова в процесі зсуву. Фактично це призводить до того, що кожний розряд регістра буде складатись з двох тригерів (рис. 6.6).

Рис. 6.6. Схема розрядів зсуваючого вліво регістра на RS-тригерах.

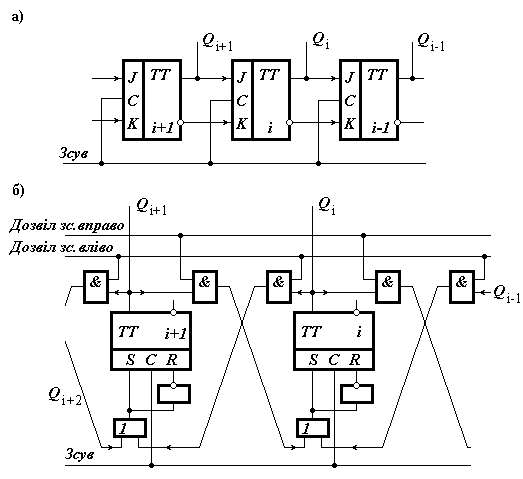

На рис. 6.7 показані схеми зсуваючих регістрів, побудованих на інтегральних JK-тригерах.

Тут використовується один JK-тригер на кожний розряд зсуваючого регістра, так як інтегральний JK-тригер уявляє собою каскадне з’єднання двох однотактних тригерів з автоматичною передачею інформації від вхідного тригера до вихідного. З’єднав входи J і K JK-тригера i-го розряду з виходами Q і Q JK-тригера (i+1)–го розряду відповідно (рис. 6.7-а), отримаємо послідовність JK-тригерів, кожний з яких виконує функції D-тригера. Зсув здійснюється вправо.

Схема реверсивного зсуваючого регістра на JK-тригерах показана на рис. 6.7-б. Схема функціонує під дією пари сигналів, що надходять по шині Зсув і по одній із шин керування реверсом (Дозвіл зсуву вправо / Дозвіл зсуву вліво), і має ту особливість, що передача інформації, що зсувається на сусідній тригер, здійснюється не парафазним кодом, а по одній лінії зв’язку. Одночасна подача одиничних сигналів на шини Дозвіл зсуву вправо і Дозвіл зсуву вліво заборонена, так як в цьому випадку інформація в регістрі під дією сигналу Зсув буде зіпсована. При нульових сигналах на цих шинах сигнал Зсув здійснить погашення регістра (встановить 0 на всіх тригерах регістру).

Зсуваючий регістр можна використовувати не тільки для зсуву коду, але і для перетворення паралельного коду, прийнятого в регістр, в послідовний. Для цього достатньо прийнятий код зсувати до тих пір, поки він не буде висунутий з регістру. Вихід з крайнього розряду використовується як вихідна шина послідовного коду. Зсуваючий регістр може виконувати також функцію перетворення послідовного коду в паралельний.

Рис. 6.7. Зсуваючі регістри на інтегральних JK-тригерах:

а) – однонаправлений зсуваючий регістр; б) – реверсивний зсуваючий регістр.

Реалізація порозрядних операцій в регістрах. Звичайно, операція видачі коду з регістра об’єднується з операцією прийому цього коду на інший регістр. В процесі передачі інформації з регістра на регістр можлива змістовна переробка кодів слів. В залежності від організації схем клапанів обміну інформацією між регістрами можуть бути здійснені такі операції:

перепис коду із регістра в регістр;

логічне додавання двох слів;

логічне множення двох слів;

порозрядне додавання двох слів (додавання за модулем 2).

Операція видачі коду з регістра була вже розглянута. Розглянемо виконання в регістрах інших операцій. Нехай два слова X і Y розміщені в регістрах RG1 і RG2 відповідно, а результат операції повинен бути утворений в регістрі RG2.

Значення результатів логічного додавання, логічного множення і додавання за mod 2 в кожному з розрядів регістра утворюються згідно таблиці 12.

Таблиця 12. Таблиця утворення результатів порозрядних операцій.

xi |

yi |

Qi = xi yi |

xi |

yi |

Qi = xi yi |

xi |

yi |

Qi = xi yi |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Н а

рис. 6.8 наведена схема для реалізації

виконання операцій порозрядного

додавання і множення.

а

рис. 6.8 наведена схема для реалізації

виконання операцій порозрядного

додавання і множення.

В Рг1 записаний код числа x1, x2, …, xn. Код іншого числа y1, y2, …, yn зберігається в Рг2. Код числа x1, x2, …, xn може бути переданий в Рг2 через систему логічних елементів І1 або І2. При збудженні шини передачі сигналом ЛД (логічне додавання) через схеми І1 на входи S тригерів регістра Рг2 пройдуть сигнали, що відповідають станам 1 тригерів регістра Рг1. Отже, стан 1 тригерів регістра Рг1 переноситься при передачі в тригери регістра Рг2 і об’єднується в кожному тригері регістра Рг2 з їх станами 1, що були встановлені кодом y1, y2, …, yn. Це і відповідає виконанню операції порозрядного додавання кодів відповідно таблиці 12.

При збудженні шини передачі сигналом ЛМ (логічне множення) через систему логічних схем І2 в регістр Рг2 на входи 0 тригерів будуть передані сигнали, що відповідають стану інверсних виходів тригерів регістра Рг1. В цьому випадку станеться скидання всіх тригерів регістра Рг2, крім тих, стан 1 яких співпадає з станом 1 тригерів регістра Рг1. Отже, виконання вказаної передачі сигналів призводить до виконанню операції порозрядного логічного множення у відповідності до таблиці 12.

Схема регістра, в якому виконується операція порозрядного додавання за mod 2 наведена на рис. 6.9. Нехай в регістр на тригерах з лічильними входами записаний код числа x1, x2, …, xn. По сигналу прийому коду Пр через систему схем І на лічильні входи тригерів в кожному розряді можна передати сигнали 1 коду числа y1, y2, …, yn. Проходячи на лічильний вхід, сигнали 1 призведуть до перекидання всіх тригерів, які попередньо сигналами коду x1, x2, …, xn були встановлені в стан 1 і 0, і в регістрі утвориться код числа Q1 Q2 …Qn-1 Qn як результат порозрядного додавання за mod 2.

Відзначимо, що в МП-системах регістри можуть бути представлені як окремими інтегральними схемами, так і входити як складові в структуру великих інтегральних схем, наприклад, ВІС мікропроцесора, ВІС інтерфейсу та інш.

В хідні

і вихідні кола тригерів регістрів в

залежності від функціонального

призначення регістра в МП-системі можуть

містити як елементи, що дозволяють

виконувати тільки окремі зазначені

вище операції, так і елементи, що

забезпечують виконання багатьох

операцій. Прикладом такого універсального

регістра може бути регістр А

(акумулятор) в ВІС

мікропроцесора КР580ИК80А.

хідні

і вихідні кола тригерів регістрів в

залежності від функціонального

призначення регістра в МП-системі можуть

містити як елементи, що дозволяють

виконувати тільки окремі зазначені

вище операції, так і елементи, що

забезпечують виконання багатьох

операцій. Прикладом такого універсального

регістра може бути регістр А

(акумулятор) в ВІС

мікропроцесора КР580ИК80А.