- •Лабораторна робота № 1 Тема: структура учбової мікропроцесорної лабораторії, клавіатура керування, індикація

- •Коротка інформація

- •Порядок виконання лабораторної роботи

- •Лабораторна робота № 2 Тема: пам’ять учбової мікропроцесорної лабораторії, дослідження виконання програм в покроковому I автоматичному режимах

- •Коротка інформація

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 3 Тема: дослідження програмно-доступних регістрів мікропроцесора кр580ик80

- •Коротка інформація

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 4 Тема: вивчення команд пересилання даних.

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 5 Тема: вивчення арифметичних команд

- •Коротка інформація

- •Індивідуальні завдання

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 6 Тема: вивчення логічних команд

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 7 Тема: вивчення команд переходів

- •Коротка інформація

- •Індивідуальні завдання

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 8 Тема: вивчення команд введення / виведення, керування і рестарту

- •Коротка інформація

- •Індивідуальне завдання

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 9 Тема: вивчення зв’язків мікролабораторії із зовнішнім середовищем

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 10 Тема: керування клавіатурою і індикаторами мікро лабораторії

- •Коротка інформація

- •Індивідуальні завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 11 Тема: програмування тимчасових затримок

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 12 Тема: програмне керування пристроями введення / виведення

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 13 Тема: динамічне керування об’єктами введення / виведення

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 14 Тема: імітаційне моделювання передньої панелі вимірювального приладу з вбудованим мп

- •Коротка інформація

- •Індивідуальне завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 15 Тема: тестування пам’яті мікропроцесорної системи

- •Коротка інформація

- •Індивідуальні завдання на лабораторну роботу

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Лабораторна робота № 16 5 Тема: макет мікропроцесорної системи охоронної сигналізації на автомобілі

- •Коротка інформація Постановка задачі

- •Інженерна інтерпретація

- •Оцінка системи

- •Порядок виконання лабораторної роботи

- •Контрольні питання

- •Додаток. Система команд 8–розрядного однокристального мікропроцесора к580ик80а.

- •Література

Індивідуальне завдання на лабораторну роботу

Скласти програму з команд пересилання. В програмі використати команди з рис. 4.1 всіх чотирьох типів.

Закодувати програму і записати її в табл. 3.1, виділивши в ній тільки ті графи з іменами регістрів, які використовуються при виконанні індивідуальної програми.

Порядок виконання лабораторної роботи

Завантажити програму в пам’ять мікро лабораторії.

Виконати програму в покроковому режимі.

При виконанні кожного кроку програми контролювати вміст всіх регістрів, що використовуються в програмі.

Результати виконання роботи зафіксувати в таблиці.

Прочитати вміст вічок пам’яті, які використані при виконанні програми. Результати показати на рис. 4.4.

Зробити короткі висновки по лабораторній роботі.

Контрольні питання

Охарактеризувати групу команд регістрових пересилань.

Чому команди, наприклад, MOV C, M і MOV C, H виконуються за різний час?

Пояснити послідовність дій при виконанні команди XCHG.

Охарактеризувати команди LHLD і SHLD.

Як виконуються команди STA і LDA?

В групі команд пересилання є команди MOV r, r. Як вони виконуються?

Лабораторна робота № 5 Тема: вивчення арифметичних команд

Мета: вивчити групу арифметичних команд, набути навичок складання програм з їх використовуванням

Коротка інформація

Виконання команд цієї групи полягає в певному арифметичному перетворенні вихідних даних в арифметико-логічному пристрої (АЛП) МП. Перелік команд і їх коди показані на рис. 5.1.

1. Додавання (без переносу) |

2. Додавання (з переносом) |

3. Віднімання (без переносу) |

4. Віднімання (з переносом) |

||||||||

Мнемоніка |

Код |

Мнемоніка |

Код |

Мнемоніка |

Код |

Мнемоніка |

Код |

||||

ADD |

A |

87 |

ADC |

A |

8F |

SUB |

A |

97 |

SBB |

A |

9F |

B |

80 |

B |

88 |

B |

90 |

B |

98 |

||||

C |

81 |

C |

89 |

C |

91 |

C |

99 |

||||

D |

82 |

D |

8A |

D |

92 |

D |

9A |

||||

E |

83 |

E |

8B |

E |

93 |

E |

9B |

||||

H |

84 |

H |

8C |

H |

94 |

H |

9C |

||||

L |

85 |

L |

8D |

L |

95 |

L |

9D |

||||

M |

86 |

M |

8E |

M |

96 |

M |

9E |

||||

5. Збільшення |

|

6. Зменшення |

7. Дії з безпосередніми даними |

|||||||||

Мнемоніка |

Код |

|

Мнемоніка |

Код |

|

Мнемоніка |

Код |

|

||||

INR |

A |

3C |

|

DCR |

A |

3D |

|

ADI |

# |

C6 |

|

|

B |

04 |

|

B |

05 |

|

ACI |

# |

CE |

|

|||

C |

0C |

|

C |

0D |

|

SUI |

# |

D6 |

|

|||

D |

14 |

|

D |

15 |

|

SBI |

# |

DE |

|

|||

E |

1C |

|

E |

1D |

|

|||||||

H |

24 |

|

H |

25 |

8. Подвійне додавання |

|||||||

L |

2C |

|

L |

2D |

|

DAD |

B |

09 |

|

|||

M |

34 |

|

M |

35 |

|

D |

19 |

|

||||

|

|

|

|

|

|

|

|

H |

29 |

|

||

INX |

B |

03 |

|

DCX |

B |

0B |

|

SP |

39 |

|

||

D |

13 |

|

D |

1B |

|

|

|

|

|

|||

H |

23 |

|

H |

2B |

9. Десяткова корекція |

|

||||||

SP |

33 |

|

SP |

3B |

|

DAA |

27 |

|

||||

Рис. 5.1. Арифметичні команди МП.

Операнди для виконання цих команд і результати виконання команд розміщуються в регістрах і вічках пам’яті. При виконанні цих команд змінюється стан прапорців знаку, нуля, парності, переносу і допоміжного переносу у відповідності до стандартних правил. Всі операції віднімання виконуються через арифметичне доповнення до двох, причому прапорець переносу встановлюється в логічну одиницю, якщо є запозичення, і скидається, якщо його нема.

Група команд додавання вмісту акумулятора з вмістом регістра (ADD r) розміщує результат виконання команди в акумулятор (A) + (r) (A). Для виконання команди витрачається час чотирьох тактів за один машинний цикл М1. Використовуються всі прапорці. Далі, якщо будь-які прапорці при виконанні команди не аналізуються, це вказується особливо. Якщо попередніми командами був зведений тригер переносу, то в сумуванні за командою ADD він участі не бере.

Команда ADD M здійснює додавання вмісту акумулятора з вмістом вічка пам’яті, адреса якого вказується парою регістрів H, L. Результат додавання розміщується в акумуляторі (A) + ((H)(L)) (A). На виконання команди за два цикли витрачається час семи тактів.

Без врахування стану біта (прапорця) переносу також виконується команда безпосереднього додавання акумулятора і вмісту другого байта команди ADI #. Для її виконання треба два цикли вибірки команди і додатковий такт у другому циклі для виконання, тобто сім тактів.

Друга, аналогічна група команд виконується з урахуванням прапорця переносу C, який сумується як молодший біт операнду. Ці команди, наприклад, можуть бути використані при обробці слів довжиною понад один байт. Команда ADC r забезпечує додавання із зберіганням результату в акумуляторі (A) + (r) + ([C]) (A). Аналогічно виконується команда з урахуванням переносу ADC M (додавання акумулятора з вмістом вічка пам’яті з адресою, яка міститься в парі регістрів H, L) і команда безпосереднього додавання з урахуванням біта переносу ACI #.

Аналізуючи команди, що показані на рис. 5.1, бачимо, що можна виділити відповідні розглянутим команди віднімання. Це група команд віднімання без переносу SUB r і SUB M і команди віднімання з запозичення (з урахуванням прапорця переносу С) SBB r, SBB M. Аналоги команд з безпосередніми операндами — безпосереднє віднімання SBI # і безпосереднє віднімання з запозиченням SUI #.

Для організації послідовної адресації і лічильників використовують команди інкрементування (збільшення на одиницю) і декрементування (зменшення на одиницю). Для регістрів, а також вічок пам’яті з адресацією за вмістом пари (H, L)- регістрів це команди INR, DCR, виконання яких не впливає на тригер переносу C.

В багатьох випадках необхідно організувати 16-розрядний операнд, для чого використовують пари регістрів. Для інкрементування або декрементування пари регістрів з сумуванням переносу або запозиченням між регістрами, що складають пару, використовують команди INX і DCX, при виконанні яких вміст регістра прапорців не змінюється.

Для розширення можливостей МП в складі команд є команди сумування вмісту регістрової пари з вмістом (H, L)-регістрів. Це команди — DAD rp, які мають назву "команди подвійного додавання". Для них використовується тільки прапорець переносу C, який встановлюється, якщо відбувся переніс з молодшого байту в старший, і скидається в протилежному випадку.

Розглянемо останню команду цієї групи — команду десяткової корекції (доповнення) акумулятора DAA. При її виконанні 8-бітне число в акумуляторі доповнюється до зображення у вигляді двох 4-бітних чисел в двійково-десятковому коді за допомогою таких операцій:

1. Якщо число, що зображене чотирма молодшими бітами акумулятора, більше дев’яти або встановлений прапорець допоміжного переносу AC, то до вмісту акумулятора додається шість.

2. Якщо тепер число, зображене чотирма старшими бітами акумулятора, більше дев’яти, або встановлений прапорець переносу C, то число шість додається до вмісту чотирьох старших бітів акумулятора.

При виконанні цієї команди аналізуються всі прапорці.

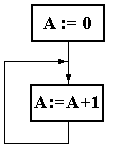

Розглянемо практичне використання команд цієї групи. Нехай необхідно організувати лічильник за mod 256. Алгоритм його функціонування і програма реалізації показана на рис. 5.2.

8000 |

3E |

00 |

|

|

MVI A, 00 |

8002 |

3C |

|

|

CO : |

INR A |

8003 |

C3 |

02 |

80 |

|

JMP C0 |

Рис. 5.2. Алгоритм і програма лічильника.

Виконання програми в покроковому режимі мікролабораторії дозволяє спостерігати на ІРД (на двох лівих індикаторах ІРД) вміст акумулятора, що збільшується з кроком +1. Вміст ІАР показує, що послідовно виконуються дві команди, записані за адресами 8002 і 8003.

За цією програмою легко ознайомитись з можливостями багаторазового проходження програми з зупинкою на встановленій адресі, причому кількість проходів встановлює користувач (див. лаб. роб. № 3).

Нехай є потреба у виконанні цієї програми AA разів і зупинитись на команді з адресою 8003. Для цього занесемо в ОЗП таку інформацію:

-

Адреса

Дані

83F0

02

83F1

80

83F2

AA

Натиснувши кнопку "Пуск", можна впевнитись, що на ІРД встановився стан акумулятора AA, тобто цикл виконаний задану кількість разів. Змінюючи вміст вічка 83F2, можна виконати програму лічильника яку-завгодно задану кількість разів.

Організуємо запис вмісту акумулятора в пам’ять мікро лабораторії так, щоб кожний новий стан лічильника заносився у вічко, адреса якого на одиницю більша за попередню (рис. 5.3).

-

Адреса

Код команди

Мітка

Мнемоніка

8000

3E

00

MVI

A, 00

8002

21

20

80

LXI

H, 8020

8005

3C

CO:

INR

A

8006

77

MOV

M, A

8007

23

INX

H

8008

C3

05

80

JMP

CO

Рис. 5.3. Запис вмісту лічильника в ОЗП.

Виконавши кілька циклів програми в покроковому режимі, перевіримо вміст вічок ОЗП, починаючи з адреси 8020. Дійсно, починаючи з цієї адреси, в ОЗП за адресами, що збільшуються, записані числа 01, 02, 03, ... .

Як і в попередньому прикладі, можна виконати задану кількість повторень виконання циклів, встановивши, наприклад, адресу зупинки 8006. Необхідно звернути увагу на виконання переносів між регістрами H, L при заповненні регістра L до числа FF. Очевидно, що не треба ніяких спеціальних заходів для організації послідовної адресації вічок ОЗП при переносі з молодшого в старший байт адреси.

Якщо, наприклад, необхідно організувати лічильник з кроком, що відрізняється від одиниці, можна скористуватись арифметичними командами. Для кроку, що дорівнює трьом, програма лічильника показана на рис. 5.4.

Адреса |

Код команди |

Мітка |

Мнемоніка |

Коментар |

|||

8000 |

06 |

03 |

|

|

MVI |

B, 03 |

; Завантаження 03 – кроку лічби – в регістр B |

8002 |

3E |

00 |

|

|

MVI |

A, 00 |

; Очищення акумулятора |

8004 |

80 |

|

|

COU: |

ADD |

B |

; Додавання кроку до A |

8005 |

C3 |

04 |

80 |

|

JMP |

COU |

; Перехід до лічби |

Рис. 5.4. Програма лічильника з кроком 3.

Зміна константи в першій команді програми дозволяє здійснити лічбу з будь-яким довільним кроком. Для реверсування напрямку лічби можна замість команди додавання (ADD) скористатись командою віднімання SUB.

В багатьох практичних застосуваннях доцільно здійснювати обробку даних в двійково-десяткових кодах для зменшення втрат часу на перетворення. Як приклад можна навести введення десяткових цифр з клавіатури приладів, виведення результатів обробки вимірів на індикатори. Як правило, в таких приладах або системах математична обробка мінімальна і може бути виконана повністю в двійково-десяткових кодах. При такій обробці використовуються ті ж самі арифметичні команди, однак результат після кожної арифметичної операції коректується за допомогою команди DAA.

Для прикладу розглянемо організацію лічильника за mod 10 (рис. 5.5).

-

Адреса

Код команди

Мітка

Мнемоніка

8000

AF

XRA

A

8001

00

NOP

8002

3C

ST:

INR

A

8003

27

DAA

8004

C3

02

80

JMP

ST

Рис. 5.5. Програма роботи лічильника за MOD 10.

В цій програмі для очистки акумулятора і прапорця переносу використовується команда ВИКЛЮЧАЮЧЕ АБО (XRA A) акумулятора з акумулятором. Очевидно, що вживання цієї команди робить програму більш ефективною – вона на один байт коротше попередніх програм, що використовували команду MVI A, 00. При виконанні програми в покроковому режимі мікро лабораторії особливу увагу слід звернути на момент переходу вмісту акумулятора в стан A. Оскільки лічба за mod 10 виключає можливість появи 16-кової цифри A, повинні бути організовані корекції цифри і перенос в наступний десятковий розряд. Цю функцію виконує наступна команда програми DAA. Після її виконання вміст акумулятора набуває значення 10. Механізм корекції розглянутий при описі цієї команди.

Арифметичні операції над багатобайтними числами

Як видно, процесор КР580ик80 безпосередньо може виконувати обмежене коло арифметичних операцій над однобайтними операндами. Але це не означає, що ним не можна виконувати складнішу обробку багатобайтних даних. Така обробка реалізується не однією окремою командою, а невеликими програмами. Нижче наводяться приклади програм деяких операцій з багатобайтними числами. При цьому використовуються такі символічні імена і адреси:

FIRST

SECND HL і DE N В

|

|

– адреса молодшого байту першого операнду і адреса результату; – адреса молодшого байту другого операнду; – вказівники даних; – довжина операндів в байтах; – лічильник байтів (представляє довжину операндів в байтах).

|

Приклад 5.1. Додавання багатобайтних чисел (цілих без знаку)

ADDN:

|

MVI

|

B, N |

; ініціалізація лічильника

|

|

LXI

|

D, FIRST |

; ініціалізація вказівників инициализация указателей

|

|

LXI |

H, SECND |

|

|

XRA LDAX

|

A

|

; скидання ознаки переносу

|

LOOP: |

LDAX |

D |

; завантаження першого операнду |

|

ADC

|

M

|

; додавання |

|

STAX

|

D

|

; запам’ятовування результату

|

|

DCR

|

В

|

; декремент лічильника

|

|

JZ

|

DONE

|

; додавання закінчено?

|

|

INX

|

H

|

; перехід до настіпного байту

|

|

INX

|

D

|

|

|

JMP

|

LOOP

|

; організація циклу

|

DONE:

|

…

|

; кінець

|

|

Примітки: 1. Для реалізації підпрограми віднімання SUBN необхідно повторити підпрограму ADDN, але замінити в ній команду ADC на команду SBB. У випадку отримання від’ємної різниці ознака С буде дорівнювати 1.

2. Для реалізації підпрограми складання багатобайтних десяткових двійково-кодованих чисел (BCD-чисел) в підпрограмі ADDN після команди ADC слід ввести команду DAA. Десяткове переповнення фіксується в розряді С регістра ознак.

Приклад 5.2. Віднімання багатобайтних десяткових двійково-кодованих чисел (BCD-чисел, цілих без знаку).

Віднімання BCD-чисел виконується в МП К580 відносно складно, оскільки команда DAA не корегує результат двійкового віднімання BCD-чисел. Віднімання BCD-чисел виконується в дві фази: спочатку отримують доповнення від’ємника до 10 n+1, а потім складають отриманий код із зменшуваним. При цьому команда DAA корегує результат двійкового складання BCD-чисел.

-

FIRST

D, E

SECND

H, L

N

В

адреса зменшуваного і різниці;

вказівник поточного байту зменшуваного;

адреса від’ємника;

вказівник поточного байту від’ємника;

довжина операндів в байтах;

лічильник байтів.

Підпрограма DSUBN

DSUBN;

|

MOV

|

B, N

|

|

; ініціалізація лічильника і вка-

|

|||

|

LXI

|

D, FIRST

|

|

зівників

|

|||

|

LXI

|

H, SECND

|

|

|

|

||

|

STC

|

|

; установка ознаки С

|

|

|||

LOOP:

|

MVI

|

A, 99H

|

|

; завантаження «дев’яток»

|

|

||

|

ACI

|

0

|

|

; врахування ознаки С

|

|

||

|

SUB

|

M

|

|

; доповнення від’ємника

|

|

||

|

XCHG

|

|

|

; обмін вказівників, HL вказує на зменшуване

|

|||

|

ADD

|

M

|

|

; додавання до зменшуваного

|

|

||

|

DAA

|

|

|

; корекція

|

|

||

|

MOV

|

МД * ‘-

|

|

; запам’ятовування різниці

|

|

||

|

XCHG

|

|

|

; відновлення вказівників

|

|||

|

DCR

|

B

|

|

; віднімання закінчено?

|

|

||

|

JZ

|

DONE

|

|

; так, вихід із підпрограми

|

|||

|

INX

|

D

|

|

; ні, віднімати следующие

|

|

||

|

INX

|

H

|

|

; байти

|

|

||

|

JMP

|

LOOP

|

|

; цикл

|

|

||

DONE:

|

…

|

|

; кінець

|

|

|||

Примітки: 1. Для представлення BCD-чисел із знаком вводиться тетрада для знаку (0000 – додатні числа, 1001 – від’ємні числа).

2. Використання в підпрограмі DSUBN команди взаємного, обміну XCHG дозволяє звертатися до пам’яті за однобайтними командами ADD М і MOV М, А, Команда XCHG дозволяє позбавитися від додаткових команд міжрегістрового обміну MOV г1, г2.

3. Отримання додаткового коду від’ємника і складання його із зменшуваним виконується в одному циклі.

4. Додатковий код від’ємника утворюється відніманням його, з коду «всі дев’ятки» і інкрементуванням результату. Саме для цього командою STC ознака переносу заздалегідь встановлюється в 1, а підсумовування виконується командою ACI яка враховує значення ознаки переносу.

5. Якщо після закінчення підпрограми ознака переносу дорівнює нулю, то це свідчить про отримання від’ємного результату.

6. Якщо двійкові числа представлені в двійковому додатковому коді, а BCD-числа представлені в десятковому до додатковому коді, то розглянуті підпрограми без змін можуть бути використані для операцій над числами із знаком. У випадку відсутності переповнення результат операції буде отриманий в додатковому коді.

Оскільки АЛП в МП К580 не формує ознаку переповнення, доводиться доповнювати підпрограми процедурою перевірки переповнення розрядної сітки, яка реалізується серією команд маскування та порівняння і працює за правилом: переповнення має місце, якщо знак результату відрізняється від однакових знаків обох операндів при складанні, або не співпадає із знаком зменшуваного при віднімання у разі, коли операнди мають різні знаки.

Програмна реалізація операції множення.

Існує багато різних алгоритмів виконання операції множення. Розглянемо найбільш часто використовувані способи і оцінимо їх достоїнства і недоліки.

Приклад 5.3. Множення байтів. Варіант 1. Множення молодшими розрядами вперед із зсувом часткової суми вправо.

D – множене, Е – множник, ВС – двобайтний добуток, L – лічильник бітів.

MULT1:

NXBIT:

|

LXI MVI MOV RAR

|

B, 0 L, 8 A, E

|

; скидання часткової суми ; завантаження лічильника ; множник в акумулятор ; біт, що аналізується в тригері С

|

|

|

MOV JNC MOV

|

Е, A NOADD A, B

|

; повернення зсунутого множника ; біт множника дорівнює нулю? ; ні

|

|

|

ADD MOV

|

D B,A

|

; додавання множеного ; повернення старшої часткової суми

|

|

NOADD:

|

MOV

|

A, B |

|

|

|

RAR MOV |

В, А |

; зсув часткової суми

|

|

|

MOV

|

A, C л., ‘-* , . .

|

||

|

RAR

|

|

||

|

MOV

|

С, А |

; повернення молодшої часткової суми |

|

|

DCR |

L |

|

|

DONE: |

JNZ ... |

NXBIT |

; організація циклу ; кінець |

|

Примітки: 1. Командою RAR аналізований біт множника поміщається в тригер переносу. Якщо він дорівнює 1, то вміст регістрів В і D сумують, а якщо С=0, то складання не виконується. Після цього (починаючи з мітки NOADD) проводиться зсув часткової суми управо.

2. Довжина підпрограми MULT1 складає 24 байт.

Приклад 5.4. Множення байтів. Варіант 2. С – добуток, D – множник, ВС – добуток, L – лічильник бітів. Множник поміщається на місце молодших розрядів добутку в регістр С. Молодші біти добутку заміщають старші біти множника, що звільняються, і тому окремих зсувів молодшого байту часткової суми виконувати не потрібно. За рахунок цього підпрограма MULT2, що наводиться нижче, на 3 байта коротша за підпрограму MULT1.

MULT2:

|

MVI

|

В, 0

|

; ініціалізація

|

|

MVI

|

L, 9

|

|

NXBIT:

|

MOV

|

А, С

|

; множник в акумулятор

|

|

RAR

|

|

; біт, що аналізується – в тригері С

|

|

MOV

|

С, А

|

; повернення зсунутого множника |

|

DCR

|

L

|

|

|

JZ

|

DONE

|

; кінець множення? |

|

MOV

|

А, В

|

; ні |

|

JNC

|

NOADD

|

; аналіз біта множника

|

|

ADD

|

D

|

; додавання множеного

|

NOADD:

|

RAR

|

|

; зсув часткової суми |

|

MOV

|

В, А

|

; повернення старшого байту часткової суми |

|

JMP

|

NXBIT

|

; організація циклу

|

DONE:

|

...

|

; кінець

|

|

Примітка. Перевірка закінчення множення проводиться до аналізу старшого біта множника, і тому в лічильник бітів L завантажується константа 9, а не 8.

Програмна реалізації операції ділення

Подібно до того, як операція множення в МП К580ИК80 реалізується послідовностями операцій «додавання–зсув», так і операція ділення виконується послідовністю операції «віднімання–зсув». Нижче розглядаються найбільш вживані способи програмної реалізації операції ділення для цілих чисел без знаку. При діленні отримують цілу частина приватного і позитивний залишок.

Приклад 5.5. Ділення однобайтних чисел (цілих без знаку) із зсувом ділимого (або залишків) вліво.

При діленні дільник послідовно віднімається зі все більшої частини ділимого і після кожного віднімання аналізується біт займу С. Якщо дільник більше тієї частини ділимого, з якої він віднімається, то С=1. В цьому випадку цифра результату рівна нулю, і дільник сумується з результатом віднімання для відновлення початкової частини ділимого (залишку). Якщо при відніманні заєму не виникає (С=0), то цифра результату рівна 1, а результат використовується як нове проміжне ділиме.

Призначення робочих регістрів наступне: Е – ділиме; D – дільник; L – лічильник бітів; Н – результат; С – залишок.

DIV:

|

LXI

|

Н, 8

|

; завантаження вказівника Н і

|

NXBIT: |

MVI MOV

|

С, 0 A, Е

|

; скидання регістра С ; ділиме в акумулятор

|

|

RAL |

; зсув ділимого вліво |

|

|

MOV

|

Е, А

|

; повернення ділимого

|

|

MOV

|

А, С

|

; проміжний залишок

|

|

RAL

|

|

; зсув залишку

|

|

SUB

|

D

|

; віднімання дільника

|

|

JNC

|

NOADD |

; залишок додатний |

|

ADD

|

D

|

; відновлення залишку

|

NOADD:

|

MOV

|

С, А

|

; запам’ятовування залишку

|

|

CMC

|

|

; інвертування С (утворення біта результату)

|

|

MOV |

А, Н

|

; запис цифри результату

|

|

RAL

|

|

|

|

MOV

|

Н, А

|

|

|

DCR

|

L

|

|

|

JNC

|

NXBIT |

; ділення на наступний біт |

|

RET

|

|

; повернення

|

Примітки: 1. До входу в підпрограму DIV ознака переносу С повинна бути скинутою.

2. Довжина підпрограми DIV складає 23 байти.