- •Т аблица

- •Электроника

- •Лабораторная работа №1 Исследование стабилизаторов

- •Краткая теория

- •Методика выполнения

- •Контрольные вопросы

- •Лабораторная работа №2 Исследование решающих усилителей на базе оу Краткая теория

- •Инвертирующий усилитель

- •Неинвертирующий усилитель

- •Усилитель с единичным коэффициентом усиления (повторитель напряжения)

- •Сумматор (суммирующий усилитель)

- •Методика выполнения

- •Контрольные вопросы

- •2. Напишите выражения для коэффициентов усиления схем умножения на постоянный коэффициент с инвертированием и без инвертирования входного напряжения.

- •Компараторы

- •Прецизионные выпрямители

- •Методика выполнения

- •Контрольные вопросы

- •Генератор колебаний треугольной формы

- •Методика выполнения

- •Контрольные вопросы

- •Генератор синусоидальных колебаний

- •Методика выполнения

- •Контрольные вопросы

- •Лабораторная работа №6 Исследование генераторов на интегральном таймере кр1006ви1

- •Краткая теория

- •МЕтодика выполнения

- •Контрольные вопросы

- •Лабораторная работа №7 Исследование пассивных и активных фильтров Краткая теория

- •Методика выполнения

- •Методика выполнения

- •Контрольные вопросы

- •Приложение 1

- •Библиографический список

- •Содержание

- •Электроника

- •443100, Г. Самара, ул. Молодогвардейская, 244. Главный корпус

- •443100, Г. Самара, ул. Молодогвардейская, 244. Корпус № 8

Методика выполнения

Целью работы является практическое получение АЧХ фильтров различного типа и определение мер по их улучшению. При снятии характеристик фильтров значения частот в таблицах ФНЧ и отдельно в таблицах ФВЧ, при которых измеряются выходные параметры, целесообразно для последующего анализа брать одинаковыми.

1. Включите необходимое программное обеспечение.

2. Соберите схему ФНЧ по рис. 7.1,а.. В качестве источника входного синусоидального сигнала подключите функциональный генератор, амплитуду выходного сигнала с которого установите в 10 В. Измерение выходного сигнала ФНЧ осуществляйте с помощью мультиметра. Так как последний выдаёт действующее значение напряжения Vд, то для нахождения амплитудного значения Va его показания необходимо умножить на 1,41. Сами кривые выходного напряжения наблюдайте по осциллографу, устанавливая на нём при различных частотах сигнала необходимую длительность периода развёртки.

3. Задайте величины R=50 Ом и С=1 мкФ и по (7.1) рассчитайте значение частоты среза fс. Изменяя частоту выходного сигнала генератора от 10 Гц до 30 кГц, измерьте действующие значения напряжения Vд на выходе ФНЧ и определите амплитудные значения Va. Рассчитайте величину коэффициента передачи К на данной частоте. Шаг изменения частоты выбирать произвольно, исходя из достаточной точности получения кривой передаточной функции. Вблизи частоты среза точки брать с меньшим шагом. Полученные результаты занесите в таблицу, по значениям К которой постройте АЧХ фильтра:

R = 50 Ом; C = 1 мкФ, Vвх = 10 B.

-

Частота f, кГц

0.01

…

…

30

Vд, B

Va, B

K

4. Задайте величины R = 25 Ом и С=1 мкФ. Повторите для этих исходных данных действия, указанные в п. 3. Результаты занесите в таблицу, по форме аналогичную приведённой выше. Постройте АЧХ.

5. Соберите схему ФВЧ по рис. 7.2,а, используя то же аппаратное обеспечение. Установите R=50 Ом и С=1 мкФ и найдите по (7.1) величину частоты среза для ФВЧ. Затем повторите действия, указанные в п. 3. Результаты занесите в таблицу, по форме аналогичную приведённой выше. Постройте АЧХ.

6. Задайте величины R= 25 Ом и С=1 мкФ. Повторите для этих исходных данных действия, указанные в п. 3. Результаты оформите в виде таблицы, аналогичной приведённой выше. Постройте АЧХ.

7. Соберите схему ФНЧ по рис. 7.3,а, используя то же аппаратное обеспечение. Установите R =50 Ом и С=1 мкФ, L = 1 мH. Найдите по (7.2) значение частоты среза. Изменяя частоту выходного сигнала генератора от 10 Гц до 30 кГц, измерьте мультиметром действующие значения напряжения на выходе ФНЧ, определите соответствующие амплитудные значения и найдите величины коэффициентов передачи фильтра. Вблизи точки среза характеристики шаг изменения частоты брать меньшим. Результаты оформите в виде таблицы, аналогичной приведённой выше. Постройте АЧХ.

8. Задайте величину R =25 Ом, оставив остальные элементы неизменными по номиналу. Повторите действия п. 7 для этих исходных данных. Результаты оформите в виде таблицы, аналогичной приведённой выше. Постройте АЧХ и объясните необычный вид кривой для этого случая.

9. Соберите схему ФВЧ по рис. 7.4,а, используя то же аппаратное обеспечение. Установите R =50 Ом, С=1 мкФ, L = 1 мН. Повторите действия п. 7 для этого случая. Результаты оформите в виде таблицы, аналогичной приведённой выше. Постройте АЧХ.

10. Задайте величину R =25 Ом, оставив остальные элементы неизменными по номиналу. Повторите действия п. 7 для этих исходных данных. Результаты оформите в виде таблицы, аналогичной приведённой выше. Постройте АЧХ.

11. Соберите схему ФНЧ по рис. 7.5,а, используя то же аппаратное обеспечение. Установите Rо=50 Ом, Со=1 мкФ. Сопротивление входного резистора Rвх инвертирующего усилителя установите также равным 50 Ом. Определите величину частоты среза фильтра fc = 1 / 2 CоRо . Изменяя частоту выходного сигнала генератора от 10 Гц до 30 кГц, измерьте мультиметром действующие значения напряжения на выходе ФНЧ, определите соответствующие амплитудные значения и найдите величины коэффициентов передачи фильтра. Вблизи точки среза шаг изменения частоты брать меньшим. Результаты оформите в виде таблицы, аналогичной приведённой выше. Постройте АЧХ.

12. Задайте величину Rо=Rвх=25 Ом, оставив остальные элементы неизменными по номиналу. Повторите действия, указанные в п. 11, для этих исходных данных. Результаты оформите в виде таблицы, аналогичной приведённой выше. Постройте АЧХ.

13. Соберите схему ФВЧ по рис. 7.6,а, используя то же аппаратное обеспечение. Установите Rвх =50 Ом, Свх=1 мкФ. Сопротивление резистора обратной связи взять равным сопротивлению входного резистора. Определите величину частоты среза fc= 1 / 2 Rвх Cвх . Затем повторите действия, указанные в п. 11, для этого случая. Результаты оформите в виде таблицы, аналогичной приведённой выше. Постройте АЧХ.

14. Задайте величину Rвх =Rо =25 Ом, оставив остальные элементы неизменными по номиналу. Повторите действия, указанные в п. 13, для этих исходных данных. Результаты оформите в виде таблицы, аналогичной приведённой выше. Постройте АЧХ.

Контрольные вопросы

1. В каких электронных схемах наиболее широко используются фильтры нижних частот?

2. Что такое полосовые фильтры, где они находят наиболее широкое применение?

3. Укажите область наиболее широкого применения фильтров верхних частот второго порядка.

4. В чём преимущества активных фильтров перед пассивными?

Лабораторная работа №8

Исследование логических элементов

Краткая теория

Простейшие логические элементы ЛЭ строятся на основе диодов и резисторов. Реализуемые с их помощью логические операции зависят от типа логики. При положительной логике схема, приведённая на рис. 8.1,а, позволяет реализовать функцию логического умножения, а схема на рис. 8.1,б – функцию логического сложения. При отрицательной логике с помощью схемы (см. рис. 8.1,а) реализуется функция логического сложения, а схемы на рис. 8.1,б – функция логического умножения.

Д ействительно,

если считать, что Е=+5 В и входные

напряжения могут принимать значения

+5 и 0 В, то, если хотя бы к одному из входов

Х1, Х2, Х3

(см. рис. 8.1,а) приложен сигнал 0,

соответствующий диод открыт и на выходе

схемы будет напряжение, близкое к 0 В.

При положительной логике это соответствует

коду «0». Если на все входы подано

положительное напряжение, большее или

равное Е, то все диоды закрыты и на

выходе напряжение Vвых=

+E, что при положительной

логике соответствует коду «1».

Следовательно, на выходе ЛЭ будет сигнал,

соответствующий коду «1» только в том

случае, если на все входы поданы сигналы

логической единицы. По определению

такой элемент выполняет логическую

функцию И.

ействительно,

если считать, что Е=+5 В и входные

напряжения могут принимать значения

+5 и 0 В, то, если хотя бы к одному из входов

Х1, Х2, Х3

(см. рис. 8.1,а) приложен сигнал 0,

соответствующий диод открыт и на выходе

схемы будет напряжение, близкое к 0 В.

При положительной логике это соответствует

коду «0». Если на все входы подано

положительное напряжение, большее или

равное Е, то все диоды закрыты и на

выходе напряжение Vвых=

+E, что при положительной

логике соответствует коду «1».

Следовательно, на выходе ЛЭ будет сигнал,

соответствующий коду «1» только в том

случае, если на все входы поданы сигналы

логической единицы. По определению

такой элемент выполняет логическую

функцию И.

При отрицательной логике уровень, близкий к 0 В, соответствует коду «1», а уровень +Е – коду «0». Если в этом случае на все входы подан уровень логического нуля, принятый выше за +5 В, то на выходе будет логический нуль (+Е). При подаче на любой из входов Х1, Х2, Х3 напряжения 0 В соответствующий диод открывается и выходное напряжение становится близким к 0 В. Это соответствует коду логической единицы.

Таким образом, подача на любой из входов сигнала, соответствующего логической единице, приводит к появлению на выходе кода «1», что характеризует логический элемент ИЛИ.

Итак, один и тот же логический элемент в зависимости от типа логики выполняет или логическую функцию И, или логическую функцию ИЛИ.

Аналогично рассмотренному работает схема, приведённая на рис. 8.1,б.

Недостатки простейших диодных ЛЭ (снижение выходного напряжения по отношению к входному за счёт его падения на открытом диоде, нестабильность уровней выходных напряжений) устраняются введением электронного усилителя по рис. 8.2. Выходной сигнал имеет низкий уровень U0вых при открытом транзисторе VT3 и высокий U1вых в тех случаях, когда VT3 заперт. Для открывания транзистора VT3 необходимо, чтобы потенциал эмиттера VT1 был больше напряжения стабилизации стабилитрона VD5. Для этого ко всем диодам VD1 – VD4 должно быть приложено напряжение высокого уровня, при котором они будут заперты. При низком уровне любого из входных сигналов потенциал эмиттера транзистора VT1 мал, ток через VD5 близок к нулю и транзистор VT3 заперт. Микросхема позволяет реализовать функцию И – НЕ.

На основе подобных ЛЭ выполняют высокопороговую логику, примером которой может служить серия 511. Эта серия отличается большими уровнями входных и выходных сигналов и высокой помехоустойчивостью.

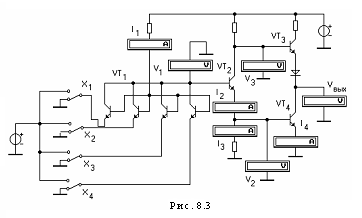

Транзисторно-транзисторные логические элементы (ТТЛ) широко распространены из-за большого быстродействия, высокой помехоустойчивости, умеренного потребления энергии, хорошей нагрузочной способности и малой стоимости. Их особенностью является наличие на входе многоэмиттерных транзисторов (МЭТ), с помощью которых реализуется требуемая логическая функция. МЭТ является эквивалентом нескольких транзисторов, у которых выводы баз и коллекторов по отдельности объединены. На рис. 8.3 приведена схема базового ЛЭ серии ТТЛ, в которой МЭТ VT1 выполнен в виде схемы замещения из четырёх транзисторов ввиду отсутствия в элементной базе моделирующей программы многоэмиттерных транзисторов.

Если на один или все эмиттеры МЭТ подано низкое напряжение (код «0» в положительной логике), то соответствующие эмиттерные переходы VT1 будут открыты. Через них протекает базовый ток VT1, замыкающийся на землю через

источники входных сигналов Х1,…,Х4, которые имеют близкие к нулю внутренние сопротивления. Транзистор VT1 находится в состоянии глубокого насыщения, и падение напряжения на нём близко к нулю, поэтому база VT2 находится под низким потенциалом и транзистор VT2 закрыт. Ток его эмиттера близок к нулю. Напряжение на базе VT4 также близко к нулю, и он заперт. Напряжение на базе транзистора VT3 близко к напряжению источника питания, поэтому VT3 открыт, и высокий уровень напряжения питания подаётся на выход схемы. Этот высокий уровень напряжения соответствует коду «1».

Если на все входы Х1,…,Х4 подан высокий уровень напряжения, то все эмиттеры VT1 оказываются смещёнными в обратном направлении и не пропускают электрический ток. Тогда ток потечёт через коллекторный переход VT1 и эмиттерный переход VT2, открывая VT2 и уменьшая потенциал его коллектора. Открывается транзистор VT4. В итоге всех переключений транзистор VT3 будет заперт, а транзистор VT4 открыт. На выходе схемы напряжение будет определяться напряжением коллектора насыщенного транзистора VT4. Это соответствует коду «0» в положительной логике. ЛЭ реализует функцию И-НЕ, так как код «0» появляется на выходе только тогда, когда на все входы VT1 поданы коды логической единицы.

Преимуществами ЛЭ на МОП-транзисторах перед ЛЭ на биполярных транзисторах являются большое входное сопротивление, простота технологического процесса изготовления, сравнительно низкая стоимость и малая потребляемая мощность. Однако по быстродействию даже лучшие ЛЭ на МОП-транзисторах уступают схемам на биполярных транзисторах. Это обусловлено наличием у МОП-транзисторов сравнительно больших входных емкостей, на перезарядку которых затрачивается определённое время. Кроме того, выходное сопротивление у открытого МОП-транзистора обычно больше, чем у биполярного, что увеличивает время зарядки конденсаторов нагрузки.

Наиболее перспективными являются ЛЭ на комплементарных МОП-транзисторах, содержащих в составе КМОП элемента два МОП-транзистора с разной электропроводностью каналов. Такие структуры успешно работают при изменении в широких пределах напряжения источника питания (от 3 до 15 В). В статическом режиме они почти не потребляют мощность.

На рис. 8.4 приведена принципиальная схема ЛЭ КМОП, выполняющая функцию 3И-НЕ. В нём использованы транзисторы с индуцированным каналом. Транзисторы VT1,…,VT3 имеют канал р-типа и открыты при напряжении затвора, близком к нулю. Транзисторы VT4,…,VT6 имеют канал n-типа и открыты при напряжении затвора, большем порогового значения.

При нулевом входном сигнале хотя бы на одном из входов ЛЭ один из транзисторов VT1,…,VT3 открыт и выходное напряжение равно Е. И только в том случае, если на всех входах есть сигнал логической единицы (обычно равный Е), все транзисторы VT1,…,VT3 закрыты, а ярусно включённые транзисторы VT4,…,VT6 открыты. Выходное напряжение равно потенциалу общей шины (логический нуль). Таким образом, сочетание ярусного включения транзисторов с каналами, имеющими один тип электропроводности, и параллельного соединения транзисторов с каналами другого типа электропроводности позволило реализовать функцию И-НЕ.

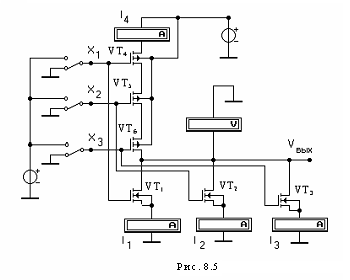

Если группы ярусно и параллельно включённых транзисторов поменять местами, то будет реализован элемент, выполняющий функцию ИЛИ-НЕ (рис. 8.5). Он работает аналогично предыдущему. Транзисторы VT1,…,VT3 открыты в том случае, если на их затворах логическая единица, и заперты при входных сигналах логического нуля.

Из рассмотренных схем видно, что в статическом режиме один из транзисторов, включённых последовательно, всегда закрыт, а другой открыт. Так как закрытый транзистор имеет большое сопротивление, то ток в цепи определяется только малыми значениями токов утечек, и микросхема практически не потребляет электрическую мощность.

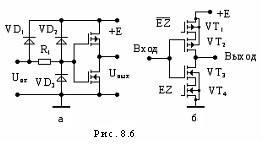

В качестве базового инвертора,

устанавливаемого на входе ЛЭ, обычно

используют цепь (рис. 8.6,а). Диоды

используются для предотвращения пробоя

плёнки оксида под затворами МОП-транзисторов.

При попадании в цепь входа статических

напряжений той или иной полярности

соответствующие диоды открываются и

закорачивают на цепь источника питания

источник статического заряда.

качестве базового инвертора,

устанавливаемого на входе ЛЭ, обычно

используют цепь (рис. 8.6,а). Диоды

используются для предотвращения пробоя

плёнки оксида под затворами МОП-транзисторов.

При попадании в цепь входа статических

напряжений той или иной полярности

соответствующие диоды открываются и

закорачивают на цепь источника питания

источник статического заряда.

По рис. 8.6,б реализуются ЛЭ с тремя устойчивыми состояниями. Последовательно с транзисторами инвертора включаются два комплементарных транзистора VT1, VT4 , управляемые инверсными сигналами. Если при их подаче транзисторы VT1, VT4 закрыты, то выходное сопротивление инвертора имеет большое значение (третье высокоимпедансное состояние).