- •1 Основы алгебры логики

- •1.1 Понятие о логических функциях

- •Функции одной и двух переменных

- •2.1Булевы функции одной переменной

- •Булевы функции двух переменных

- •2.3 Понятие базиса и функционально-полного базиса

- •Основные аксиомы и тождества алгебры логики

- •Способы задания Булевых функций

- •3.1 Описательный способ:

- •3.2 Аналитический метод:

- •3.2.1Совершенная дизъюнктивная нормальная форма (сднф)

- •3.2.2 Совершенная конъюнктивная нормальная форма (скнф)

- •3.2.3Таблица истинности и последовательность значений наборов переменных

- •3.2.4 Геометрический способ представления функций алгебры логики (фал) (кубические комплексы)

- •3.2.5 Временные диаграммы

- •3.2.6 Функциональные схемы

- •3.2.7 Взаимные преобразования способов представления фал

- •4. Основные характеристики и параметры логических элементов

- •4.1 Цифровые устройства и их классификация (из инета)

- •4.2 Передаточные характеристики

- •4.3 Входная характеристика

- •4.4 Выходная характеристика

- •4.5 Нагрузочная способность

- •5. Базовые логические элементы

- •5.1 Структура логических элементов

- •5.1.1 Логические устройства диодной логики

- •5.1.2 Простой усилительно-формирующий каскад

- •5.1.3Сложный усилительно-формирующий каскад (двухтактный)

- •5.2 Базовый элемент ттл-логики

- •5.2.5 Модификации базовых элементов

- •5.3 Ттлш-логический элемент

- •5.3 Базовые элементы кмоп логики, преимущества

- •6. Синтез комбинационных устройств

- •6.1 Основные этапы неавтоматизированного синтеза комбинационных устройств.

- •6.2 Минимизация цифровых устройств

- •6.2.1 Аналитическая минимизация фал

- •6.2.2 Минимизация фал на основе карт Карно

- •6.2.3 Смысл и применимость методов минимизации при синтезе цифровых устройств.

- •6.3 Приведение фал к заданному базису.(и-не, или-не, и-или-не)

- •Типовые комбинационные устройства

- •7.1 Типовые комбинационные цифровые устройства.

- •Преобразователи кодов

- •Шифраторы (кодеры) и дешифраторы (декодеры)

- •Мультиплексоры и демультиплексоры (Концентраторы)

- •7.5 Сумматоры

- •Компараторы кодов

- •8 Последовательностные устройства

- •8.1 Обобщённая схема последовательностного устройства

- •8.2 Понятие об автоматах Мили и Мура

- •9 Триггеры

- •9.1 Классификация

- •9.2.1 Асинхронный rs-триггер

- •9.2.2 Синхронизируемый уровнем

- •9.2.4 Двухтактный rs-триггер

- •9.3.1 Асинхронный d–триггер

- •9.3.4 Двухтактный d–триггер

- •9.4.1 Асинхронный

- •9.4.3 Синхронизируемый фронтом jk-триггер

- •9.4.4 Двухтактный jk-триггер

- •10. Типовые последовательностные устройства

- •10.1 Регистры

- •10.1.1 Классификация

- •10.2 Счетчики.

- •10.2.1 Классификация счетчиков.

- •10.2.3 Асинхронные двоичные счётчики

- •10.2.4 Суммирующие. Схема. Быстродействие

- •10.2.5 Вычитающий счетчик. Схема. Быстродействие.

- •10.2.6 Реверсивные счетчики

- •10.2.8 Счётчики с параллельным переносом

- •10.2.9 Счетчик с групповым переносом.

- •10 .3 Генератор чисел

- •10.4 Распределители импульсов

- •11.Цифрово-аналоговые преобразователи

- •11.1 Классификация цап

- •12 Аналого-цифровые преобразователи (ацп). Методы построения.

- •Параллельные ацп

- •Последовательно-параллельные ацп

- •Ацп последовательного приближения

- •Интегрирующие(равертывающего) ацп

- •Следящие ацп:

- •Сигма-дельта ацп

- •Тема 13. Общие принципы построения и функционирования компьютеров

- •13Машина фон Неймана

- •13.1.2 Машины Гарвардского и Принстонского классов

- •13.2 Организация памяти эвм

- •13.3 Микропроцессоры

- •Интерфейсы эвм

- •Общая организация систем обработки данных как совокупности аппаратных и программных средств.

- •14 Локальные и глобальные вычислительные сети.

- •15 Проблемы безопасности компьютерных сетей

10. Типовые последовательностные устройства

10.1 Регистры

10.1.1 Классификация

Регистры - триггерные устройства, предназначенные для хранения небольших объёмов информации и выполнения операций сдвига.

Занесение новой информации в регистр называется записью, а вывод информации - считыванием.

Для первоначальной установки всех триггеров в одинаковое состояние используется единый сигнал, а операция называется начальной установкой или сбросом.

Информация в регистре может сдвигаться при подаче специального сигнала на один или сразу несколько разрядов. Регистры с такой функцией называются сдвиговыми.

По способу записи и считывания различают регистры с параллельной и последователь-ной записью и считыванием соответственно. Можно образовать 4 разновидности таких регистров, комбинируя разные способы записи и считывания. Способа записи и считывания могут совмещаться.

Регистр сдвига может осуществлять сдвиг влево, вправо или быть реверсивным. Обычно регистр теряет информацию, выдвигаемую из него, но может иметь и кольцевую структуру. При этом вход последовательной записи соединяется с последовательным выходом регистра.

Входные и выходные сигналы могут быть однофазными и парафазными.

По способу синхронизации записи регистры делятся: на синхронизируемые уровнем (регистр защёлка) и синхронизируемы фронтом сигнала.

Сдвиговые регистры синхронизируются фронтом в случае единственного синхронизирующего сигнала. Возможно построение регистров с многофазной синхронизацией уровнем.

Существуют регистры, выполняющие много функций, их называют комбинированными или многорежимными ( многорежимный буферный регистр серии К589ИР12).

Синтез регистров

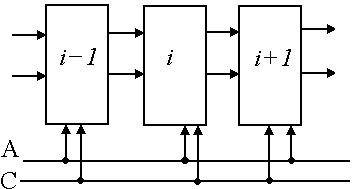

Синтез регистров достаточно прост, т.к. регистр представляет собой совокупность одинаковых разрядных блоков. В свою очередь разрядный блок включает в себя триггер (триггеры при многофазной синхронизации) и несложную комбинационную схему.

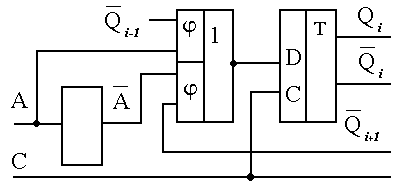

Выполним синтез одного разряда реверсивного счётчика на основе D-триггера. Сдвиг осуществляется на один разряд. Синтез осуществим словарным методом.

Структурную схему некоторого среднего звена регистра можно представить следующим

образом.

При А=0 сдвиг вправо

При А=1 сдвиг влево.

С – сигнал синхронизации.

При

А = 0 ,

При

А = 0 ,

;

;

;

;

При С=1

При С=1

При A = 1 ,

;

;

;

;

Если С = 0, то состояния не изменяются.

Таблица состояний среднего разряда.

-

N

A

F

D

0

1

2

3

0

0

0

0

0

0

0

0

0

0

1

1

0

1

0

1

0

0

0

0

0

0

0

0

0

0

4

5

6

7

0

0

0

0

1

1

1

1

0

0

1

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

8

9

10

11

1

1

1

1

0

0

0

0

0

0

1

1

0

1

0

1

0

0

1

1

0

1

0

0

1

1

12

13

14

15

1

1

1

1

1

1

1

1

0

0

1

1

0

1

0

1

0

0

1

1

0

1

0

0

1

1

Здесь F – функция переходов; D –вход i –го разряда. Хотя формально количество входных переменных 4, можно видеть, что функция возбуждения D-входа триггера не зависит от предыдущего состояния триггера.

Составим карту Карно и произведём с ее помощью минимизацию функции возбуждения.

-

D

AQi-1

Qi+1

00

01

11

10

0

0

1

0

0

1

0

1

1

1

или через СКНФ

или через СКНФ

Приводя к базису И-ИЛИ-НЕ, будем иметь:

Структурная схема одного разряда регистра приведена ниже.

Более просты структурно регистры хранения и регистры с односторонним сдвигом информации.

В случае регистра хранения синхронизация может осуществляться как фронтом, так и уровнем. Для сдвигового регистра обязательно применять триггеры тактируемые фронтом, двухступенчатые или с многофазной синхронизацией.

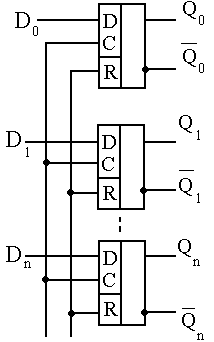

Регистр хранения на D триггерах.

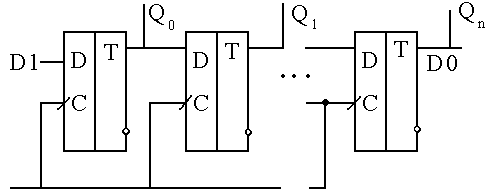

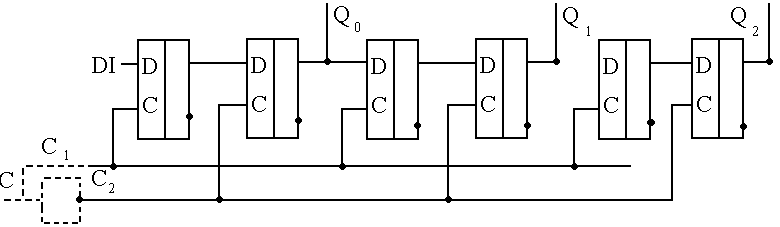

Регистр сдвига с последовательной записью и комбинированным выходом на D-триггерах, синхронизируемых фронтом.

Двухтактный регистр сдвига на D триггерах с синхронизацией уровнем.

Применение регистров

Регистры в вычислительной технике могут использоваться:

в качестве регистров временного хранения результатов операций (буферные);

для выполнения cдвигов при умножении и делении и прочих операциях;

в качестве преобразователей информации из параллельной формы в последовательную и обратно, что необходимо при создании простых линий связи ( ИРПС – RS232 и т.п. );

в качестве генераторов кодов в управляющих устройствах (при этом часто регистр закольцовывается).

Основные параметры

Регистры изготавливаются в виде СИС.

Статистические параметры их те же, что и у элементов соответствующей серии, т.е. уровни логического нуля и единицы, нагрузочная способность, входные токи, потребляемая мощность или ток.

К динамическим характеристикам относятся времена распространения от различных входов до выходов. Это время установки в исходное состояние, отсчитываемое от момента подачи сигнала R до установления выходного кода. Время распространения при записи информации. Часто задаётся максимальная частота синхронизирующих импульсов. Она определяется временем задержки сигнала в комбинационной цепи и временем срабатывания триггера.