- •1 Основы алгебры логики

- •1.1 Понятие о логических функциях

- •Функции одной и двух переменных

- •2.1Булевы функции одной переменной

- •Булевы функции двух переменных

- •2.3 Понятие базиса и функционально-полного базиса

- •Основные аксиомы и тождества алгебры логики

- •Способы задания Булевых функций

- •3.1 Описательный способ:

- •3.2 Аналитический метод:

- •3.2.1Совершенная дизъюнктивная нормальная форма (сднф)

- •3.2.2 Совершенная конъюнктивная нормальная форма (скнф)

- •3.2.3Таблица истинности и последовательность значений наборов переменных

- •3.2.4 Геометрический способ представления функций алгебры логики (фал) (кубические комплексы)

- •3.2.5 Временные диаграммы

- •3.2.6 Функциональные схемы

- •3.2.7 Взаимные преобразования способов представления фал

- •4. Основные характеристики и параметры логических элементов

- •4.1 Цифровые устройства и их классификация (из инета)

- •4.2 Передаточные характеристики

- •4.3 Входная характеристика

- •4.4 Выходная характеристика

- •4.5 Нагрузочная способность

- •5. Базовые логические элементы

- •5.1 Структура логических элементов

- •5.1.1 Логические устройства диодной логики

- •5.1.2 Простой усилительно-формирующий каскад

- •5.1.3Сложный усилительно-формирующий каскад (двухтактный)

- •5.2 Базовый элемент ттл-логики

- •5.2.5 Модификации базовых элементов

- •5.3 Ттлш-логический элемент

- •5.3 Базовые элементы кмоп логики, преимущества

- •6. Синтез комбинационных устройств

- •6.1 Основные этапы неавтоматизированного синтеза комбинационных устройств.

- •6.2 Минимизация цифровых устройств

- •6.2.1 Аналитическая минимизация фал

- •6.2.2 Минимизация фал на основе карт Карно

- •6.2.3 Смысл и применимость методов минимизации при синтезе цифровых устройств.

- •6.3 Приведение фал к заданному базису.(и-не, или-не, и-или-не)

- •Типовые комбинационные устройства

- •7.1 Типовые комбинационные цифровые устройства.

- •Преобразователи кодов

- •Шифраторы (кодеры) и дешифраторы (декодеры)

- •Мультиплексоры и демультиплексоры (Концентраторы)

- •7.5 Сумматоры

- •Компараторы кодов

- •8 Последовательностные устройства

- •8.1 Обобщённая схема последовательностного устройства

- •8.2 Понятие об автоматах Мили и Мура

- •9 Триггеры

- •9.1 Классификация

- •9.2.1 Асинхронный rs-триггер

- •9.2.2 Синхронизируемый уровнем

- •9.2.4 Двухтактный rs-триггер

- •9.3.1 Асинхронный d–триггер

- •9.3.4 Двухтактный d–триггер

- •9.4.1 Асинхронный

- •9.4.3 Синхронизируемый фронтом jk-триггер

- •9.4.4 Двухтактный jk-триггер

- •10. Типовые последовательностные устройства

- •10.1 Регистры

- •10.1.1 Классификация

- •10.2 Счетчики.

- •10.2.1 Классификация счетчиков.

- •10.2.3 Асинхронные двоичные счётчики

- •10.2.4 Суммирующие. Схема. Быстродействие

- •10.2.5 Вычитающий счетчик. Схема. Быстродействие.

- •10.2.6 Реверсивные счетчики

- •10.2.8 Счётчики с параллельным переносом

- •10.2.9 Счетчик с групповым переносом.

- •10 .3 Генератор чисел

- •10.4 Распределители импульсов

- •11.Цифрово-аналоговые преобразователи

- •11.1 Классификация цап

- •12 Аналого-цифровые преобразователи (ацп). Методы построения.

- •Параллельные ацп

- •Последовательно-параллельные ацп

- •Ацп последовательного приближения

- •Интегрирующие(равертывающего) ацп

- •Следящие ацп:

- •Сигма-дельта ацп

- •Тема 13. Общие принципы построения и функционирования компьютеров

- •13Машина фон Неймана

- •13.1.2 Машины Гарвардского и Принстонского классов

- •13.2 Организация памяти эвм

- •13.3 Микропроцессоры

- •Интерфейсы эвм

- •Общая организация систем обработки данных как совокупности аппаратных и программных средств.

- •14 Локальные и глобальные вычислительные сети.

- •15 Проблемы безопасности компьютерных сетей

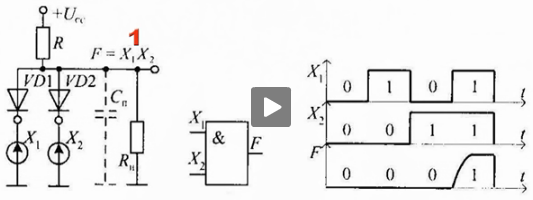

5.1.1 Логические устройства диодной логики

Диодные логические элементы являются исторически первыми и самыми простыми схемами, которые реализуют булевы функции И, ИЛИ , И-ИЛИ, И-ИЛИ-И. Особенностью ДЛЭ является то что они не усиливают входных сигналов и не могут выполнять операции НЕ. Рассмотрим реализацию элемента ИЛИ:

Из представленной схемы видно, что высокий уровень напряжения на выходе диодного элемента ИЛИ устанавливается при подаче на один или оба входа высоких уровнях напряжений, при которых открываются диоды VD1 или VD2, либо оба вместе, при подаче на оба входа низкого уровня напряжения диоды закрыты, то в выходной цепи не протекает выходное напряжение и почти равно 0, на выходе элемента обычно имеется паразитная емкость Cп 25-100 пкФ вследствие чего длительность фронта выходного сигнала очень мала, так как ёмкость быстро заряжается от источника входных сигналов, через малое прямое сопротивление открытого диода, а длительность спада выходного сигнала велика, так как диоды закрыты и ёмкость разряжается через резистор RH . Поэтому для диодных схем ИЛИ выполняется неравенство длительность фронта значительно меньше длительности спада. tLH << t HL

Теперь рассмотрим схему реализацию элемента И. Мы видим что высокий уровень

Напряжения на выходе диодного элемента устанавливается И, устанавливается при подаче на оба входа высоких уровней напряжений при которых закрываются диоды VD1 и VD2, длительность фронта выходного сигнала определяется временем заряда паразитной ёмкости Cп через большое сопротивление резистора R. Если на один из входов , например на первый подан низкий уровень напряжения, то диод VD1 открывается при этом от источника питания протекает ток по цепи резистор R открытый диод VD1 b и источник входного сигнала, на выходе устанавливается низкий уровень напряжения. Длительность спада выходного сигнала , определяется временем разрядки паразитной ёмкости Cп через молое открытое сопротивление диода, поэтому в диодных схемах И , tLH >> tHL

5.1.2 Простой усилительно-формирующий каскад

Рис. 3.5. Транзисторный усилительный каскад

В рассмотренной

схеме ток базы транзистора

Iб

определяется

входным напряжением

U,

падением

напряжения на переходе

ибэ

и сопротивлением в цепи базы

Rg

:![]()

а ток коллектора

Ik,

, должен превышать базовый в бетта

раз. Однако, при изменении тока через

транзистор происходит изменение

напряжения на коллекторе по закону:![]()

и, следовательно,

величина тока коллектора не может

превышать максимального значения :![]() ,

,

при котором напряжение на коллекторе становится равным нулю. Ток базы, при котором достигается максимальный коллекторный ток,

называется

граничным током.

При увеличении тока базы сверх

Ig

ток

называется

граничным током.

При увеличении тока базы сверх

Ig

ток

коллектора не увеличивается, и транзистор переходит в так называемый режим насыщения. В режиме насыщения происходит отпирание коллекторного перехода и в базе накапливается большое количество не основных носителей заряда.

Напряжение между коллектором и эмиттером транзистора в режиме насыщения равно 0,5^0,1 В и транзистор эквивалентен замкнутому ключу. Для надежного замыкания ключа транзистор переводят в режим глубокого насыщения, существенно увеличивая ток базы по сравнению с граничным.

Противоположным

насыщению является режим отсечки

транзистора. В этом случае![]() а

транзистор можно рассматривать как

ключ в разомкнутом

а

транзистор можно рассматривать как

ключ в разомкнутом

состоянии.

Для логических схем режимы отсечки и насыщения являются основными рабочими режимами.