- •1. Классификация электронных устройств

- •3. Полупроводниковые диоды

- •4. Биполярные транзисторы

- •7,8,9. Полевые транзисторы

- •10. Тиристоры

- •1(2) Общие сведения, классификация и основные характеристики усилителя. Типовые функциональные каскады полупроводникового усилителя

- •Основные характеристики усилителя

- •5.9 Типовая переходная характеристика усилителя

- •3,4(2) Обратная связь в усилителях

- •5(2) Статический режим работы усилительных каскадов

- •11(2) Усилительные каскады на полевых транзисторах

- •6(2) Усилительный каскад на биполярном транзисторе с общим эмиттером

- •9(2) Усилительный каскад на биполярном транзисторе с общим коллектором

- •17(2) Дифференциальные усилительные каскады

- •10(2) Усилительные каскады с динамической нагрузкой и с каскодным включением транзисторов

- •13(2) Основные положения теории обратной связи применительно к усилителям

- •14(2) Мощные усилительные каскады

- •15(2) Двухтактные выходные каскады.

- •14(2) Бестрансформаторные мощные выходные каскады

- •12(2) Многокаскадные усилители

- •18(2) Операционные усилители

- •Повторитель напряжения

- •19(2) Неинвертирующий усилитель

- •20(2) Инвертирующий сумматор

- •Неинвертирующии сумматор

- •21(2) Усилитель с дифференциальным входом

- •Интегратор

- •Дифференциатор

- •22(2) Логарифмический и антилогарифмический (экспоненциальный) усилители

- •1(3) Диодные ограничители амплитуды

- •5(3) Транзисторные мультивибраторы

- •6(3) Генераторы пилообразных импульсов

- •Генераторы линейно изменяющегося напряжения

- •2(3) Триггеры

- •3(3) Транзисторные триггеры

- •4(3) Несимметричный триггер с эмиттерной связью (триггер Шмитта).

- •10(3) Основные логические операции

- •Логические элементы и—не, или—не

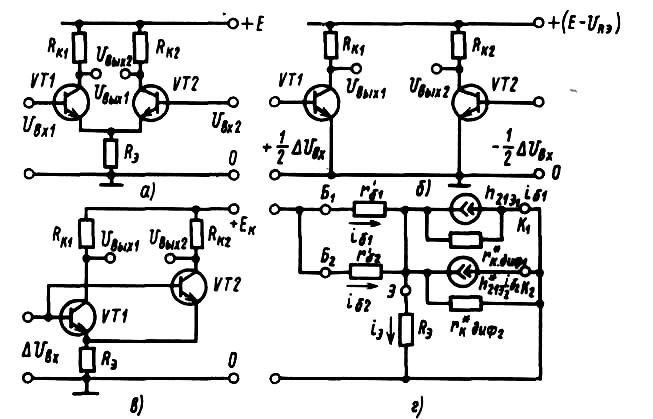

17(2) Дифференциальные усилительные каскады

Дифференциальный усилительный каскад (рис. 4.29, а) имеет два входа и усиливает разность напряжений, приложенных к ним. Если на оба входа подать одинаковое (синфазное) напряжение, то усиление будет чрезвычайно мало. Дифференциальный усилительный каскад не усиливает синфазный сигнал.

Дифференциальный каскад состоит из двух транзисторов, эмиттеры которых соединены и подключены к общему резистору Rэ. Для сигнала Uвxl транзистор VT1 включен по схеме с ОЭ, а транзистор VT2—по схеме с ОБ. Для сигнала UBx2 транзистор VT1 включен по схеме с ОБ, а транзистор VT2—по схеме с ОЭ.

П редположим,

что каскад абсолютно симметричен, т. е.

сопротивление

резисторов, входящих в каждое плечо, и

параметры

транзисторов VT1

и

VT2

одинаковы.

В этом случае при

равных входных сигналах Uвх1

и UBx2

токи

транзисторов

редположим,

что каскад абсолютно симметричен, т. е.

сопротивление

резисторов, входящих в каждое плечо, и

параметры

транзисторов VT1

и

VT2

одинаковы.

В этом случае при

равных входных сигналах Uвх1

и UBx2

токи

транзисторов

Рис. 4.29. Дифференциальный усилительный каскад:

а- базовая схема, б—схема эквивалентного преобразования, в—схема при подаче синфазного напряжения, г — упрощенная эквивалентная схема для синфазного входного сигнала

VT1 и VT2 равны между собой, а именно: Iк1=1к2, Iэ1=1э2, /Б1 = /Б2. Пусть входные напряжения получат одинаковые приращения разных полярностей 1/2ΔUвх:

![]()

В результате ток одного транзистора увеличится на Δ/к, а другого на столько же уменьшится:

![]()

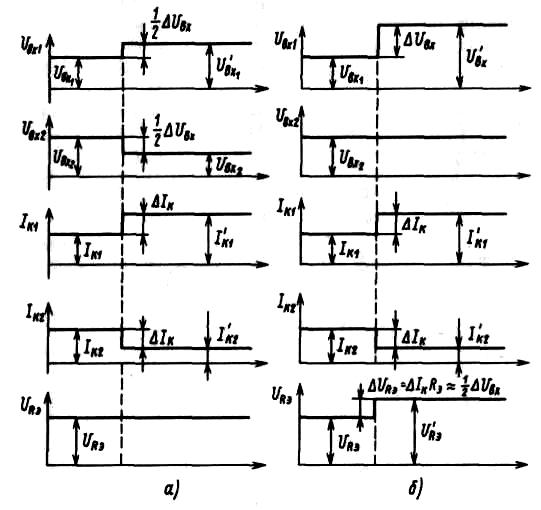

При этом результирующий ток через резистор Rэ останется без изменения. Постоянным будет и падение напряжения на нем (рис. 4.30, а).

Если входное напряжение изменить только на одном входе на ΔUвх, т.е. U'BXl = UBXl + AUвх, то это приведет к изменению тока через соответствующий транзистор. Если бы транзистор VT2 отсутствовал, транзистор VT1 был бы включен по схеме с ОЭ и ток в его цепи изменился бы на 2Δ/К. При этом падение напряжения на Rэ увеличилось бы на ΔU'Rэ:

![]()

Рис. 4.30. Диаграммы напряжений и токов при симметричной схеме подачи входного напряжения (а) и при несимметричной схеме (б)

Но увеличение паления напряжения на регистре Rэ приведет к уменьшению разности потенциалов между базой и эмиттером транзистора VT2 и ток его уменьшится, причем изменение тока транзистора VT2 будет таково, что приращения напряжений эмиттер — база обоих транзисторов будут одинаковы. Следовательно, при увеличении UBXl на ΔUBX потенциал эмиттера увеличится на ΔUBX/2, что эквивалентно увеличению тока через резистор Rэ на Δ/к (рис. 4.30,6). При этом приращение напряжения база—эмиттер для транзистора VT1 равно ΔUBX/2 и —ΔUBX/2 для транзистора VT2. Ток каждого плеча изменится на Δ/к. Очевидно, что независимо от того, как на вход каскада подаются напряжения, токи транзисторов в первом приближении меняются одинаково. В действительности из-за небольших значений h21э транзисторов, конечных значений резисторов в Rэ и ненулевых входных сопротивлений каскадов с ОБ при разной схеме подачи входных напряжений имеется небольшая разница. Это следует учитывать при уточнении полученных результатов и в ответственных случаях обеспечивать симметричную схему подачи входных напряжений. Приращения их вызваны половиной разности напряжений, приложенных между входами. Это дает основание при анализе дифференциального каскада рассматривать только одну его половину, считая, что к входу его приложена половина разности напряжений между входами, а сопротивление в эмиттерной цепи равно нулю (см. рис. 4.29,6).

Такой подход справедлив для любой схемы подачи напряжения. Напряжения база — эмиттер обоих транзисторов, вызывающие входные токи, равны между собой и равны половине разности входных напряжений: ΔUBX = UBXl — UBx2-

Эквивалентная замена дифференциального каскада на каскады, показанные на рис. 4.29,6, позволяет использовать результаты, полученные для каскада с ОЭ.

Коэффициент усиления по напряжению дифференциального каскада при холостом ходе определяется как отношение разности выходных напряжений к разности входных:

![]()

Из выражения видно, что в режиме холостого хода коэффициент усиления по напряжению дифференциального каскада равен коэффициенту усиления каскада с ОЭ, идентичного одному плечу дифференциального каскада.

Выходное сопротивление каскада, если пренебречь сопротивлением коллекторного перехода, в два раза выше, чем у соответствующего каскада с ОЭ:

![]()

Входное сопротивление для разностного сигнала (дифференциальное входное сопротивление каскада) также в два раза больше, чем у каскада с ОЭ:

![]()

Как видно, входное дифференциальное сопротивление невелико. Для его повышения в цепь эмиттера каждого из транзисторов можно включить равные по значению сопротивления резисторы Ro так, чтобы rэдиф стало равным rэдиф + Ro. Можно также снижать коллекторные токи, что ведет к увеличению rэдиф, но при этом снижается коэффициент усиления.

При подключении сопротивления нагрузки RH коэффициент усиления уменьшается. Оценить влияние нагрузки можно подставив выходную цепь источником напряжения KUΔUBX с внутренним сопротивлением Rвых. При подключении сопротивления нагрузки на нем будет падать напряжение

![]()

и если коэффициент усиления по напряжению оценить как

![]()

то он примет значение

![]()

При подаче на входы дифференциального каскада синфазного напряжения (см. рис. 4.29,в) напряжения Uвых1 и Uвых2 изменятся, но в полностью сбалансированном дифференциальном каскаде разность их останется той же.

Это еще раз подтверждает, что в идеальном дифференциальном каскаде синфазный входной сигнал не вызывает появления дифференциального выходного сигнала.

Найдем входное сопротивление каждого входа для синфазного входного сигнала. Для этого используем упрощенную эквивалентную схему каскада для средних частот (см. рис. 4.29, г), в которой не учтено сопротивление эмиттерного перехода гэдиф ввиду его малости по сравнению с сопротивлениями R’, Rк, r*кдиф, а также RKl, Rк2 вследствие выполнения условия Rк<< r*кдиф.

У идеально сбалансированного каскада параметры плеч равны.

Тогда входное напряжение каскада

![]()

откуда входное сопротивление каждого входа для синфазного сигнала

![]()

Чем выше Rвхсф, тем меньше входной ток синфазного сигнала и тем меньше изменения выходных напряжений Uвых1 и Uвых2. Поэтому сопротивление в эмиттерной цепи Rэ, которое, по существу, определяет входное сопротивление для синфазного сигнала, необходимо увеличивать. Из сравнения выражений для синфазного и дифференциального сигналов видно, что они существенно различаются и значение входного сопротивления для синфазного сигнала во много раз выше, чем для дифференциального.

При увеличении сопротивления Rэ приходится сталкиваться с проблемой обеспечения необходимого режима работы транзисторов по постоянному току. Если в статическом режиме значения токов транзисторов /ко1 и /ко2 выбраны, то с увеличением Rэ приходится увеличивать напряжение питания каскада, так как

![]()

При значении сопротивления Rэ, определенного из требуемого входного сопротивления для синфазного сигнала, напряжение питания

![]()

становится настолько большим, что реализация такого каскада может стать технически нецелесообразной. Кроме того, на резисторе Rэ будет бесполезно рассеиваться электрическая мощность, что снижает КПД каскада.

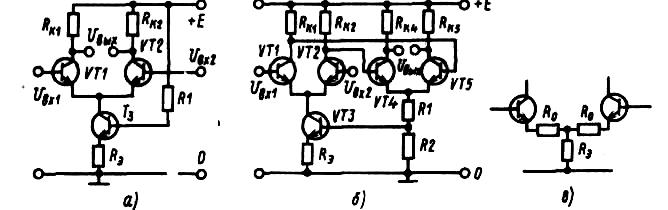

Для устранения этого недостатка вместо резистора Rэ включают транзистор по схеме с ОЭ (рис. 4.31, а). Транзистор VT3 выполняет функции источника тока. Действительно, если задать в цепи базы транзистора VT3 определенное значение тока /Б3, то в цепи коллектора будет протекать ток

![]()

Рис. 4.31. Дифференциальный каскад с транзисторным источником тока в цепи эмиттера (а); введение ОС по синфазному сигналу (б); включение сопротивлений, упрощающих настройку усилителя (в)

Если бы транзистор VT3 был идеальным источником тока, то изменения тока транзисторов VT1 и VT2 не вызвали бы изменения тока через транзистор VT3 и можно было бы считать, что в эмиттерную цепь включено бесконечно большое сопротивление. Так как выходное сопротивление транзистора VT3 не равно бесконечности и определяется в рассматриваемом случае дифференциальным сопротивлением коллекторного перехода r *кдиф, то можно считать, что для синфазного сигнала входное сопротивление для двух параллельно соединенных входов

![]()

При малых токах транзисторов VT1 и VT2 синфазное входное сопротивление находится в пределах десятков — сотен МОм. На высоких частотах, когда сопротивление емкости коллекторного перехода транзисторов Ск* соизмеримо с сопротивлением rкдиф, синфазное входное сопротивление существенно уменьшается. Его можно найти, если вместо r *кдиф подставить

![]()

Хотя в идеальном дифференциальном каскаде синфазный сигнал на его входе не вызывает появления дифференциального выходного сигнала, в реальном каскаде наблюдается небольшой дифференциальный выходной сигнал. Он обусловлен неполной идентичностью характеристик транзисторов, разницей в значениях коллекторных сопротивлений Rк1, Rк2 и внутренних сопротивлений источников, подключенных к входам каскада.

Неидентичность характеристик транзисторов приводит к тому, что при изменении токов вследствие воздействия синфазного сигнала коэффициенты передачи базового тока и входные сопротивления транзисторов изменяются по-разному. В результате этого коллекторные токи транзисторов также изменяются.

В диапазоне высоких частот существенную роль в разбалансе каскада играют емкости коллекторных переходов. Они являются основной причиной роста усиления синфазного сигнала в диапазоне высоких частот.

Для количественной характеристики усиления дифференциального и синфазного сигналов используют коэффициент ослабления синфазного входного напряжения Koccф (коэффициент подавления синфазного сигнала), который показывает, во сколько раз коэффициент усиления дифференциального входного сигнала Ku диф выше, чем синфазного Кисф:

![]()

Значения коэффициента ослабления синфазного входного напряжения могут достигать нескольких тысяч.

Следует отметить, что коэффициент ослабления синфазного сигнала уменьшается в случае несимметричного выхода, когда напряжение снимается только с коллектора одного из транзисторов. В этом случае он равен отношению входных сопротивлений для синфазного и дифференциального входных сигналов.

Для повышения коэффициента ослабления синфазного входного напряжения вводят синфазную обратную связь по току (рис. 4.31, б). Для этого к дифференциальному усилительному каскаду подключают аналогичный дифференциальный каскад (транзисторы VT4, VT5), часть напряжения эмиттера которого управляет источником тока на транзисторе VT3. При подаче синфазного сигнала на входные зажимы транзисторов VT1, VT2 токи их изменяются. Соответственно изменятся потенциалы баз транзисторов VT4, VT5 и токи через них, что вызовет изменение напряжения на резисторе R2. Это напряжение управляет током транзистора VT3, обеспечивая тем самым отрицательную ОС по синфазному сигналу. Такая ОС уменьшает отклонения токов транзисторов VT1, VT2 от требуемого значения, вызванные синфазным сигналом, и соответственно уменьшает величину разбаланса каскада.

Для примера рассмотрим, как будут протекать процессы при подаче входного синфазного напряжения, уменьшающего токи транзисторов VT1, VT2. Под влиянием этого напряжения потенциалы баз транзисторов VT3, VT4 возрастут, что приведет к увеличению их коллекторных токов. Повысится напряжение и на резисторе R2, что вызовет увеличение тока транзистора VT3 и уменьшение падения напряжения на нем. В свою очередь, увеличится разность потенциалов между базами и эмиттерами транзисторов VT1, VT2 и их ток.

ОС по синфазному сигналу поддерживает рабочие точки транзисторов вблизи заданных и тем самым уменьшает разбаланс каскада.

На коэффициент усиления дифференциального сигнала ОС влияния не оказывает. Составив эквивалентную схему каскада, можно количественно оценить влияние ОС по синфазному сигналу.

Дифференциальные каскады достаточно чувствительны к параметрам отдельных элементов и сложны в наладке. Поэтому на практике между эмиттерами транзисторов часто включают небольшие резисторы Ro, упрощающие настройку и расширяющие диапазон допустимых входных сигналов (рис. 4.31, в). Однако при этом уменьшается коэффициент усиления каскада. Если транзисторы дифференциальных каскадов достаточно хорошо подобраны в пары и сопротивления в их коллекторных цепях равны, то влияние изменения температуры на их токи будет одинаково:

![]()

При этом ток и напряжение в нагрузке останутся неизменными. Поэтому усилительные каскады этого типа находят применение при построении усилителей постоянного тока (УПТ).

На практике идеальной компенсации обычно добиться не удается, и при изменении температуры наблюдается изменение выходного сигнала. Если дифференциальное входное напряжение равно нулю, а выходное меняется с изменением температуры, то такое изменение называется температурным дрейфом нуля. При неизменной температуре выходной сигнал несколько изменяется с течением времени (это обусловлено старением компонентов и изменениями их параметров).

Временной дрейф нуля оценивают в абсолютных значениях изменения сигнала за определенный промежуток времени.

Дрейф нуля обычно приводят ко входу, так чтобы его значение показывало, какой нужно подать входной сигнал для того, чтобы получить изменение выходного сигнала, равное его температурному или временному приращению. Для этого изменение выходного напряжения с температурой или в течение определенного времени делят на коэффициент усиления каскада. Типовое значение температурного дрейфа нуля дифференциального каскада 1—20 мкВ/град. Временной дрейф составляет единицы—десятки мкВ в год, а при плохих компонентах — мВ/ч и более.

Если дифференциальный каскад используется в качестве УПТ, то дрейф выходного сигнала может быть вызван и изменениями входных токов транзисторов. Действительно, для нормальной работы каскада в его базовых цепях должны протекать определенные токи. Если бы они не изменялись, то с помощью дополнительных внешних цепей можно было бы обеспечить практически полное отсутствие входного тока в цепях источника усиливаемого сигнала. Однако значения входных токов транзисторов зависят от изменения температуры и для уменьшения влияния этих изменений приходится принимать специальные меры.

Основным способом уменьшения входного тока является уменьшение тока эмиттера /э. Иногда /э уменьшают до 10—50 мкА, при этом /Б1 мкА и наблюдается дрейф порядка 0,1—0,2 мкА на каждые 10 °С (для кремниевых транзисторов).

Дополнительное снижение влияния дрейфа тока базы можно получить применяя специальные типы транзисторов и используя параметрические компенсационные схемы.

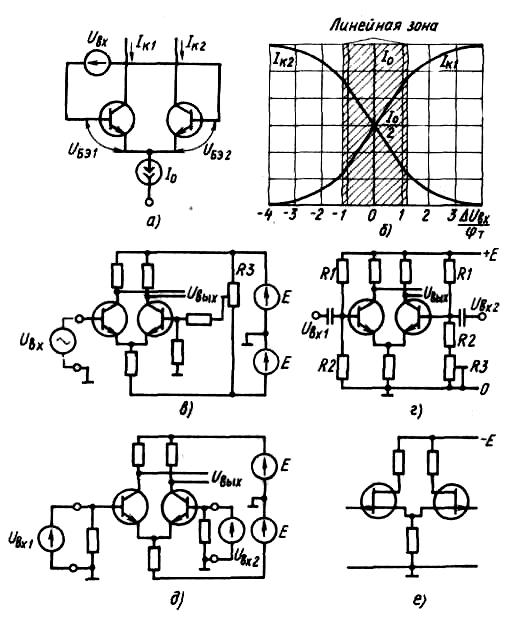

Линейность характеристики преобразования у дифференциальных каскадов наблюдается только при малых значениях входных напряжений, соизмеримых с тφт. Покажем это на примере каскада, выполненного на идеализированных транзисторах, у которых h216→1, /кэо<</к, а в цепь эмиттеров установлен генератор тока /0 (рис. 4.32, а). Эти допущения позволяют записать уравнения транзисторов в упрощенном виде:

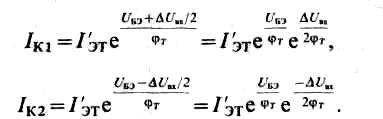

![]()

Рис. 4.32 Расчетная схема (а) и зависимости токов коллектора от входного напряжения (б); включение дифференциального каскада в схемы усилителя постоянного напряжения (в), усилителей разности двух переменных (г) и двух постоянных напряжений (д); дифференциальный каскад на полевых транзисторах (е)

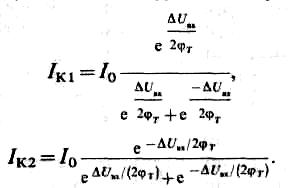

В статическом режиме (ΔUвх = 0) у идеально подобранной пары транзисторов UБЭ1 = UБЭ2 = UБЭ и /К1 = /к2 = ½/0. При Uвх ≠0 напряжение UБЭ одного транзистора увеличится на ½ ΔUвх, а другого уменьшится на ту же величину (доказано выше). Тогда токи коллекторов

Учитывая, что

![]()

Тогда

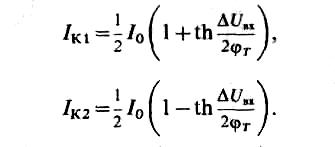

Так как выходной сигнал Uвых пропорционален разности токов /К1 и /К2, которая равна

![]()

то он является функцией гиперболического th от входного напряжения. Несложно показать, что при одинаковых по модулю приращениях токов коллекторов Δ/К1 и Δ/К2 их значения определяют из уравнений

При малых значениях ΔU вх(ΔU вх ≤φт) каскад обычно можно считать линейным (рис. 4.32, б). Поэтому при работе в качестве усилителя входное напряжение,

как правило, не превышает 0,1 В. В выражении температурный потенциал φт меняется с изменением температуры, что приводит к температурной зависимости характеристик преобразования.

Изменение тока /0 вызывает соответствующее приращение выходного тока и коэффициента усиления. Это важное свойство дифференциального каскада, которое позволяет применять его для умножения двух сигналов. Действительно, если в (4.188) ток /0 сделать функцией одного сигнала /0 =f1(U1), a Δ UBX =f2 (U2)—другого, то выражение будет иметь вид

![]()

Некоторые из возможных схем использования дифференциального каскада в качестве усилителя медленно меняющегося сигналов и усилителей разности двух сигналов переменного и постоянного тока приведены на рис. 4.32, в – д. Резистор Rз введен для компенсации неидеальности плеч, вызванной разбросом параметров транзисторов и резисторов. С помощью его каскад балансируется для получения Uвых = 0 при UBX = 0.

Аналогично рассмотренному выполняют дифференциальные каскады на полевых транзисторах (рис. 4.32, е). Их анализ и расчет подобны разобранному. Качественно похожи и общие свойства. При расчете и построении схем устройств необходимо учитывать, что управляющим сигналом являются потенциалы затворов, а их ток имеет малое значение.

Дифференциальные усилительные каскады широко применяют для построения усилителей постоянного тока и логических элементов. Они являются одними из наиболее распространенных в интегральной схемотехнике.

Таким образом, дифференциальные каскады имеют: \) входное сопротивление для дифференциального сигнала, равное удвоенному сопротивлению одиночного каскада с ОЭ (без сопротивления в эмиттерной цепи); 2) высокое входное сопротивление для синфазного сигнала; 3) коэффициент усиления по напряжению для дифференциального сигнала, равный коэффициенту усиления одиночного каскада с ОЭ; 4) коэффициент усиления для синфазного сигнала, стремящийся к нулю; 5) выходное сопротивление, в два раза большее, чем у одиночных каскадов с ОЭ с аналогичными параметрами компонентов. Кроме усиления они позволяют выполнять умножение двух сигналов.