- •1 Способ.

- •2 Способ.

- •Организация однопроцессорных эвм.

- •Основные устройства входящие в эвм.

- •Система прерываний.

- •Система памяти. Классификация памяти.

- •Динамическая память.

- •Режим чтения записи.

- •Режим регенерации информации.

- •Режим страничной чтения записи.

- •Синхронная и асинхронная память.

- •Синхронная динамическая память

- •Кэш память

- •Постоянные запоминающие устройства

- •Пзу на 4 байта

- •Ппзу (Программированные пользователем запоминающие устройства)

- •Фрагмент ппзу (рисунок)

- •Спзу (Стираемые постоянные запоминающие устройства)

- •Фрагмент спзу (рисунок)

- •Эипзу (Электрические изменяемые постоянные запоминающие устройства)

- •Модульный принцип построения памяти

- •Организация плоской памяти

- •Особенности pdp-11

- •Организация памяти ibm – pc

- •Виды организации памяти

- •Прямой доступ к памяти (пдп, dma)

- •Принцип пдп

- •Упрощенный алгоритм обмена.

- •Структурная схема контроллеров пдп

- •Устройства массовой памяти или внешние запоминающие устройства.

- •Ограничения fat

- •Файловые системы ntfs

- •Общие выводы:

- •Оптические накопители.

- •Интерфейсы внешних запоминающих устройств.

- •Клавиатура.

- •Мониторы.

- •Интерфейс Centronics

- •Вычислительные комплексы и системы Параллельная обработка информации

- •Конвейер арифметических операций

- •Конвейер команд

- •Многопроцессорные вычислительные системы.

- •Типы структурной организации (мпвк).

- •С общей шиной.

- •С разделяемой памятью. ( с многоходовыми озу)

- •Особенности организации вычислительных комплексов.

- •Комплексы с общем полем оперативной памяти.

- •Комплексы cmmp.

- •Проект Эльбрус.

- •Этапы проекта Эльбрус

- •Структура Эльбрус 2 (рис.)

- •Основополагающие принципы проекта

- •Эвм Эльбрус 3м

- •Супер эвм мвс – 100к

- •Супер эвм мвс 15000 вм

- •Супер эвм мвс – 6000

- •Проект blue gene

- •Вычислительные системы. Системы с конвейерной обработкой информации.

- •Система cray

- •Матричные системы окмд.

- •Ассоциативные системы.

- •Функционально распределенные системы.

- •Транспьютеры.

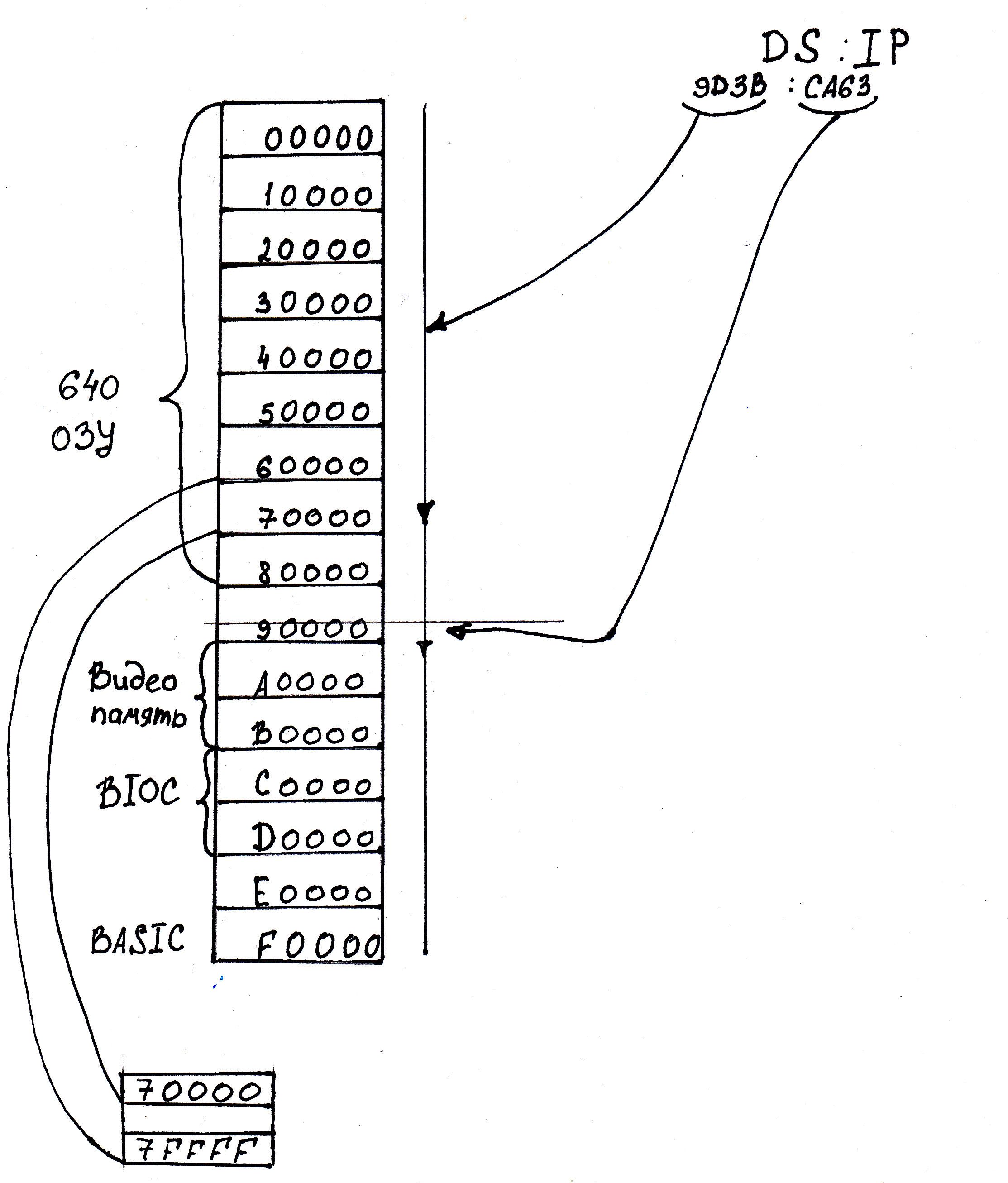

Организация памяти ibm – pc

16-разрядный процессор.

Шина адреса – 20 разрядов.

Общий объем памяти 1 Мбайт.

Адресное пространство разделено на 16 блоков по 64 Кбайт каждый.

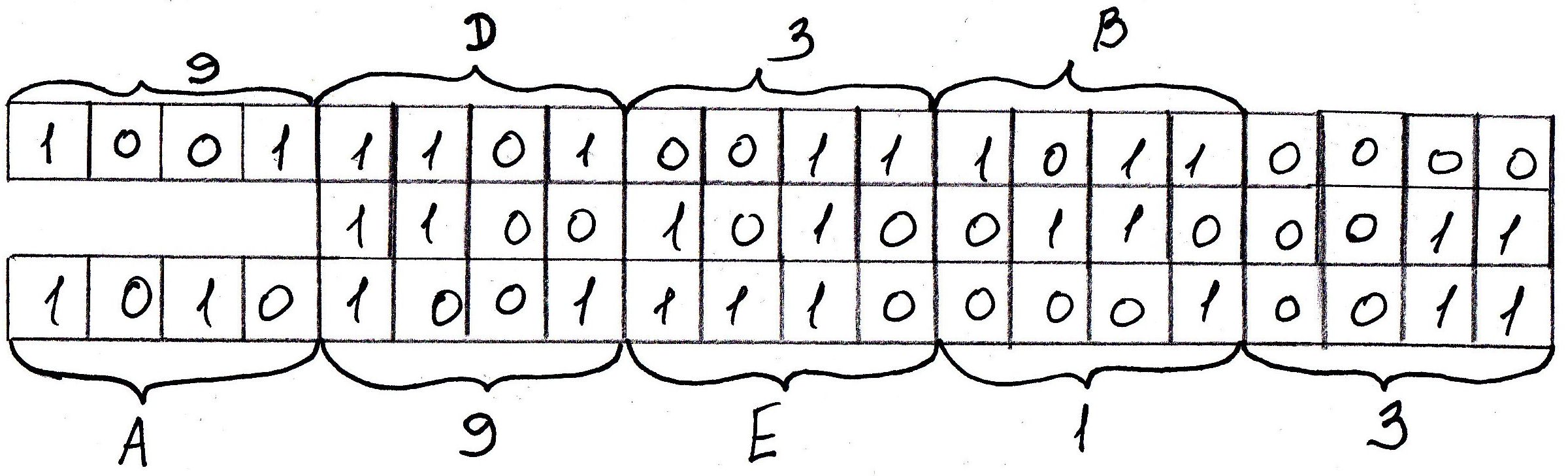

Так как процессор 16-разрядный, а шина адреса 20 разрядов, то полный адрес ячейки определяется путем сложения 16-разрядного адреса сегмента с 16-разрядным относительным смещением внутреннего сегмента.

Сегментный регистр (DS)

Индексный IP.

Если адрес сегмента сдвинуть влево на 4 разряда, дополнив справа нулями, то получим 20-разрядный адрес начала сегмента. Сложив его с 16-разрядным относительным смещением, получим полный 20-разрядный адрес ячейки.

Виды организации памяти

В общем случае память строится по 3 основным принципам:

1. Запоминающее устройство с произвольной выборкой (ЗУПВ).

2. Память типа FIFO (буферная память).

3. LIFO или стек.

Буферная память (FIFO)

Буферной памятью называется – объект памяти, которым владеют одновременно два объекта, не связанные между собой.

Используется для согласования работы устройств с различным быстродействием, а так же при мультипрограммной обработке.

Стек (LIFO) [Память магазинного типа]

Стек (англ. stack — стопка) — структура данных с методом доступа к элементам LIFO (англ. Last In — First Out, «последним пришёл — первым вышел»). Чаще всего принцип работы стека сравнивают со стопкой тарелок: чтобы взять вторую сверху, нужно снять верхнюю.

Стек используется при переходе к подпрограммам и обработке прерываний. В нем сохраняется состояния прерванной программы, необходимые для успешного возврата (пример патроны).

При выходе из стека подпрограммы в обратной последовательности извлекаются данные.

Стек является разделом основной памяти. Адресуется с помощью специального регистра в составе центрального процессора, который называется указатель стека, который содержит адрес верхушки стека. При занесении данных в стек значения указателя стека автономно изменяются (обычно увеличиваются) таким образом, что он содержит адрес следующей свободной ячейки.

Лекция № 6

Прямой доступ к памяти (пдп, dma)

Прямой доступ к памяти (англ. Direct Memory Access, DMA) — режим обмена данными между устройствами или же между устройством и основной памятью (RAM), без участия Центрального Процессора (ЦП). В результате скорость передачи увеличивается, так как данные не пересылаются в ЦП и обратно.

Используется для обмена большими массивными информациями между оперативной памятью и внешними запоминающими устройствами. При этом центральный процессор отключается от систем магистрали и процессом обмена управляет контроллер ПДП, выполняющий следующие функции:

Принимает запрос на ПДП.

Формирует и посылает центральному процессору запрос на захват системной магистрали.

Принимает от ЦП подтверждение захвата.

Направляет внешнему устройству сигнал, информирующий о начале цикла ПДП.

Выдает на шину адреса адрес первой ячейки оперативной памяти, предназначенной для обмена.

Вырабатывает сигналы, обеспечивающие работу системной магистрали при обмене.

Изменяет (модифицирует) адрес ячеек оперативной памяти в процессе обмена.

По окончанию циклов ПДП передает ЦП управление системной магистралью.