- •Микропроцессорные контроллеры

- •8.3 Система команд

- •10.4 Организация памяти

- •1. Типы архитектур микроконтроллеров

- •1.1 Основные структуры вычислительных систем

- •1.2 Определение микропроцессора

- •1.3 Шинная организация соединений

- •1.4. Типы архитектур микроконтроллеров

- •2 Микроконтроллер на базе 8-разрядного

- •2.1 Описание микропроцессора кр1821вм85

- •2.2 Режимы работы мп

- •3 Микроконтроллер на базе 16-разрядного микропроцессора к1810вм86

- •3.1 Технические характеристики мп к1810вм86

- •3.2 Назначение сигналов

- •3.3 Программно-доступные регистры

- •3.5 Организация внешней памяти

- •3.6 Структурная схема мк на базе мп к1810вм86

- •3.7 Способы адресации

- •3.8 Система команд мп 1810вм86

- •3.8.1 Команды пересылок данных

- •2. Пересылки “регистр-память” -

- •3.8.2 Команды преобразование данных

- •10. Команды сдвигов –

- •3.8.3 Команды передачи управления

- •1. Безусловные переходы -

- •8 Микроконтроллер на базе омэвм к1816ве48

- •8.1 Технические характеристики к1816ве48

- •8.2 Способы адресации операндов

- •8.3 Система команд

- •Rlc a, rrc a ; циклические сдвиги влево и вправо через признак переноса.

- •8.4 Таймер

- •8.5 Структурная схема мк

- •9 Микроконтроллер на базе омэвм к1816ве51

- •9.1 Технические характеристики омэвм к1816ве51

- •9.2 Организация памяти

- •9.3 Регистры специальных функций

- •9.4 Способы адресации операндов

- •9.5 Система команд

- •Rlc a, rrc a ; циклические сдвиги влево и вправо через признак переноса.

- •9.6 Управление прерываниями

- •9.7. Последовательный ввод-вывод данных

- •9.8 Таймеры

- •11.1 Семейство pic-контроллеров

- •12 Современные тенденции в развитии

- •12.1 Сигнальные процессоры фирмы Texas Instruments

- •12.2 Сигнальные процессоры Analog Devices

- •12.3 Транспьютеры

8 Микроконтроллер на базе омэвм к1816ве48

ОМЭВМ в настоящее время получили широкое распространение для разработки микроконтроллеров, так как использование ОМЭВМ в системах управления обеспечивает достижение исключительно высоких показателей эффективности при столь низкой стоимости, что им, видимо нет в ближайшем времени альтернативной элементной базы [16].

Напомним, что однокристальная микроЭВМ (ОМЭВМ) – это

СБИС, в которой на одном кристалле размещены МП, ОЗУ, ПЗУ и УВВ.

Рассматриваемая данной главе ОМЭВМ К1816ВЕ48 входит в состав целого семейства ОМЭВМ, которое объединяется общим названием – МК48. Отличительные различия в характеристиках представителей семейства МК48 приведены в таблице 8.1.

Таблица 8.1.

Микросхема |

Аналог |

ПЗУ, байт |

Тип ПЗУ |

ОЗУ, байт |

Макс. fт, МГц |

Потреб. ток, мА |

КР1816ВЕ35 |

I-8035 |

Нет |

Внеш. |

64 |

6 |

135 |

КР1816ВЕ48 |

I-8048 |

1 К |

УФППЗУ |

64 |

6 |

135 |

КР1816ВЕ39 |

I-8039 |

Нет |

Внеш. |

128 |

11 |

110 |

КР1816ВЕ49 |

I-8049 |

2 К |

ПЗУ |

128 |

11 |

110 |

КР1830ВЕ35 |

I-80C35 |

Нет |

Внеш. |

64 |

6 |

8 |

КР1830ВЕ48 |

I-80C48 |

1 К |

ПЗУ |

64 |

6 |

8 |

8.1 Технические характеристики к1816ве48

ОМЭВМ К1816ВЕ48 имеет следующие технические характеристики:

- шина данных – 8 разрядов;

- шина адресов – 12 разрядов;

- адресное пространство – 212 = 4 кбайта;

- внутреннее ПЗУ – 1 кбайт;

- расширение ПЗУ – до 3 кбайт;

- внутреннее ОЗУ – 64 байта;

- внешнее ОЗУ – 256 байт (4 страницы по 64 байта);

- команды - 1 или 2 байта;

- тактовая частота fт - 6МГц;

- прерывания - 2 уровня;

- ввод-вывод данных – 3 порта.

Организация ПЗУ. ПЗУ используется для хранения программ, при этом внутреннее ПЗУ объемом 1 кбайт занимает адреса – 000003FFh., а при подключении внешнего ПЗУ объемом 3 кбайта адресное пространство расширяется до адреса 0FFFh.

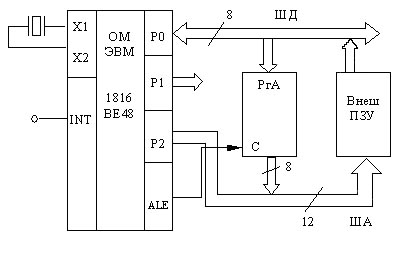

На рисунке 8.1.1 представлена схема подключения внешнего ПЗУ. Порт P0 выполняет роль совмещенной 8-разрядной шины A/D, по которой при обращении к внешнему ПЗУ передается сначала младший байт адреса, а затем порт P0 переходит в режим чтения кодов из внешнего ПЗУ. Передача младшего байта сопровождается сигналом ALE, по заднему фронту которого младший байт адреса с выхода порта Р0 защелкивается в регистр адреса РгА. Временные диаграммы этого процесса полностью совпадают с временными диаграммами МП К1821ВМ85 (рисунок 2.2.1).

Старшая часть адреса – 4 разряда ША11-ША8, передается через порт Р2 и удерживается в течение всего цикла обращения к внешнему ПЗУ. Подключение внешнего ПЗУ расширяет программные возможности МК, но сокращает возможности по подключению внешних устройств, так как свободным остается только один порт Р1 (рисунок 8.1.1).

В этой связи необходимо заметить, что если для реализации МК не хватает объема внутреннего ПЗУ, то практического смысла подключать внешнее ПЗУ никакого нет. Так как возникает необходимость в дополнительных ИС – ПЗУ, РгА, то лучше перейти к использованию микропроцессора, например К1821ВМ85. Использование МП позволит существенно расширить и адресное пространство – до 64 кбайт, и расширить функциональные возможности по системе команд. Использование ОМЭВМ хорошо именно тем, что не требует дополнительных ИС.

Рисунок 8.1.1 Схема подключения внешнего ПЗУ

Организация ОЗУ. ОЗУ используется для оперативного хранения данных. Особенностью организации ОЗУ является объединение в единое адресное пространство как регистров общего назначения (РОН), стека и собственно ячеек ОЗУ.

На рисунке 8.1.2

представлена диаграмма распределения

адресов внутреннего ОЗУ. В диаграмме

выделены следующие области:

На рисунке 8.1.2

представлена диаграмма распределения

адресов внутреннего ОЗУ. В диаграмме

выделены следующие области:

1. Два банка РОНов по 8 регистров – R0-R7. Для обращения к этим ячейкам ОЗУ используется регистровая адресация, при которой:

- команда – однобайтная;

- команда включает в себя наряду с кодом операции (КОП) адрес (номер) РОНа.

В текущем состоянии ОМЭВМ работает только один банк РОНов. Выбор банка осуществляется программно, с помощью команд

SEL RB0 ; выбор банка 0

SEL RB1 ; выбор банка 1;

2. Стек – 16 ячеек ОЗУ с последовательным доступом. Обращение организовано по магазинному принципу, когда первым из стека читается код, который был записан последним, то есть по принципу LIFO (см. раздел 2.2, п.6). ОМЭВМ не имеют специальных команд загрузки байта в стек и чтение его из стека. Обращение к стеку выполняется для команд CALL и RET.

3. ОЗУ пользователя имеют адреса 32-63. Для обращения к ОЗУ используется только косвенная адресация с использованием регистров R1 и R0 для хранения адреса. При этом адресоваться можно к любой ячейке ОЗУ, включая РОНы и стек.

Кроме указанного ОЗУ в ОМЭВМ имеется аккумулятор А и регистр PSW - регистр состояния программы, который имеет следующие значения разрядов:

- D7 – признак переноса С;

- D6 – признак дополнительного переноса AC;

- D5 – признак пользователя F0, устанавливаемый в лог. “0”

командой CLR F0 или в состояние лог.”1” командой CPL F0;

- D4 – указывает на рабочий банк РОНов;

- D3 – не используется;

- D2-D0 – указатель стека.