- •Тема 1 Общая методология происхождения скс

- •Основные понятия и определения

- •Принципы системного подхода

- •Жизненные цикла изделия, системы

- •Назначение скс, состав и структура

- •1.5 Принципы создания систем

- •1.6 Стадии и этапы создания

- •1.7 Требования к содержанию, виды и комплектность документов

- •Тема 2 Кеш-память

- •2.1 Назначение и типы кеш-памяти

- •2.2 Архитектура кеш-памяти

- •2.2.1 Кеш прямого отображения

- •2.2.2 Полностью ассоциативная архитектура

- •2.2.3 Наборно(Частично)-ассоциативная архитектура

- •2.3 Методы записи, целостность данных

- •2.4 Методика расчета кеш-памяти

- •Методы подключения средства диагностирования компа и общие принципы разработки уст-в сопряжения.

- •4.2 Сравнение вариантов подключения средства диаг-ния к компу

- •Основные ф-ии уст-ва сопряжения и релиз-я основных видов совместимости

- •Сравнение методов реализации ф-ий устр-в сопряжения

- •5. Организация обмена информацией между процессорами и внешними устройствами

- •5.1 Организация ввода-вывода

- •5.2 Методы управления вводом-выводом

- •5.3 Типовая структура контроллеров

- •6. Контроллеры внешних устройств

- •6.1 Особенности графического изображения временных диаграмм

- •6.2 Структурная и функциональная организация контроллеров

- •6.3 Типовые структуры контроллеров

- •8 Лекция (5.10.2011)

- •8.1 Синхронные последовательные интерфейсы

- •8.2 Контроллер последовательной синхронной передачи, схема, алгоритм, подпрограмма.

- •8.3 Контроллер последовательного синхронного приема.

- •9 Лекция (10.10.2011)

- •9.1 Асинхронный последовательный контроллер передачи информации из пк в сд.

- •9.2 Контроллер последовательного асинхронного приема информации из сд в пк.

- •Проектирование подсистем ввода аналоговой информации

- •12. Построение подсистемы ввода аналоговой информации

- •12.1 Анализ структурных схем

- •12.2 Пример схем модуля аналогового вывода

- •12.1 Анализ структурных схем

- •12.2 Пример схем модуля аналогового вывода

- •13. Рекомендации по выбору компонентов системы вв/выв аналоговой информации

- •13.2 Проблемы, возникающие при дискретизации и последующем восстановлении.

- •13.3 Выбор параметров ацп.

- •Тема 15 Последовательная шина usb (Universal Serial Bus)

- •15. 1 Структура и взаимодействие системы usb

- •15. 2 Физический интерфейс

- •Тема 16 Особенности использования usb, обмен инфо-

- •16.1 Организация обмена инфо-

- •16. 1.1 Модель передачи данных

- •16.1.2 Типы передаваемых данных

- •16. 1.3 Протокол и форматы пакетов

- •16.2 Модификации usb

- •17. Контроль достоверности информации(кди) в скс.

- •17.1 Кди в микросхемах озу небольшого объема и при последовательном варианте обмена информацией.

- •17.2 Кди в накопителях на гибких дисках и кмоп-памяти.

- •17.3 Кди в накопителях на жестких дисках, cd-rom- накопителях и современных микросхемах памяти.

- •18 Магистральный интерфейс agp

- •19 Режимы работы процессора

- •19.1 Введение в многопроцессорные системы.

- •19.2 Режимы работы процессора .

- •19.3 Синхронизация элементов компьютерной системы.

- •Лекция20

- •20. Разновидности микросхем памяти.

- •21. Организация и функционирование микросхем памяти

- •22. Организация памяти 32х разрядных процессоров.

- •Некоторые варианты подключения средств диагностирования к пк

21. Организация и функционирование микросхем памяти

При разработке микросхем памяти существует 2 взаимосвязанные проблемы :

- увеличение объема памяти

-минимизация количества выводов в микросхеме

Эти противоречия решаются 2мя путями :

Размещение запоминающих устройств в виде матрицы

Мултиплексирование неиспользуемых линий шины адреса для строк и столбцов .

21.1 Организация динамическим микросхем

21.2 Составные элементы ОЗУ .

22.3 Принцип адресации микросхем памяти 32 двух разрядными процессами .

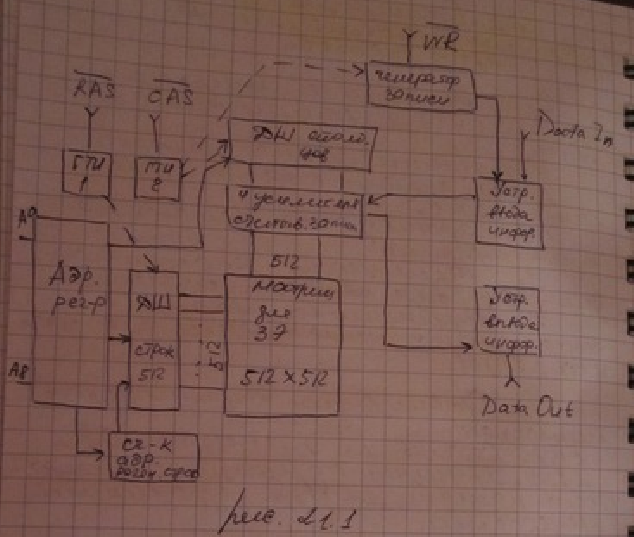

21.1 Упрощенная структурная схема памяти рис . 21.1

Матрица запоминающих элементов 512х512 содержит 262 144 ячекипамти (256 Кбит)

В микросхемах памяти запоминающие элементы сгрупированы в матрицу(в данной схеме 512х512). Схема управления состоит из 2х ГТИ (ГТИ1 и ГТИ2), которые запускают в работу сигналы RASи CAS.Для выбора любой из 252 ^144 ячеек памяти требуется 18р. Код – 256кбит. В данной схеме адр. Код подается на 24 разр. адресный регистр в мультиплексном режиме .

Сначала 9 младших разр . с шины адреса , которая используется для выбора нужной строки , под. Адрес строки поступает на ДШ строки по адресному сигналу RAS и запоминается в ДШ строк затем на те же адресные входа А0-А8

Поступают 9 старших разрядов кодов , которые соответствуют адресу столбца,

Запоминается в ДШ столбцов по разр. Сигналу CAS.

К моменту приема адреса столбца на выходе ДШ строк фиксируется вст . строка. Фиксация сохраняется на время действия сигнала RAS.

Устройства ввода\вывода информации служат для приема вх. информации и вывода считываемой информации . Они так же реализуют задачу сопряжения с внешними устройствами . При записи информации она поступает в устройство ввода информации и запоминается там по разреш. сигналу CAS , пост. В ГТИ и генератора записи - RW. При активном сигнале RAS .

Применение мультиплексирования позволяет при сохранении высокого быстродействия получать максимально высокую информационную плотность и разместить данную микросхему в стандартном 86и выводном корпусе.

Т. 21.1

Емкость |

Размер матрицы |

Кол-во адр. вх. |

Упр. вход. |

Инф. вх. |

питание |

Кол-во выводов |

16к |

128х128 |

7 |

3шт. |

2шт. |

2вх. |

14 |

64к |

256х256 |

8 |

W |

Dout |

+5В |

15 |

256к |

512х512 |

9 |

RAS |

Din |

земля |

16 |

1м |

1024х1024 |

10 |

CAS |

W\R |

|

17 |

4м |

2048х2048 |

11 |

|

|

|

18 |

16м |

4096х4096 |

12 |

|

|

|

19 |

64м |

8192х8192 |

13 |

|

|

|

20 |

Режимы работы микросхем памяти

Поясним в табл . 21.2 . Микросхема памяти раб. В 3х режимах: запись , чтение , регенерация .

Т.21.2

Вход |

Выход |

Режимы работы |

RAS CAS WR Din |

Dout |

1 |

1 |

V |

V |

Rвх->∞ |

Схема не выбрана |

1 |

Ø |

V |

V |

Rвх->∞ |

Схема не выбрана |

Ø |

1 |

V |

V |

Rвх->∞ |

Регенерация |

Ø |

Ø |

Ø |

Ø v1 |

Rвх->∞ |

Запись |

Ø |

Ø |

1 |

V |

Øv1 |

Считывание |

В режиме регенерации осуществляется псевдочтение без выхода на шину данных.

Т.О. запоминающее устройство может работать в зх режимах:

-считывание

-запись

-регенерация

В режиме считывания после срабатывания дешифратора столбцов одновременно вывод. 4 числа на усилитель считывания \записи , выбирается 1 из усилителей по адр. вход. и данные -> выход. буфер.

При записи данные поступают на вход ДIи по разрешающим сигналам CASи WR информация поступает усилитель считывания \ записи . Требуемый усилитель выбир. по комбинациям А3-А6 – адр. входов усилителей и через столбцовые ключи записывается в выбранный элемент памяти.

21.2 Для управления банками памяти используют следующие элементы ОЗУ:

-мультиплексор адреса

-ЛУ памятью

-буфер данных

-логика контроля паритета

Рис. 21.2

Банк памяти – ПРУ может обращаться к любым ячейкам памяти , указав ее адрес на считывание и запись. Для получения требуемой величины емкости микросхема делится на банки . Каждый банк компануется определенным образом , в зависимости от внутренней организации . Если однобитрыемикросх. – кол-во 8 , обязательно одна из микросхем – контроль четности .

MUX адр . использ. опред. адр.:

Сигналы формирует адр. памяти для выбора нужных ячеек.

Логика упр. памятью - управление процессом чтения и записи , форм. Стробы CAS и RAS , сигналы ADRSEL, по которым MUX переключается с выбора строки на выдачу адреса столбца и после этого выдает строб адр. столбца CAS.

Логика выроб. сигнал запись и чтение.

21.3 32х разрядный процессор позволяет адресовать 4 Гб , ШД – 64 разрядная т.е. для нормальной работы необходимо реализовать 8 байт . Для задания требуемого № байта необходимо использовать 3 адр. разр. А0-А2 , оставшиеся 29 разрядов распределяются между адр. входами микросхемы , являются мультиплексными и ДШ ад. банке . Конкретное распределение этих адресов зависит от использ. модулей памяти .

Задача адрес. сводится к распределению адресов между данными памяти ОЗУ и требуемым байтом .

Последователность решения этой задачи сводится к следующему :

Т.к. адресов . может любой из 8 байт , то младшие разряды шины адреса (3 разр.) отводятся для выбора требуемого байта , т.е. комбинация на этих шинах адреса означает какой из байт требуется ПРЦ .Оставшиеся разряды необходимо распределить (А3-А31) между микросхемами ОЗУ и банками памяти .

Выделение или расчет требуемого количества адресов для микросхем ОЗУ.

Исходя из расчитываемого объема ОЗУ , определение кол-ва адресов выполняется в слдеующей последовательности :

А) Например ОЗУ имеет емкость =32 мб т.к. за один адресный цикл адр. 8 байт, то фактическое кол-во адресов для адресации 8 байт составит :

32мб/8байт= 2^22 адр. линий .

А3-А24 -22 линий цикла адреса

Получен .разр. Распределяется поровну :

Младшие А3-А13 для адресации требуемой строки по синхросигналу RAS.

Старшие А14-А 24 – для адресации требуемого столбца по сигналу CAS.

Оставшиеся разряды используются для адресации к требуемому банку памяти.

А25- А31 – номер банка.

4Гб = 2^3 –номер байта

2 ^22 –для выбора ячейки памяти

2^7 –под номер банка .

Сумма = 2^32.

Структурная схема распределения адресов :

При расчете может получиться нечетное кол-во адресов , отводимое под ОЗУ

В этом случае расчитываемый объем ОЗУ компонуется модулями. Требу. ОЗУ реализуется на 2х модулях , что бы было четное кол-во адресов .

Четный ряд: 32,64, ,128, 256,512 , 1024 , 2Гб, 4Гб.

В ДП: 1) Расчит. Требуемый объем ОЗУ, выбирается тип модулей :

2) Обосновывается арх. кеш памяти ,расчитываются параметры кеша .

3) Выбирается микросхема кеш памяти .