- •Тема 1 Общая методология происхождения скс

- •Основные понятия и определения

- •Принципы системного подхода

- •Жизненные цикла изделия, системы

- •Назначение скс, состав и структура

- •1.5 Принципы создания систем

- •1.6 Стадии и этапы создания

- •1.7 Требования к содержанию, виды и комплектность документов

- •Тема 2 Кеш-память

- •2.1 Назначение и типы кеш-памяти

- •2.2 Архитектура кеш-памяти

- •2.2.1 Кеш прямого отображения

- •2.2.2 Полностью ассоциативная архитектура

- •2.2.3 Наборно(Частично)-ассоциативная архитектура

- •2.3 Методы записи, целостность данных

- •2.4 Методика расчета кеш-памяти

- •Методы подключения средства диагностирования компа и общие принципы разработки уст-в сопряжения.

- •4.2 Сравнение вариантов подключения средства диаг-ния к компу

- •Основные ф-ии уст-ва сопряжения и релиз-я основных видов совместимости

- •Сравнение методов реализации ф-ий устр-в сопряжения

- •5. Организация обмена информацией между процессорами и внешними устройствами

- •5.1 Организация ввода-вывода

- •5.2 Методы управления вводом-выводом

- •5.3 Типовая структура контроллеров

- •6. Контроллеры внешних устройств

- •6.1 Особенности графического изображения временных диаграмм

- •6.2 Структурная и функциональная организация контроллеров

- •6.3 Типовые структуры контроллеров

- •8 Лекция (5.10.2011)

- •8.1 Синхронные последовательные интерфейсы

- •8.2 Контроллер последовательной синхронной передачи, схема, алгоритм, подпрограмма.

- •8.3 Контроллер последовательного синхронного приема.

- •9 Лекция (10.10.2011)

- •9.1 Асинхронный последовательный контроллер передачи информации из пк в сд.

- •9.2 Контроллер последовательного асинхронного приема информации из сд в пк.

- •Проектирование подсистем ввода аналоговой информации

- •12. Построение подсистемы ввода аналоговой информации

- •12.1 Анализ структурных схем

- •12.2 Пример схем модуля аналогового вывода

- •12.1 Анализ структурных схем

- •12.2 Пример схем модуля аналогового вывода

- •13. Рекомендации по выбору компонентов системы вв/выв аналоговой информации

- •13.2 Проблемы, возникающие при дискретизации и последующем восстановлении.

- •13.3 Выбор параметров ацп.

- •Тема 15 Последовательная шина usb (Universal Serial Bus)

- •15. 1 Структура и взаимодействие системы usb

- •15. 2 Физический интерфейс

- •Тема 16 Особенности использования usb, обмен инфо-

- •16.1 Организация обмена инфо-

- •16. 1.1 Модель передачи данных

- •16.1.2 Типы передаваемых данных

- •16. 1.3 Протокол и форматы пакетов

- •16.2 Модификации usb

- •17. Контроль достоверности информации(кди) в скс.

- •17.1 Кди в микросхемах озу небольшого объема и при последовательном варианте обмена информацией.

- •17.2 Кди в накопителях на гибких дисках и кмоп-памяти.

- •17.3 Кди в накопителях на жестких дисках, cd-rom- накопителях и современных микросхемах памяти.

- •18 Магистральный интерфейс agp

- •19 Режимы работы процессора

- •19.1 Введение в многопроцессорные системы.

- •19.2 Режимы работы процессора .

- •19.3 Синхронизация элементов компьютерной системы.

- •Лекция20

- •20. Разновидности микросхем памяти.

- •21. Организация и функционирование микросхем памяти

- •22. Организация памяти 32х разрядных процессоров.

- •Некоторые варианты подключения средств диагностирования к пк

19.2 Режимы работы процессора .

16-ти разрядные процессоры работают в реальном режиме.

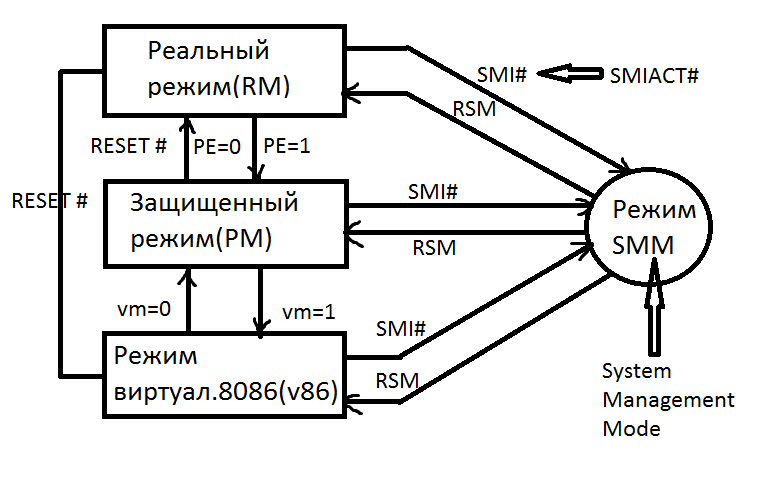

Граф перехода

между режимами

процессора

Первоначально в 16-разрядном процессоре был реальный режим, в которой доступна память=1Мбайт, шА=20 разрядов.

Память разбивается на сегменты: кода, данных, стека.

Для того, чтобы сегменты не наезжали друг на друга , за ними следит программист.

В последующих 32-разрядных процессорах реализуется защищенный режим. Поддерживается реальный режим и виртуальный.

Виртуальный – это несколько процессоров 16-разрядных, но с возможностью доступа к 4 Гбайтам.

Память делится на страницы, защищенность означает, что предусмотрены специальные средства с целью устранения недостатков реального режима. Для этого исп-ся специальные указатели-дескрипторы – сегмент до 4 Гбайт.

Кроме сегментации памяти предусмотрен постраничный режим. Реализуется защищенный режим с помощью уровней привилегий.

Этот режим предназначен для выполнения некоторых действий с возможностью изоляции от прикладного программного обеспечения.

Основное предназначение – реализация системы управления энергопотреблением.

В режиме SMM система может перейти по сигналу SMI. Сигнал SMI является запросом прерывания с наивысшим приоритетом. Получив этот сигнал процессор завершает текущую инструкцию и вырабатывает сигнал SMI ответный.

Процессор сохраняет свой контекст в специальной памяти SMRAM – это выделенная область физической памяти, доступ к которой обеспечивается внешними схемами в целях обращения к памяти при наличии сигнала SMIACT#.

После сохранения контекста процессор переходит к выполнению обработчика SMI, который расположен в этой специальной области.

Обработчик – это последовательность инструкций, который выполняются процессором в реальном режиме.

При нахождении в SMM запрещаются все аппаратные прерывания, а также исключения.

Процедура обработки заканчивается сигналом RSM. Но этому сигналу процессор устанавливает свой контекст из образа, который хранится в памяти, и возвращается в предыдущий режим.

19.3 Синхронизация элементов компьютерной системы.

Работа всех элементов компьютерной системы осуществляется синхросигналами, которые вырабатываются генератором на системной плате. Эта частота умножается на определенной число и делится для обеспечения частоты системной шины ISA(8 МГц) , а также другие контроллеры системной платы(com,LPT,системный таймер).

Лекция20

20. Разновидности микросхем памяти.

В КС различают следующие виды памяти: память процессора, внутренняя и внешняя память. Память процессора включает регистры общего назначения, сегментные регистры, регистры команд, внутренний кеш.

Внутренняя память это ОП или ОЗУ, КМОП память.

К внешней памяти относят гибкие, жесткие и флеш-память, регистры передающих устройств, видеопамяти, CD-ROM.

20.1 Быстродействие процессора и памяти:

Быстрод. Проц. Мгц |

Быстр. Сист. Шины. Мгц. |

Тип Памяти |

Быстрод. Памяти, Мгц |

Дата. |

5-200 |

5-66 |

FPM/EDO |

5-16 |

1981-1996 |

200-450 |

66-100 |

SDRAM |

66-100 |

1997-1998 |

500+ |

100+ |

RDRAM |

600-800 |

2000+ |

Быстродействие процессора выражают в единицах частоты Мгц, а быстродействие памяти - в нс. Существуют специальные таблицы, которые устанавливают зависимость между нс и Мгц. Например частота 10Мгц – цикл 100нс. 100Мгц – 10нс. 500Мгц – 2нс. 1Ггц – 1нс.

За одну нс световой луч проходит 30см. Как видно из таблицы один и тот же тип памяти использовался в течении 15 лет, а производительность процессора увеличилась в 40 раз, а производительность памяти осталась на месте. Поэтому появилась необходимость в использовании новых микросхем памяти.

С увеличением частоты продолжительность цикла уменьшается. Рост тактовой частоты в 100 раз в 100 раз уменьшает цикл.

Быстродействие памяти составляет 60нс, поэтому процессор вынужден простаивать. Обычно адресация в микросхемах памяти сводится к следующему: выбирается строка (элементы в виде матрицы) а затем столбец, и после этого передаются данные. Время, затраченное на поиск строки и столбца называется временем задержки. Время доступа = время задержки + время цикла.

Память с временем доступа 60 нс имеет время задержки 25 нс и продолжительность цикла 35 нс, шаговая частота памяти 30 Мгц.

Если процессор работает на частоте 300 Мгц то он вынужден оставаться в ожидании 10 циклов до поступления данных. Для уменьшения времени ожидания были разработаны определенные типы микросхем.

20.2.1

FPM – Fast Page Memory – быстрый постраничный режим. С целью сокращения времени ожидания память DRAM разбивают на страницы, благодаря этому обеспечивается более быстрый доступ к данным в пределах строки. Длина строки от 512 байт до нескольких кб. Специальная схема поиска страниц позволяет при обращении к ней кеш-памяти в пределах страницы уменьшить состояние ожидания. В дополнение к этому был разработан так называемый пакетный burst режим доступа. Сущность этого режима сводится к следующему. Обычно в большинстве случаев доступ к данным является последовательным, поэтому после установки строки и 1го столбца адреса в пакетном режиме можно обращаться к 3м адресам столбца без дополнительного состояния ожидания. Схема синхронизации в пакетном режиме для стандартных DRAM с временем доступа 60 нс 5-3-3-3, где цифры означают циклы. 1 операция доступа к данным – 5 циклов на системной шине, 2 последовательных операции по 3 цикла.

Без пакетного режима и разбивки на страницы - схема 5-5-5-5. Память поддерживает постраничный или пакетный режим.

Иногда для получения быстродействия FPM применяют разбиение ОП на 2 банка и при обращении к одному из банков в другом выбирается строка и столбец, поэтому цикл ожидания уменьшается.

20.2.2 Дальнейшим шагом получения быстродействия микросхем памяти в процессорах Pentium было использовано EDO – Extended Data Out. Это усовершенствованный вариант FPM. В специальных микросхемах памяти учитывается перекрытие синхронизации между очередными операциями доступа. Последний цикл совмещается с предыдущим и это позволяет в пакетном режиме добиться схемы 5-2-2-2.

20.2.3 SDRAM – Synchronus DRAM. Это новый тип памяти, однако так как она является динамической то ее начальное время ожидания такое же как в FPM и EDO. Но общее время цикла намного короче. Схема синхронизации пакетного доступа 5-1-1-1. Эта память работает на высоких частотах 5Мгц и выше. Начиная с SDRAM быстродействие микросхем оценивают в Мгц а не в нс.

20.2.4 RDRAM – относится к новому типу микросхем памяти. Rambus DRAM.

Данный тип использовался с 1999 года. Быстродействие этой памяти сравнимо с быстродействием процессора. Обычные типы памяти имеют разрядность данных равную разрядности шин процессора – 64бит = 8 байт что соответствует максимальному быстродействию на частоте 100 Мгц. – 800 Мб/сек.

Используют также низковольтные сигналы что существенно снижает потребляемую мощность. Логические «0» - 1В. «1» - 1.8В.

Как и в модулях SDRAM. В модулях RDRAM устанавливаются специальные ПЗУ, которые содержат информацию о размере и типе модуля. Каждый модуль может комплектоваться 4,8,16 RDRAM-микросхем.

SDRAM модули – DIMM

RIMM - Rambus Inline Memory Modules.

Соответственно имеют различное число контактов, в частности модуль RIMM – 184 позолоченных контактов (по 92 на стороне). Работой микросхем управляет специальный контроллер SDRAM, частота синхронизации 400 Мгц.