- •Тема 1 Общая методология происхождения скс

- •Основные понятия и определения

- •Принципы системного подхода

- •Жизненные цикла изделия, системы

- •Назначение скс, состав и структура

- •1.5 Принципы создания систем

- •1.6 Стадии и этапы создания

- •1.7 Требования к содержанию, виды и комплектность документов

- •Тема 2 Кеш-память

- •2.1 Назначение и типы кеш-памяти

- •2.2 Архитектура кеш-памяти

- •2.2.1 Кеш прямого отображения

- •2.2.2 Полностью ассоциативная архитектура

- •2.2.3 Наборно(Частично)-ассоциативная архитектура

- •2.3 Методы записи, целостность данных

- •2.4 Методика расчета кеш-памяти

- •Методы подключения средства диагностирования компа и общие принципы разработки уст-в сопряжения.

- •4.2 Сравнение вариантов подключения средства диаг-ния к компу

- •Основные ф-ии уст-ва сопряжения и релиз-я основных видов совместимости

- •Сравнение методов реализации ф-ий устр-в сопряжения

- •5. Организация обмена информацией между процессорами и внешними устройствами

- •5.1 Организация ввода-вывода

- •5.2 Методы управления вводом-выводом

- •5.3 Типовая структура контроллеров

- •6. Контроллеры внешних устройств

- •6.1 Особенности графического изображения временных диаграмм

- •6.2 Структурная и функциональная организация контроллеров

- •6.3 Типовые структуры контроллеров

- •8 Лекция (5.10.2011)

- •8.1 Синхронные последовательные интерфейсы

- •8.2 Контроллер последовательной синхронной передачи, схема, алгоритм, подпрограмма.

- •8.3 Контроллер последовательного синхронного приема.

- •9 Лекция (10.10.2011)

- •9.1 Асинхронный последовательный контроллер передачи информации из пк в сд.

- •9.2 Контроллер последовательного асинхронного приема информации из сд в пк.

- •Проектирование подсистем ввода аналоговой информации

- •12. Построение подсистемы ввода аналоговой информации

- •12.1 Анализ структурных схем

- •12.2 Пример схем модуля аналогового вывода

- •12.1 Анализ структурных схем

- •12.2 Пример схем модуля аналогового вывода

- •13. Рекомендации по выбору компонентов системы вв/выв аналоговой информации

- •13.2 Проблемы, возникающие при дискретизации и последующем восстановлении.

- •13.3 Выбор параметров ацп.

- •Тема 15 Последовательная шина usb (Universal Serial Bus)

- •15. 1 Структура и взаимодействие системы usb

- •15. 2 Физический интерфейс

- •Тема 16 Особенности использования usb, обмен инфо-

- •16.1 Организация обмена инфо-

- •16. 1.1 Модель передачи данных

- •16.1.2 Типы передаваемых данных

- •16. 1.3 Протокол и форматы пакетов

- •16.2 Модификации usb

- •17. Контроль достоверности информации(кди) в скс.

- •17.1 Кди в микросхемах озу небольшого объема и при последовательном варианте обмена информацией.

- •17.2 Кди в накопителях на гибких дисках и кмоп-памяти.

- •17.3 Кди в накопителях на жестких дисках, cd-rom- накопителях и современных микросхемах памяти.

- •18 Магистральный интерфейс agp

- •19 Режимы работы процессора

- •19.1 Введение в многопроцессорные системы.

- •19.2 Режимы работы процессора .

- •19.3 Синхронизация элементов компьютерной системы.

- •Лекция20

- •20. Разновидности микросхем памяти.

- •21. Организация и функционирование микросхем памяти

- •22. Организация памяти 32х разрядных процессоров.

- •Некоторые варианты подключения средств диагностирования к пк

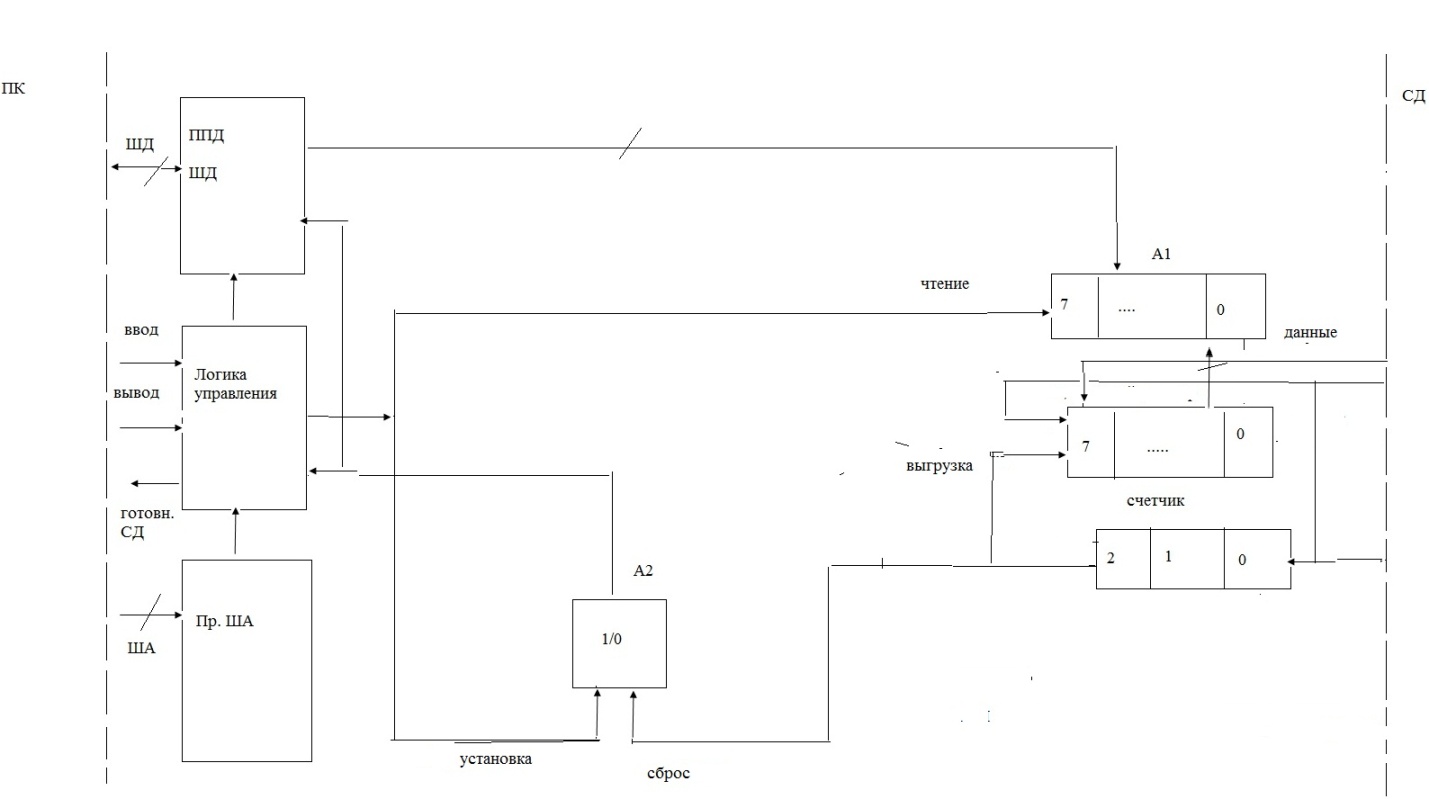

8.3 Контроллер последовательного синхронного приема.

Контроллер последовательного синхронного приема данных из СД состоит из тех же блоков, кроме ГТИ.

Подпрограмма: (под вопросом)

M1 TST, @#A2

BPL M1

MOV А1, @#R1

Алгоритм:

Процессор циклически опрашивает состояние регистра А2. В цикле «ввод» на ША выставляется адрес А2 и с помощью логики управления считывает состояние А2.

Если А2=1 переход М1, если А2=0, то старший разряд ШД положит. Процессор считывает данные с А1.

9 Лекция (10.10.2011)

Асинхронные последовательные интерфейсы

Особенность асинхронного обмена информацией состоит в том, что общая синхронизация между ПК и СД (средство диагностирования) отсутствует. На предающем и приемном конце имеются тактовые генераторы, которые настроены на одну и ту же частоту. Однако получить строго одинаковые частоты ГТИ не удается из-за влияния различных факторов. Поэтому надо рассматривать специальные меры для компенсации разбаланса частот.

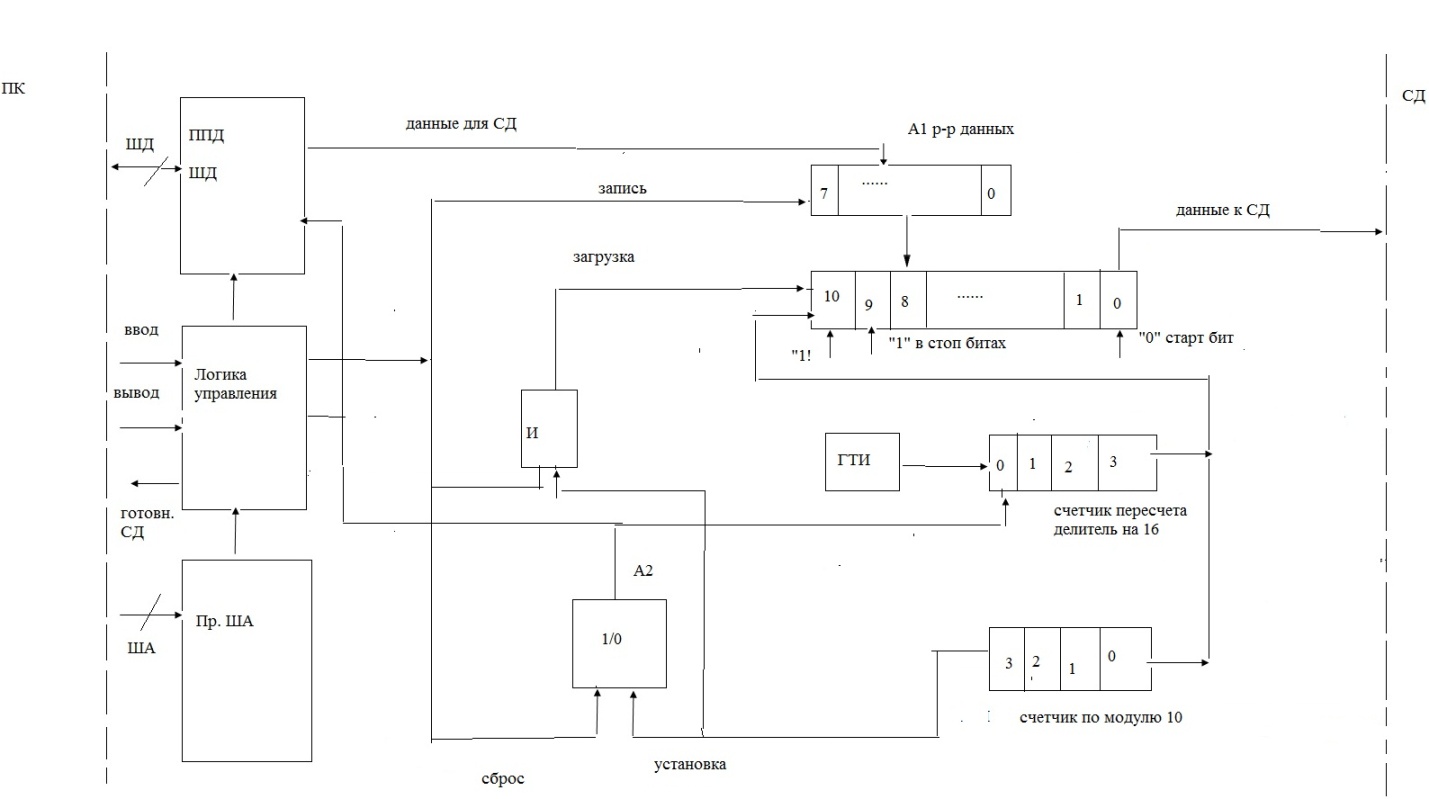

9.1 Асинхронный последовательный контроллер передачи информации из пк в сд.

Блок-схема контроллера.

Назначение блоков:

Рассматриваемый генератор предназначен для передачи данных в формате с 2 стоп битами и 1 старт битом. Он включает Пр ША, ППД ШД и ЛУ. Буферный регистр А1, регистр состояния и управления А2 (триггер), ГТИ, делитель частоты на 16, счетчик по модулю 10, логическая схема «И».

Работа схемы:

После передачи очередного байта данных в А2 записывается «1» (установка-вход). Единица выходного сигнала счетчика по модулю 10 подготавливает схему «И». Наличие «1» в А2 информирует процессор о готовности контроллера к приему следующего байта данных и передачи его по линии связи к СД. Этот же сигнал «1» на А2 запрещает работу делителя на 16! Процесс передачи очередного байта начинается с того, что процессор выставляет на ШД очередной байт. Одновременно процессор формирует управляющий сигнал «вывод». ЛУ, получив сигнал «вывод» вырабатывает управляющий сигнал «запись» и по схеме «И» разрешает записываемый байт загрузить в сдвиговый регистр, тем самым байт из А1 переписывается в сдвиговый регистр. Этот же сигнал по входу «сброс» переводит А2 в 0.

Одновременно с «загрузкой» в сдвиговый регистр записывается в 0-разряд 0, а в 9,10 разряды -1. Наличие «0» на выходе А2 разрешает работу делителя частоты на 16. Делитель начинает накапливать импульс, поступающий в ГТИ. И в прием 16 импульса вырабатывает 1 сдвиговый импульс. Этот импульс выдает в линию данных стартовый бит. Значение старшего бита в линии данных поддерживается в линии данных до прихода очередного импульса сдвига. Этот импульс перепишет в 0-рязряд сдвигового регистра 1ый бит данных. Это продолжится до передачи всех информационных бит. После этого передаются 1ый и 2ой стоп биты. После счетчик по модулю 10 вырабатывает сигнал, который переводит А2 в 1 и подготавливает схему «И», т.е. контроллер переходит в режим ожидания. В линии поддерживается логическая «1». После этого процесс повторяется.

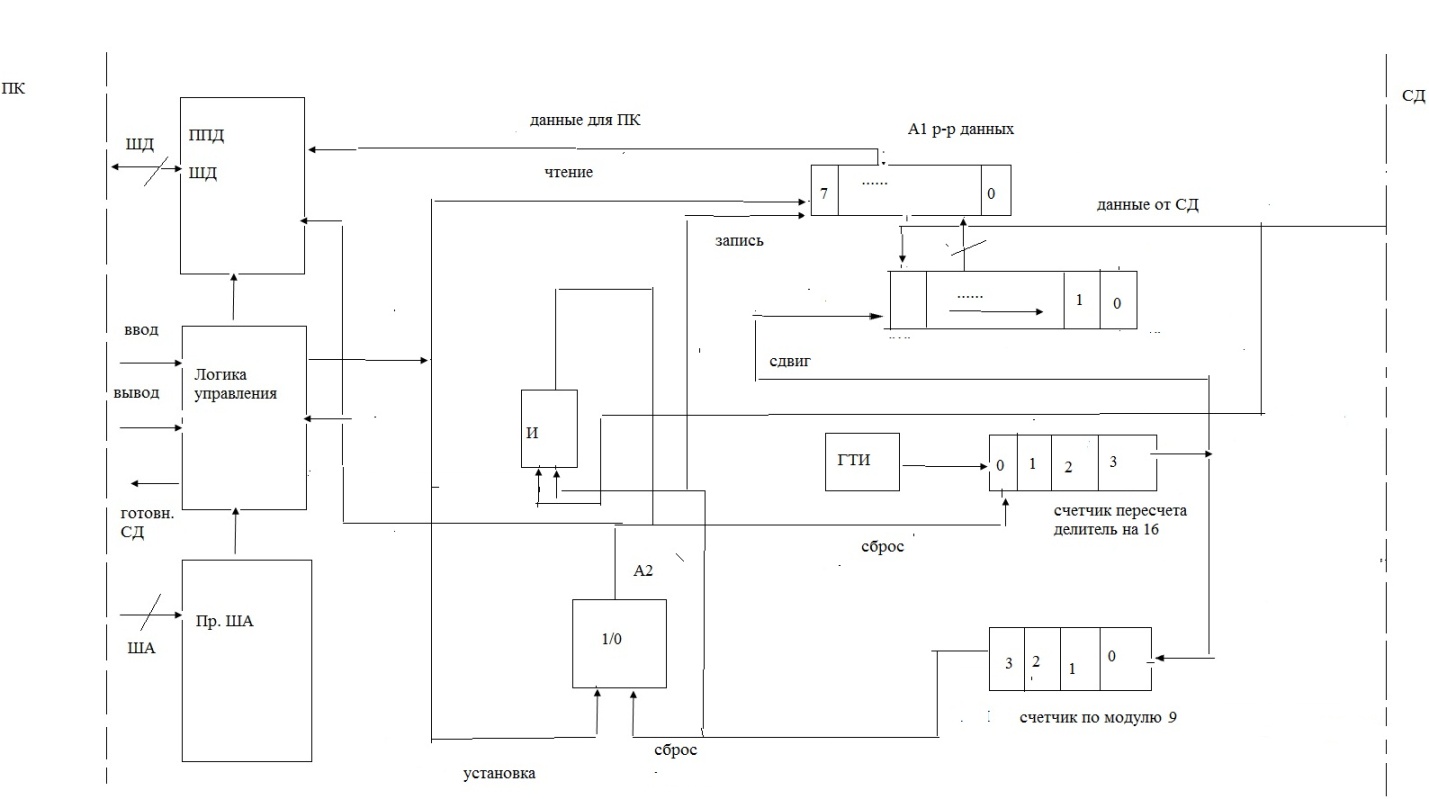

9.2 Контроллер последовательного асинхронного приема информации из сд в пк.

Блок-схема.

В отличие от предыдущей схемы на схему «И» на вход поступают данные от СД.

Работа схемы аналогична работе пред. схемы. Отличие: уровень логической «1», поступающие из линии «данные», запрещает работу делителя частоты на 16. После перехода счетчик по модулю 19 в единичное состояние. 1 со схемы «И» запрещает работу делителя на 16. Как только линия переходит в стартовый режим логического 0, схема «И»=0, запускает делитель частоты на 16. Сдвиговый регистр имеет 8 разрядов, вместо 10.

Особенность асинхронной передачи: ГТИ приемника и передатчика работают независимо. Частоты одинаковы. Для уменьшения вероятности ошибки из-за возможного различия частот вводится делитель частоты на 16, т.е. считывание производится примерно на середине временного интервала, отведенного на выработку 16 тактовых импульсов.

Асинхронный режим поддерживает микросхема UART, в современных системах интегрирована в чипсет.

Т10. Проектир. подс-м ввода аналог. инфы в СКС

10.1. анализ стр-р подс-мы ввода аналоговой инфы

10.2. х-ка сигналов от объекта диагностир.

10.3. анализ подс-мы аналог. ввода

10.1. стр-ра определяется целью и задачами диагностир. Цель-получ. достоверной инфы от объекта диагностир. Система в общ. случ. должна содержать:

1)датчик или группу датчиков первичной инфы, кот. находится на объекте диагностир.

2)блок преобразователей аналог. сигналов в цифровые

3) соотвествующий канал связи: цифовой и\или аналог.

4)наличие ср-ва обратного преобразования цифр.в аналог.

Сущ.различные вар-ты структурн.схем

1 вар-т реализ. принцип параллельной обраб. аналог. сигнала

Для каждого отдельного датчика существует свой АЦП, что обеспечивает максим. быстрод. и высокое кач-во.

Д1

СУ

СН

ФП

АЦП1

Дn

СУ

СН

ФП

АЦПn

УМ

К ПК

Д-датчик; СУ-согласующ. устр-во;

ФП-функциональный преобр-ль ЦМ-цифров. мультиплексор;

СН-схема нормализации

Существует ф-ла для определения кол-ва каналов в структурной сх. Это кол-во ограничивается динамической погрешностью преобразований i-го параметра.

Nц=

Nц-пред. Допустим. кол-во цифровых каналов

-допустим.

значение динамич. погр-ти

-допустим.

значение динамич. погр-ти

-максим.

значение производной параметра в

измерян. диапазоне преобразований

-максим.

значение производной параметра в

измерян. диапазоне преобразований

-

период коммутации

-

период коммутации

Т.к.каналы независимы др.от друга, то относит. просто реализ-ся необходимые ф-циональные преобразования.

В дан. сх. отсутствуют ошибки, кот возникают в др. сх. при наличии одного АЦП и необх-ти введения сх. выборки хранения.

Др. вар-ты схем основаны на принципе последовательной обработки аналогов. сигналов(исп.аналоговый мультиплексор), а также необходимо наличие сх. выборки хранения.

2

вх

АМ

вх

АЦП

УУ

-ой вар-т сх.

К ПК

Существует ф-ла, кот. позволяет определить максим. допустимое кол-во датчиков.

Nа<= -период коммутации;

-период коммутации;

-период

цикла

-период

цикла

В дан. сх. быстродействие сбора данных ниже, т.к. оно определяет АЦП, а применение аналог. мультиплексора и сх. выборки хранения ухудшает точностные характеристки.

Возможно построение структ. сх. с использованием 1 сх. выборки хранения

АМ

в\х

УУ

АЦП

К ПК

Е

АМ

СУ

УУ

в\х

АЦП

сли датчики однотипные и имеют одинак. сигналы, они могут быть поданы на вх. Аналог. мультиплексора

К ПК

Любой вар-т структурн.сх.реализ-ся из следующих осн. устр-в: датчиков, сх. согласования, сх. нормализации АЦП, цифров. или аналог. мультипл. или устр-ва управл.

10.2.

Входн. сигналы от объекта диагностики должны быть нормированы. В общем случае они могут быть аналоговыми или дискр.

Вх. сигн. от объекта диагностики

Аналогов.

Низк.ур.

Дискр.

Средний ур.

0-100мВ(термопара) -5-0+5мА 0-5В;-5В-0В

0-300Ом(датч. сопротивл.) -5-0+5В 0-12В;-12В-0В

0-5мГн(индуктив-ть) -10-0+10В 0-24В;-24-0В

0-48В;-48В-0В

0-бесконечность Ом(сухой контакт)

1

УСЗ

ПУ

ИД

АЦП

Д

У

Ф

К

0.3.

0.3.

У-усилитель; Ф-фильтр, необходимый, чтобы убрать высокочастотную составляющ.

К-коммутатор(мультиплексор)

УСЗ-устр-во слежения запоминания(сх. выборки-хранения) при подаче на вход АЦП сигнала, он должен быть постоян. за весь период преобразования.

ИД-интерф. дискр. ввода и интерф. управления.

Существуют готовые модули, с помощью кот. реализ. ввод аналогов. сигн. в ПК.

1 из вар-тов имеет особ-ти:

Парам-р х-ки

1.число разр(ЦП) 11(вместе со зн.)

2.время преобраз. 100мкс

3.число рег-ров 3

4.Uвх.В +- 1В или +-10В

Данный модуль позволяет подключать 16 датчиков.

АМ

АМ

Д1

Д16

Д8

Д1

0

7

8

15