6.1. Организация ячейки памяти на запоминающем элементе rs триггер

RS триггер является элементарным регистром, у которого имеется 2 входа R и S, по которым он может быть установлен в единичное или нулевое состояние, как показано на рис 6.1.

Рис. 6.1. «ячейка памяти на RS триггере»

На рис.6.1. обозначено:

хD-входной бит данных (хD Є 1,0)

хзп- строб записис входного бита

хчт- строб считывания запомненной информации

z – запомненное состояние триггера

z- считываемое значение сохранённых данных в стробе чтения

Предполагается, что выборка, запись, и извлечение информации осуществляется в стробах чтения/записи, а информация, сохранённая в RS триггере может изменяться в стробе записи, если входной бит имеет противоположное значение, как это показано на рис. 6.2.

Рис. 6.2. Временная диаграмма ячейки памяти

хЗП∙хD ├ z

хЧТ∙ z ├ z чт ф. 6.1.

На временной диаграмме в тактах дискретного времени последовательно записывается, сохраняется, и извлекается информация в соответствующих стробах записи и чтения.

По сути, в 2-х тактном режиме записи/чтения, и этот процесс для наглядности можно представить в сиквенциальной формуле 6.1.

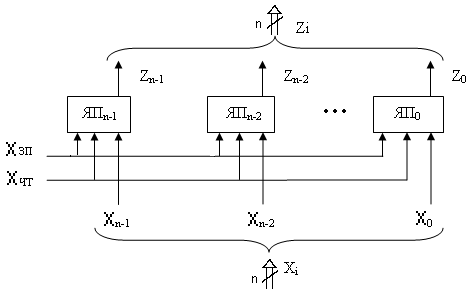

Эту регулярную структуру (ячейку памяти) можно расширить (нарастить) до n-разрядного машинного слова, где запись и чтение будет осуществляться параллельно по всей линейке n- разрядного слова, как это показано на рис. 6.3.

Рис. 6.3. Регистр n- разрядного машинного слова

хЗП∙Хi ├ Zi

хЧТ∙ Zi ├ Zi ф. 6.2.

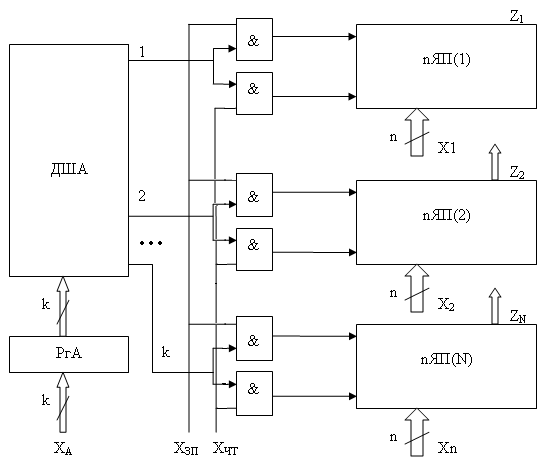

Рис.6.4 Адресная выборка машинных слов

Соответственно, регулярность в наращивании памяти можно распостранить на массив машинных слов с фиксированным их количеством выбираемых по адресу, значение которого соответствует номеру выбранного слова из массива. При этом в структуру памяти добавляется регистр адреса (РгА) на k разрядов, объединённый с дешифратором адреса, который преобразует каждую кодовую адресную комбинацию в стробирующий сигнал (1,2,3…2k), который в свою очередь является стробом записи или чтения содержимого соответствующего массива памяти. Так как запись и чтение в такте машинного слова осуществляется только для одного выбранного n-разрядного регистра, то магистрали данных (XD, ZD)можно объединить в общие магистрали входных и выходных данных.

Индуктивно можно распостранить дальнейшее расширение памяти, как показано на рис. 6.4., организуя соответствующие адресные выборки массивов (страниц), организованных из страниц, разделов, томов, книг, библиотек, и т.д.

Рассмотренная организация памяти позволяет реализовать все процедуры (записи, хранения, извлечения) в оперативном режиме с изменением данных в каждом такте работы ЦВМ.

Такая структура характерна для ОЗУ, но в практике разработок средств вычислительной техники бывает целесообразно изменять универсальный принцип организации памяти, для чего она может быть реализована на элементах, позволяющих осуществлять однократный цикл записи, с неизменными данными (например, тестирование). В свою очередь, память такого рода может быть с однократной записью, не позволяющей вносить какие- либо изменения после их записи, и перепрограммируемые., когда данные для длительного хранения могут быть изменены в процессе модернизации используемого оборудования (например, машинная память BIOS).