- •1. Принципы построения и основы работы

- •2. Элементная база мпсу

- •3. Оперативные запоминающие устройства.

- •4. Постоянные запоминающие устройства.

- •5. Архитектура микропроцессора типа кр580вм80

- •6. Типы машинных циклов и слово состояния

- •7,8. Командные циклы чтения/записи

- •9. Командный цикл подтверждения прерывания.

- •10. Принципиальные электрические схемы

- •11,12. Интерфейс мпсу с изолированной системой шин

- •13. Интерфейс мпсу с общей системой шин

- •14. Организация обслуживания запросов прерывания

- •15. Программируемый контроллер

- •17. Программируемый контроллер прерываний

- •18. Функциональная схема пкп. Настройка режимов работы

- •19. Программируемый интервальный таймер

- •21. Мпсу с вводом-выводом аналоговой информации

- •22. Выходные каскады мпсу

- •Дворак Николай Маркович микропроцессорные устройства

- •В высших учебных заведениях 3-4 уровней

- •98309, Г. Керчь, ул. Орджоникидзе, 82

- •98309, Г. Керчь, ул. Орджоникидзе, 82

2. Элементная база мпсу

Шинная

структура МПСУ, модульное подключение

памяти и внешних устройств и организация

связей между ними и МП предъявляет

особые требования к элементной базе,

на которой строятся МПСУ. Основное

требование состоит в том, чтобы все

микросхемы памяти и ВУ, с которых

информация передается в МП, были бы

трехстабильными. Трехстабильность

означает, что выходной сигнал, кроме

двух стандартных для всех цифровых

микросхем значений 0 и 1, имеет еще третье

выключенное состояние, называемое еще

как Z-состояние высокого сопротивления,

когда ножка микросхемы отключена как

от земли, так и от источника питания

![]() .

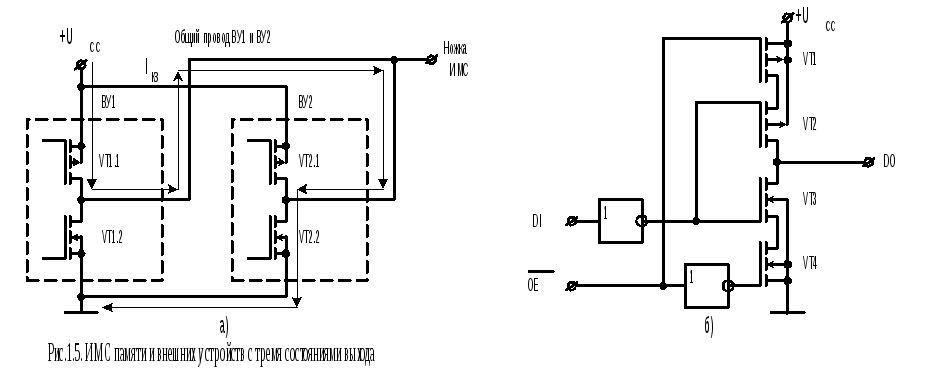

Это требование поясняется схемой,

приведенной на рис.1.5а.

.

Это требование поясняется схемой,

приведенной на рис.1.5а.

Е![]()

сли

ВУ1 выдает на ШД сигнал уровня 1, а ВУ2

выдает в то же время на ШД сигнал уровня

0, то через открытые в этом случае

транзисторы VT1.1 и VT2.2 проходит ток

короткого замыкания IКЗ, который

сожжет оба транзистора. В связи с этим

выходные каскады микросхем памяти и ВУ

выполняются по схеме, приведенный на

рис.1.5б. Для того чтобы входной сигнал

DI, который может принимать два значения

– 0 или 1, был передан на выход DO, на вход

сли

ВУ1 выдает на ШД сигнал уровня 1, а ВУ2

выдает в то же время на ШД сигнал уровня

0, то через открытые в этом случае

транзисторы VT1.1 и VT2.2 проходит ток

короткого замыкания IКЗ, который

сожжет оба транзистора. В связи с этим

выходные каскады микросхем памяти и ВУ

выполняются по схеме, приведенный на

рис.1.5б. Для того чтобы входной сигнал

DI, который может принимать два значения

– 0 или 1, был передан на выход DO, на вход

![]() (Output Enable – вывод разрешен) нужно подать

сигнал уровня 0. При таком сигнале

(Output Enable – вывод разрешен) нужно подать

сигнал уровня 0. При таком сигнале

![]() транзисторы VT1 и VT4 будут открыты, и

сигнал DI будет передан на вывод DO

микросхемы через один из открытых

транзисторов VT2 или VT3. При

транзисторы VT1 и VT4 будут открыты, и

сигнал DI будет передан на вывод DO

микросхемы через один из открытых

транзисторов VT2 или VT3. При

![]() =1

транзисторы VT1 и VT4 будут закрыты, и вывод

DО будет отключен как от земли, так и от

источника питания

=1

транзисторы VT1 и VT4 будут закрыты, и вывод

DО будет отключен как от земли, так и от

источника питания

![]() .

В МПСУ активный уровень сигнала

.

В МПСУ активный уровень сигнала

![]() стандартизирован и равен 0. Трехстабильные

выводы микросхем обозначаются значком

.

стандартизирован и равен 0. Трехстабильные

выводы микросхем обозначаются значком

.

На рис.1.5б приведена схема трехстабильного элемента КМОП-типа. Существуют также трехстабильные элементы ТТЛ-типа.

На рис.1.6 приведены основные большие интегральные схемы (БИС), применяемые в схемах МПСУ. Все они имеют трехстабильную шину данных.

БИС типа КР580ВА86 является двунаправленным шинным формирователем (ШФ). Подключается БИС к шинам МП с целью повышения нагрузочной способности шин. Характеристики входных и выходных сигналов:

UВХ.1≥2 В при IВХ.1=50 мкА; UВХ.0≤0,8 В при IВХ.0=-0,2 мА;

UВЫХ.1≥2,4 В при IВЫХ.1=-5 мА (порт В) и IВЫХ.1=-1 мА (порт А);

UВЫХ.0≤0,45 В при IВЫХ.0=32 мА (порт В) и IВЫХ.0=10 мА (порт А).

Режим

работы БИС КР580ВА86 определяется сигналами

выбора кристалла

![]() и направления передачи Т (Transmit

–передавать). При

и направления передачи Т (Transmit

–передавать). При

![]() =1

порты А и В выключены. При

=1

порты А и В выключены. При

![]() =0

и Т=0 осуществляется передача информации

от порта В к порту А, а при

=0

и Т=0 осуществляется передача информации

от порта В к порту А, а при

![]() =0

и Т=1 – от порта А к порту В.

=0

и Т=1 – от порта А к порту В.

Для хранения байта информации применяется БИС параллельного регистра КР580ИР82. Информация, подведенная к входному порту I регистра, переписывается в регистр асинхронно при сигнале STB=1. При STB=0 регистр хранит информацию, занесенную при STB=1. Считывание с выходного порта О регистра осуще-

ствляется

по сигналу

![]() =0.

Характеристики выходных сигналов

регистра:

=0.

Характеристики выходных сигналов

регистра:

UВЫХ.1≥2,4 В при IВЫХ.1=-5 мА; UВЫХ.0≤0,45 В при IВЫХ.0=32 мА.

Как видно, при применении регистра, имеющего большую нагрузочную

рисунок

способность, нет необходимости в применении шинного формирователя.

На рис.1.6 приведен еще ряд БИС, работа которых будет описана далее:

КР537РУ10 - статическое ОЗУ (оперативное запоминающее устройство);

КР573РФ2(5) - ПЗУ (постоянное запоминающее устройство) с ультрафиолетовым способом стирания информации;

КР580ВВ55 - программируемый параллельный интерфейс;

КР580ВН59 - программируемый контроллер прерываний;

КР580ВИ53 - программируемый интервальный таймер;

КР572ПВ4 - 8-входовой аналогоцифровой преобразователь (АЦП);

КР1108ПА32 - 8-разрядный цифроаналоговый преобразователь (ЦАП).

На рис.1.7 приведены интегральные микросхемы (ИМС) 8-разрядных (по емкости шины данных) микропроцессоров и микроконтроллера. У всех приведенных МП шины адреса и данных трехстабильные.

Характеристики входных и выходных сигналов МП типа КР580ВМ80:

UВХ.1≥3,3 В; UВХ.0≤0,8 В;

UВЫХ.1≥3,7 В при IВЫХ.1=0,15 мА; UВЫХ.0≤0,45 В при IВЫХ.0=1,4 мА.

Величины выходных токов микропроцессора малы, и поэтому всегда требуется применение шинного формирователя или регистра.

Назначение выводов МП и схема включения его в работу будут даны далее. Здесь рассмотрим особенности строения ША и ШД микропроцессоров.

У МП типов КР580ВМ80 и Z80 ША и ШД полные (соответственно 16 и 8 физических выводов корпуса (ножек) микросхемы МП) и изолированные. Недостатком такой организации ША и ШД является максимальное число выводов микросхемы – всего 24 ножки. Достоинством является простота схемы МЭВМ и максимальное ее быстродействие.

У МП типа КР1821ВМ85 ША и ШД полные и совмещенные. Число ножек этих шин равно 16, что является достоинством такой организации ША и ШД. Однако усложняется работа МЭВМ на базе этого процессора, функциональная схема которой приведена на рис.1.8. Цикл работы МЭВМ состоит из двух этапов:

1). Совмещенная шина работает в режиме ША. По единичному строб сигналу, поступающему из ШУ одновременно на регистры RGH и RGL, полный 16-разрядный адрес фиксируется в этих регистрах.

2). Совмещенная шина работает в режиме ШД. ВУ или ЗУ по сигналам, поступающим из ШУ, обмениваются информацией с МП.

Установление связи между МП и ВУ или ЗУ происходит в два этапа. Поэтому быстродействие в схеме с МП КР1821ВМ85 ниже, чем в схеме с МП, у которого ША и ШД раздельные.

Существуют также МП, у которых ША неполная (содержит 8 ножек при емкости шины 16 разрядов), и ША совмещена с ШД. Количество ножек указанных шин минимально и равно 8. Корпус такого МП имеет минимально возможное число ножек. Функциональная схема МЭВМ на базе такого МП совпадает с рис.1.8, но работа происходит в 3 этапа, за счет чего снижается до минимума производительность МЭВМ.

Установление связи между МП и ВУ или ЗУ происходит в два этапа. Поэтому быстродействие в схеме с МП КР1821ВМ85 ниже, чем в схеме с МП, у которого ША и ШД раздельные.

Рисунок

С уществуют

также МП, у которых ША неполная (содержит

8 ножек при емкости шины 16 разрядов), и

ША совмещена с ШД. Количество ножек

указанных шин минимально и равно 8.

Корпус такого МП имеет минимально

возможное число ножек. Функциональная

схема МЭВМ на базе такого МП совпадает

с рис.1.8, но работа происходит

в 3 этапа, за счет чего снижается до

минимума производительность МЭВМ:

уществуют

также МП, у которых ША неполная (содержит

8 ножек при емкости шины 16 разрядов), и

ША совмещена с ШД. Количество ножек

указанных шин минимально и равно 8.

Корпус такого МП имеет минимально

возможное число ножек. Функциональная

схема МЭВМ на базе такого МП совпадает

с рис.1.8, но работа происходит

в 3 этапа, за счет чего снижается до

минимума производительность МЭВМ:

1). Совмещенная шина работает в режиме ША, на которой выставлен старший байт АН 16-разрядного адреса. По единичному строб сигналу, поступающему из ШУ на регистр RGH, старший байт АН фиксируется в этом регистре.

2). Совмещенная шина работает в режиме ША, на которой выставлен младший байт АL 16-разрядного адреса. По единичному строб сигналу, поступающему из ШУ на регистр RGL, младший байт АL фиксируется в этом регистре.

3). Совмещенная шина работает в режиме ШД. ВУ или ЗУ по сигналам, поступающим из ШУ, обмениваются информацией с МП.

Существуют также МП, у которых ШД и ША раздельные и ША неполная (содержит 8 ножек при емкости шины 16 разрядов).

Кроме описанных БИС, в схемах МПСУ используются также простые микросхемы со следующими особенностями:

1). Триггеры простейших типов RS и D асинхронные и синхронные. Более сложные триггеры применяются чрезвычайно редко из-за того, что логику работы сложных триггеров можно реализовать в МПСУ программным путем.

2). Счетчики, работающие на сложение и вычитание, без предварительных установок. Вместо счетчиков в МПСУ целесообразно применять БИС КР580ВИ53 программируемого интервального таймера, который содержит три 16-разрядных счетчика.

3). Мультиплексоры и коммутаторы.

4). Дешифраторы таких типов, у которых активный выходной сигнал имеет уровень 0, а также существует режим отключенных выходов, когда на всех выходах дешифратора устанавливаются уровни 1.

5). Любые логические схемы комбинационного типа.

У

всех этих простых микросхем в случае

их применения в схемах сбора информации

и ввода ее в МП выход должен иметь 3

состояния – быть трехстабильным. Если

микросхемы с таким свойством нет, то к

ее выходу следует подключить описанный

выше регистр КР580ИР82, оформив соответствующим

образом сигналы, подаваемые на входы

STB и

![]() .

.