- •1. Принципы построения и основы работы

- •2. Элементная база мпсу

- •3. Оперативные запоминающие устройства.

- •4. Постоянные запоминающие устройства.

- •5. Архитектура микропроцессора типа кр580вм80

- •6. Типы машинных циклов и слово состояния

- •7,8. Командные циклы чтения/записи

- •9. Командный цикл подтверждения прерывания.

- •10. Принципиальные электрические схемы

- •11,12. Интерфейс мпсу с изолированной системой шин

- •13. Интерфейс мпсу с общей системой шин

- •14. Организация обслуживания запросов прерывания

- •15. Программируемый контроллер

- •17. Программируемый контроллер прерываний

- •18. Функциональная схема пкп. Настройка режимов работы

- •19. Программируемый интервальный таймер

- •21. Мпсу с вводом-выводом аналоговой информации

- •22. Выходные каскады мпсу

- •Дворак Николай Маркович микропроцессорные устройства

- •В высших учебных заведениях 3-4 уровней

- •98309, Г. Керчь, ул. Орджоникидзе, 82

- •98309, Г. Керчь, ул. Орджоникидзе, 82

21. Мпсу с вводом-выводом аналоговой информации

МПСУ могут управлять объектами с использованием аналоговой информации, если в состав МПСУ введены аналогоцифровые (АЦП) и цифроаналоговые (ЦАП) преобразователи.

В качестве АЦП в МПСУ целесообразно применять ИМС типа КР572ПВ4, которая обеспечивает работу по 8-ми каналам аналоговых данных и имеет стандартный интерфейс для подключения к шинам МП [6]. Функциональная схема АЦП приведена на рис.1.64. Работа АЦП тактируется синхроимпульсами CLK, частота которых равна 2,5 МГц. 8 аналоговых сигналов UBX0…UBX7 поступают на аналоговый коммутатор, который соединяет с одновходовым АЦП1 только один аналоговый сигнал AN в очередности: UBX0, UBX1,… UBX7. В течение 32 мкс сигнал преобразуется АЦП1 в цифровую форму размером 1 байт и цифровой код переписывается в соответствующую ячейку ОЗУ емкостью 8 байт. По истечении 32·8=256 мкс (8 – количество аналоговых входов) все ячейки ОЗУ будут заполнены кодами всех 8-ми входных аналоговых сигналов. Далее будет следовать обновление кодов в соответствии с текущими значениями аналоговых сигналов.

Считывание

кодов из ОЗУ производится по команде

IN, адресная информация которой позволяет

сформировать сигнал

![]() =0

и битами А2А1А0 выбрать для чтения ячейку

памяти ОЗУ, а сопровождающий эту команду

сигнал чтения

=0

и битами А2А1А0 выбрать для чтения ячейку

памяти ОЗУ, а сопровождающий эту команду

сигнал чтения

![]() с помощью инвертора преобразуется в

импульс единичного строба ALE,

по которому выбранная ячейка ОЗУ

соединяется с буфером ШД АЦП.

с помощью инвертора преобразуется в

импульс единичного строба ALE,

по которому выбранная ячейка ОЗУ

соединяется с буфером ШД АЦП.

Вид преобразуемых аналоговых сигналов и коды выходных цифровых сигналов зависят от опорных напряжений UОП1 и UОП2 (табл.1.3), подводимых к АЦП1 через внешние выводы ИМС АЦП. Эти зависимости устанавливаются для всех восьми аналоговых сигналов одновременно.

Таблица 1.3

|

UОП1 |

UОП2 |

UВХ |

Соответствие выходных кодов входным напряжениям |

|

+2,5 V |

0 |

0…+2,5 V |

0000.0000 (0 V)…1111.1111 (+2,5 V) |

|

0 |

-2,5 V |

0…-2,5 V |

0000.0000 (-2,5 V)…1111.1111 (0 V) |

|

1,25 V |

-1,25 V |

-1,25…+1,25 V |

0000.0000 (-1,25 V)…1000.0000 (0,0049 V)…1111.1111 (+1,25 V) |

Из

множества ИМС ЦАП [6] рассмотрим ЦАП типа

КР1108ПА2. Вход ЦАП 8-разрядный (рис.1.6 и

рис.1.64). Управление ЦАП осуществляется

стандартными сигналами

![]() и

и

![]() .

Вид выходного аналогового напряжения

UВЫХ,

снимаемого с AN,

зависит от способа подключения вывода

FC1

на землю (табл.1.4).

.

Вид выходного аналогового напряжения

UВЫХ,

снимаемого с AN,

зависит от способа подключения вывода

FC1

на землю (табл.1.4).

Таблица 1.4

|

Вывод FC1 заземлен |

Соответствие выходного напряжения входным кодам |

|

- напрямую |

0000.0000 (0 V)…1111.1111 (+2,5 V) |

|

- через С=0,1 мкФ |

0000.0000 (-1,25 V)…1000.0000 (0,0049 V)…1111.1111 (+1,25 V) |

Питание ЦАП двухполярное: -15 В и +5 В. ИМС имеет два вывода земли: 0D V - земля цифровая и 0A V - земля аналоговая.

рисунок

Р ассмотрим

пример реализации на основе МП системы

автоматического регулирования по

структурной схеме, приведенной на

рис.1.65. Примем регулятор П-типа с

коэффициентом передачи К=2. МП должен

выполнять умножение на коэффициент КМП

цифрового кода сигнала

ассмотрим

пример реализации на основе МП системы

автоматического регулирования по

структурной схеме, приведенной на

рис.1.65. Примем регулятор П-типа с

коэффициентом передачи К=2. МП должен

выполнять умножение на коэффициент КМП

цифрового кода сигнала

![]() ,

равного разности кодов сигналов UЗАД

и UОУ.

Принципиальная схема САР приведена на

рис.1.64. АЦП работает в однополярном

режиме, а ЦАП работает в двухполярном

режиме. Сигналы UЗАД,

UРЕГ

и UОУ

аналоговые, а сигналы СЗАД,

СОУ,

Сε

и СРЕГ

цифровые (коды).

,

равного разности кодов сигналов UЗАД

и UОУ.

Принципиальная схема САР приведена на

рис.1.64. АЦП работает в однополярном

режиме, а ЦАП работает в двухполярном

режиме. Сигналы UЗАД,

UРЕГ

и UОУ

аналоговые, а сигналы СЗАД,

СОУ,

Сε

и СРЕГ

цифровые (коды).

Коэффициенты передачи для ИМС АЦП типа КР572ПВ4 и ЦАП типа КР1108ПА2, примененных в схеме на рис.1.64, равны

![]() (1.1)

(1.1)

Если К – коэффициент передачи П-регулятора для аналоговых сигналов (рис.1.65а), а КМП – коэффициент передачи, реализуемый программой МП (рис.1.65б), то из сопоставления рис.1.65а и 1.65б получаем

![]() (1.2)

(1.2)

Это выражение справедливо для любых типов ИМС АЦП и ЦАП. Для примененных в схеме ИМС АЦП и ЦАП с учетом (1.1) получим: КМП=К=2.

Умножение на 2 в МП может быть выполнено циклическим сдвигом кода влево с использованием команды RLC. Например, при сдвиге влево кода 0010.1110В=2ЕН=4610 получим код 0101.1100В=5СH=9210.

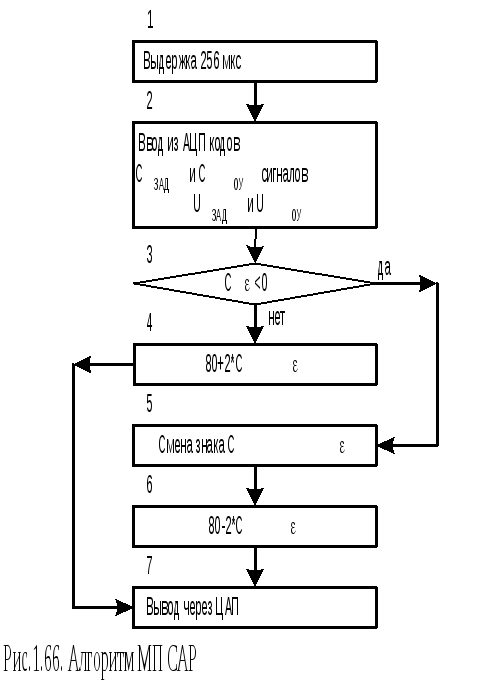

А лгоритм

МП системы автоматического регулирования

приведен на рис.1.66, а программа – на

рис.1.67.

лгоритм

МП системы автоматического регулирования

приведен на рис.1.66, а программа – на

рис.1.67.

Блок 1: Создание выдержки времени не менее 256 мкс, чтобы ОЗУ АЦП после включения питания схемы или сброса заполнилось верными данными.

Блок 2: Ввод через АЦП кодов сигналов UЗАД и UОУ.

Блок

3: Вычисление

![]() и переход по знаку результата.

и переход по знаку результата.

Блок 4: Подготовка кода для вывода положительного напряжения сигнала UРЕГ. При входном коде 80 ЦАП его выходной сигнал равен 0,0049 В≈0 В.

Блок

5: Смена знака кода

![]() ,

так как операция умножения

,

так как операция умножения

![]() на 2 через сдвиг RLC кода верна только для

положительных чисел.

на 2 через сдвиг RLC кода верна только для

положительных чисел.

Блок 6: Подготовка кода для вывода отрицательного напряжения сигнала UРЕГ.

Блок 7: Вывод сигнала UРЕГ через ЦАП.

|

Адрес |

Код команды |

Метка |

Мнемокод |

Комментарии |

|||

|

0000 |

3E |

2В |

|

|

М1 |

MVI 2В |

Выдержка времени в тактах 7+43·(5+10)=652, в микросекундах 652·0,4=260,8 мкс* |

|

0002 |

3D |

|

|

|

Цикл |

DCR A |

|

|

0003 |

C2 |

02 |

00 |

|

|

JNZ Цикл |

|

|

0006 |

DB |

E8 |

|

|

М2 |

IN E8 |

Ввод UОУ с адреса Е8Н=1110.1000В |

|

0008 |

57 |

|

|

|

|

MOV D, A |

Регистр D←аккумулятор А |

|

0009 |

DB |

EC |

|

|

|

IN EC |

Ввод UЗАД с адреса ЕСН=1110.1100В |

|

000B |

92 |

|

|

|

M3 |

SUB D |

Аккумулятор

А← |

|

000C |

FA |

17 |

00 |

|

|

JM M5 |

Переход

на М5, если

|

|

000F |

07 |

|

|

|

M4 |

RLC |

Аккумулятор

А←2· |

|

0010 |

57 |

|

|

|

|

MOV D, A |

Регистр D←аккумулятор А |

|

0011 |

3E |

80 |

|

|

|

MVI A, 80 |

Аккумулятор А←80 |

|

0013 |

8A |

|

|

|

|

ADC D |

Аккумулятор

А←80+2·| |

|

0014 |

C3 |

20 |

00 |

|

|

JMP M7 |

Безусловный переход на метку М7 |

|

0017 |

57 |

|

|

|

M5 |

MOV D, A |

Регистр D←аккумулятор А |

|

0018 |

3E |

00 |

|

|

|

MVI A, 00 |

Аккумулятор А←00 |

|

001A |

92 |

|

|

|

|

SUB D |

Аккумулятор

А←| |

|

001B |

07 |

|

|

|

M6 |

RLC |

Аккумулятор

А←2·| |

|

001C |

57 |

|

|

|

|

MOV D, A |

Регистр D←аккумулятор А |

|

001D |

3E |

80 |

|

|

|

MVI A, 80 |

Аккумулятор А←80 |

|

001F |

92 |

|

|

|

|

SUB D |

Аккумулятор

А←80-2· |

|

0020 |

D3 |

F7 |

|

|

М7 |

OUT F7 |

Вывод UРЕГ по адресу F7H=1111.0111B |

|

Рис.1.67. Программа МП САР |

|||||||

* В приведенном расчете:

- 7, 5 и 10 – длительности в тактах выполнения команд MVI, DCR и JNZ;

- 43 – десятичный эквивалент 16-ричного кода 2BН (количества циклов);

- 0,4 – длительность машинного такта МП, мкс.