- •Принцип проектирования микропроцессорного блока.

- •Программная модель микропроцессора Intel 8085.

- •Система команд микропроцессора

- •Особенности программирования на ассемблере.

- •Шина адреса.

- •Шина управления.

- •Особенности мп к1812вм85(intel 80185).

- •Организация микропроцессорного блока на базе микропроцессора к1810 вм86/88 (Intel 8086/88 ) Основные методы повышения производительности микропроцессоров:

- •Основные характеристики микропроцессоров:

- •Средства реализации пошагового режима.

- •Особенности организации вм88.

- •Процессорный блок на базе 8086 / 8088

- •Особенности проектирования блоков памяти в микропроцессорных устройствах.

- •Статическая память 537 ру n зу

- •Периферийные бис микропроцессорных комплектов. Обобщенная структура программируемой бис.

- •Программируемый параллельный адаптер кр580 вв55

- •Программируемый таймер кр580ви53 / ви54

- •Программируемый адаптер последовательного интерфейса кр580вв51.

- •Структурная организация программируемого адаптера последовательного интерфейса кр580вв51.

- •Программное обеспечение программируемого адаптера последовательного интерфейса кр580вв51.

- •Программируемый контроллер прерываний кр580вн59,вн59а; intel8259, 59а

- •Структура программы инициализации пкп

- •Особенности организации 1810вн59а (i8259а).

- •Микроконтроллер к1816 ве51/31(intel 8051)

- •Структура резидентной памяти данных (рпд).

- •Система команд.

- •Структура команд orl( дизъюнкция), xrl (сумма по модулю 2) аналогична предыдущей.

- •Параллельные порты.

- •Счетчик/Таймер

- •Последовательный порт

- •Подсистема прерываний

- •Особые режимы работы

Средства реализации пошагового режима.

Цикл выполнения команды микропроцессора состоит из четырех тактов. В первом такте выводится адрес, во втором готовится передача данных, которая реализуется в третьем и четвертом тактах. Анализ сигналов состояний READY выполняется в третьем такте.

Внешние сигналы микропроцессора можно разделить на три группы:

Общие сигналы;

Сигналы управления минимальным режимом;

Сигналы управления максимальным режимом.

Режим задается

путем подачи уровня напряжения на вход

MN/![]() .

.

При минимальном режиме все сигналы управления реализуются микропроцессором. Этот режим используется в однопроцессорных системах .При максимальном режиме необходимо использовать дополнительную БИС. Это режим используется в многопроцессорных системах.

Общие сигналы:

![]() .

.![]()

Микропроцессор работает от сигналов однофазных, допускается частота от 1 Мгц до 5 Мгц .

Сигнал сброса при первом включении микропроцессора должен быть не менее 50 мкс, во время действия сигнала сброса шина адреса и шина данных находятся в третьем состоянии. По сбросу обнуляется регистр IP, сегментному регистру (CS):= FFFF. Стартовый адрес программы FFFF0. Остальные сегментные регистры обнуляются.

Сигнал

![]() используется при отладке системы и

выполнении синхронизации с внешними

устройствами и микропроцессором. Этот

вход опрашивается по команде WAIT и если

он равен 1, то микропроцессор переходит

в состояние ожидания. Програмная

реализация сигнала READY.

используется при отладке системы и

выполнении синхронизации с внешними

устройствами и микропроцессором. Этот

вход опрашивается по команде WAIT и если

он равен 1, то микропроцессор переходит

в состояние ожидания. Програмная

реализация сигнала READY.

Прерывание : INT, INTA, NMI ( запрос немаскируемого прерывания ).

Сигналы ПДП: HOLD, HLDA.

BHE - связь с организацией памяти.

Память 86 процессора представляет собой 2 бвнка, ВНЕ - признак обращения к старшему байту банка памяти. ДТ / DR - управление внешнего формирователя ШД.

Особенности организации вм88.

Микропроцессор 88 был разработан для обеспечения приема аппаратных средств микропроцессора 80-85 . Имеет ту же цоколевку и характеристики, как 86 микропроцессор. Отличие состоит в организации внешних шины адреса и шины данных. Шина данных восьмиразрядная . Разряды А8-А15 формируются в регистре внутри микропроцессора. Для формирования шины адреса необходимо данные о младшем байте записать во внешний регистр. Управление памятью и внешними устройствами инверсно по отношению к 86. При выполнении внутренних операций быстродействие, как у 86 , так как внешняя шина данных шестнадцатиразрядная. При обращении к внешнему устройству потери времени составляют 4 такта на одно обращение. Использование ВМ88 снижает аппаратные затраты, так как упрощается организация памяти.

Процессорный блок на базе 8086 / 8088

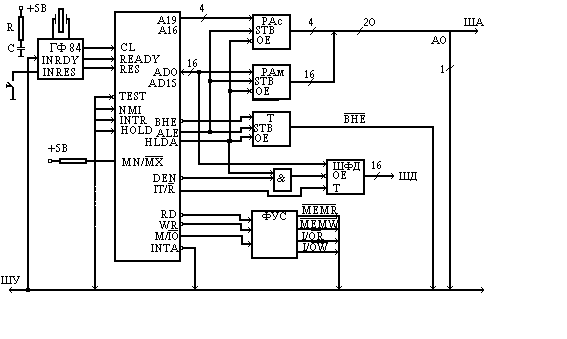

Рис. 2.5. Процессорный блок на МП К1810ВМ86:

РАс, РАм - регистр старшего и младшего байта адреса;

Т - триггер хранения ВНЕ;

ШФД - шинный формирователь данных;

ФУС - формирователь управляющих сигналов;

ГФ84 - системный генератор.

Проектирование микропроцессорного блока аналогично 8085. Для формирования ША требуется внешний регистр адреса, управляемый сигналом ALE. В течении первого такта адресной информации МП передает инфомацию о состоянии и сигнал BHE. Последний сигнал необходимо запомнить в течении первого такта во внешним регистре или триггере. Формирование ШД осуществляется буферными двунаправленными схемами с тремя состояниями. Управление буфером выполняется сигналами DT/R, DEN, которое формируются несколько раньше, чем сигналы записи / чтения. При обращении к внешним устройствам, как к ячейкам памяти формируется сигнал записи / чтения - WR/RD состоит в усилении мощности этих выходов. При использовании команд ввода-вывода необходимо ФУС, структура которого аналогична 8085. Управление синхронизацией МП выполняет генератор 1810 ГФ84 (8384).

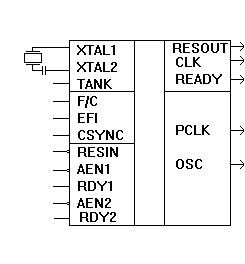

Генератор предназначен для организации взаимодействия микропроцессора с периферийными устройствами или другими микропроцессорами. Возможна работа в двух режимах - режиме внутренней и внешней синхронизации. При использовании внутренней синхронизации генераторный кварц подключается ко входам XTAL1, XTAL2. Выходные сигналы генератора: OSC, CLK, PCLK связаны следующими соотношениями:

f( clk )=OSC/2 f( pclk ) = OSC/6.

Режим форматирования внутренней частоты задается по входу F/C, если потенциал равен 0, то внутренний генератор, в противоположном случае частота должна подаваться по входу EFI. Обеспечение взаимодействия при работе в многопроцессорной системе осуществляется с помощью сигналов синхронизации: RDY1, RDY2, CSYNC. На вход CSYNC подаются сигналы синхронизации, RDY1, RDY2 - входная готовность объединенная по имени. Управление выполняется сигналами приходящими на AEN. RESIN - входной сигнал сброса .