- •Принцип проектирования микропроцессорного блока.

- •Программная модель микропроцессора Intel 8085.

- •Система команд микропроцессора

- •Особенности программирования на ассемблере.

- •Шина адреса.

- •Шина управления.

- •Особенности мп к1812вм85(intel 80185).

- •Организация микропроцессорного блока на базе микропроцессора к1810 вм86/88 (Intel 8086/88 ) Основные методы повышения производительности микропроцессоров:

- •Основные характеристики микропроцессоров:

- •Средства реализации пошагового режима.

- •Особенности организации вм88.

- •Процессорный блок на базе 8086 / 8088

- •Особенности проектирования блоков памяти в микропроцессорных устройствах.

- •Статическая память 537 ру n зу

- •Периферийные бис микропроцессорных комплектов. Обобщенная структура программируемой бис.

- •Программируемый параллельный адаптер кр580 вв55

- •Программируемый таймер кр580ви53 / ви54

- •Программируемый адаптер последовательного интерфейса кр580вв51.

- •Структурная организация программируемого адаптера последовательного интерфейса кр580вв51.

- •Программное обеспечение программируемого адаптера последовательного интерфейса кр580вв51.

- •Программируемый контроллер прерываний кр580вн59,вн59а; intel8259, 59а

- •Структура программы инициализации пкп

- •Особенности организации 1810вн59а (i8259а).

- •Микроконтроллер к1816 ве51/31(intel 8051)

- •Структура резидентной памяти данных (рпд).

- •Система команд.

- •Структура команд orl( дизъюнкция), xrl (сумма по модулю 2) аналогична предыдущей.

- •Параллельные порты.

- •Счетчик/Таймер

- •Последовательный порт

- •Подсистема прерываний

- •Особые режимы работы

Параллельные порты.

Порты Р0-Р3 предназначены для ввода или вывода байтовой информации и обеспечивают обмен с внешними устройствами: памятью программ и данных, контроллерами различного назначения, периферийными устройствами.

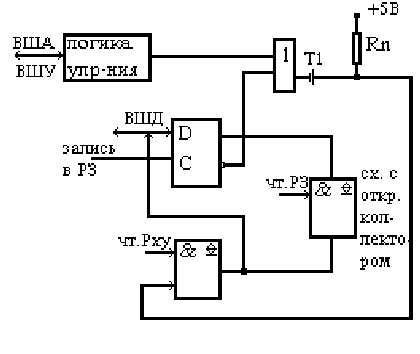

Каждый из портов состоит из 8-разрядного регистра -защелки (РЗ) , выходного драйвера транзистора Т1, входных цепей и схемы Д1 с открытым коллектором. Схемотехника портов несколько отличается, так как они выполняют разные функции. Однако в упрощенном варианте её можно рассмотреть на примере рис.

При чтении со входа порта Рх.Y данные через конъюнктор Д1 передаются на внутреннюю шину данных (ВШД), которая организована как "монтажное ИЛИ". Если в РЗ записана 1 , то данные со входа порта без искажения передаются в приемник. Если РЗ=0, то в соответствующий разряд приемника будет записан 0 в независимости от значения сигнала.

При записи информации в порт, данные записываются в РЗ и выводятся через Т1 на выход порта.

Обращение к портам возможно только по прямому адресу. Все разряды порта находятся в битовом пространстве.Порты однонаправленные. Каждый бит порта может быть настроен как на ввод, так и на вывод. По сбросу все порты устанавливаются на ввод.

Для чтения данных из порта или регистра защелки используются различные команды.

Чтение РЗ осуществляется командами «чтение-модификация-запись» , при выполнении которых команда считывает состояние РЗ, при необходимости модифицирует полученное значение и записывает результат обратно в РЗ:

ORL Px,A - Px - приемник

XRL Px, A

ANL Px,A

INC Px

DEC Px

DJNZ Px,rel

Для чтения отдельных битов используются команды :

JBC Px.y, SETB Px.y

CPL Px.y, MOV Px.y,C

Во всех случаях, когда операндом и регистром назначения является порт или бит порта, команды считывают информацию с выходов РЗ, а не с внешних контактов выводов порта.

Чтение с внешних выводов порта может быть выполнено командами:

MOV (A, @Ri, Rn, ad) , Px

ADD A, Px

Чтение информации с выходов РЗ, а не с внешних контактов позволяет исключить в ряде случаев неправильную интерпретацию уровня напряжения на выводе порта. Например, при соединении вывода порта с базой n-p-n транзистора и подаче лог. 1, транзистор открывается и чтение состояния внешнего вывода покажет лог.0, так как на контакте порта присутствует напряжение база-эммитер транзистора (0,7В). Чтение же РЗ подтвердит подачу лог. 1.

Запись данных в порт осуществляется обычным способом: MOV Px,(A,Rn,@R0,#d).

Порты Р0, Р1, Р2, Р3 в зависимости от особенности применения могут реализовать разные функции. При работе с внешней памятью порт Р0 является системным портом , через который в режиме с разделением времени передаются младший байт адреса и данные. Появление младшего байта адреса сопровождается сигналом ALE , по которому он должен быть зафиксирован во внешнем регистре.

Признаком работы Р0 в системном режиме является использование команд MOVX, MOVC.

При работе в качестве системного порта согласование (специальное) с нагрузкой не требуется. Если Р0 используется как порт общего назначения, то к выходу порта должен быть присоединен внешний подтягивающий резистор от источника питания +5В. Р1-Р3 имеют встроенную нагрузку.

Порт Р2 служит для вывода старшего байта адреса при работе в системном режиме. Особенностью порта Р2 является возможность мультиплексирования на выход содержимого РЗ или старшего байта адреса. При работе в режиме адресной шины содержимое РЗ сохраняется и поступает на выводы порта в тех машинных циклах, когда нет обращения к внешней памяти. При обращении к внешней памяти на выход порта выводится информация из регистра адреса DPTR или из программного счетчика РС по командам MOVC и MOVX .Исключение составляют команды MOVX A,@Ri, и MOVX @Ri,A, при которых на выходе находится содержимое РЗ.

Нагрузочная способность Р0 - два входа ТТЛ, у остальных - один.

Р1 - порт общего назначения и особенностей не имеет.

Р3 - при записи в Р3 “1” выполняет системные функции

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

RD |

WR |

T1 |

T0 |

INT1 |

INT0 |

TxD |

RxD |

Рис.3.5. Альтернетивные функции порта 3: RD - чтение внешней памяти данных; WR- запись во внешнюю память данных; Т1,Т0 - входы таймера/счетчика; INT0, INT1 - входы запросов прерываний; TxD- выход передатчика последовательного порта; RxD - вход приемника последовательного порта.

. Если в бит порта Р3 записан “0” , то на выходе порта фиксируется “0”.

Наиболее оптимально применение ВЕ51 в том случае, если отсутствуют устройства, для которых требуются внешние шины данных и адреса, так как в этом случае можно использовать произвольно порты Р0-Р2. При использовании порта Р3 необходимо учитывать функциональные особенности каждого входа: T1, T0, INT1, INT0 – входные линии, RD,WR,- выходные линии, сигналы на которых формируются только при выполнении команд MOVX, и так далее.