- •Принцип проектирования микропроцессорного блока.

- •Программная модель микропроцессора Intel 8085.

- •Система команд микропроцессора

- •Особенности программирования на ассемблере.

- •Шина адреса.

- •Шина управления.

- •Особенности мп к1812вм85(intel 80185).

- •Организация микропроцессорного блока на базе микропроцессора к1810 вм86/88 (Intel 8086/88 ) Основные методы повышения производительности микропроцессоров:

- •Основные характеристики микропроцессоров:

- •Средства реализации пошагового режима.

- •Особенности организации вм88.

- •Процессорный блок на базе 8086 / 8088

- •Особенности проектирования блоков памяти в микропроцессорных устройствах.

- •Статическая память 537 ру n зу

- •Периферийные бис микропроцессорных комплектов. Обобщенная структура программируемой бис.

- •Программируемый параллельный адаптер кр580 вв55

- •Программируемый таймер кр580ви53 / ви54

- •Программируемый адаптер последовательного интерфейса кр580вв51.

- •Структурная организация программируемого адаптера последовательного интерфейса кр580вв51.

- •Программное обеспечение программируемого адаптера последовательного интерфейса кр580вв51.

- •Программируемый контроллер прерываний кр580вн59,вн59а; intel8259, 59а

- •Структура программы инициализации пкп

- •Особенности организации 1810вн59а (i8259а).

- •Микроконтроллер к1816 ве51/31(intel 8051)

- •Структура резидентной памяти данных (рпд).

- •Система команд.

- •Структура команд orl( дизъюнкция), xrl (сумма по модулю 2) аналогична предыдущей.

- •Параллельные порты.

- •Счетчик/Таймер

- •Последовательный порт

- •Подсистема прерываний

- •Особые режимы работы

Шина адреса.

При формировании

ША необходимо анализировать наличие

режима ПДП. Если ПДП не используется,

то в качестве формирователя можно

использовать однонаправленные буферные

элементы или обычные интегральные

схемы. При наличии большого числа

периферийных устройств наиболее

нагруженными разрядами являются разряды,

обеспечивающие обращение к внутренним

регистрам периферийных БИС. Как правило

это разряды А0 и А1. Поэтому особенно

тщательно нужно анализировать нагрузку

на эти разряды. Так как адрес внешнего

устройства дублируется в старшем и

младшем байтах, то можно не использовать

формирователь А0, А1, а распределить

нагрузку между разрядами (А0 А1)![]() (A8

A9). Это справедливо для К580. В тех случаях,

когда необходимо фиксировать адрес во

внешнем регистре, рекомендуется

использовать микросхемы: К580ИР82(83),

1533ИР23,33,34,...

(A8

A9). Это справедливо для К580. В тех случаях,

когда необходимо фиксировать адрес во

внешнем регистре, рекомендуется

использовать микросхемы: К580ИР82(83),

1533ИР23,33,34,...

ША, как правило, полностью не используется. Ее надо проектировать под конкретный объем памяти и внешних устройств.

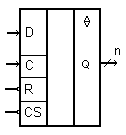

Обобщенная схема регистра.

CS - сигнал выборки корпуса;

D - входные сигналы;

Q - выходные сигналы.

Шина управления.

В ШУ входят сигналы

записи, чтения, записи внешних устройств,

сигналы прерывания, ПДП и синхронизации.

При работе с памятью и внешними

устройствами возможны два способа

обращения к внешним устройствам: с

помощью команд IN и OUT(раздельное обращение

к памяти и внешним устройствам), с помощью

команд чтение и запись памяти. В первом

случае операционные возможности

обработки входных данных уменьшаются,

так как весь обмен информацией выполняется

через аккумулятор и несколько упрощается

дешифрация адреса, но требуется четыре

сигнала управления:

![]() ,

,![]() ,

,![]() ,

,![]() .

А во втором случае приемником или

передатчиком информации может быть

любой регистр МП и достаточно двух

сигналов

.

А во втором случае приемником или

передатчиком информации может быть

любой регистр МП и достаточно двух

сигналов![]() и

и![]() .

Формирование этих сигналов зависит от

особенностей МП. Для К580 сигналы

записи/чтения формируются в системном

контроллере К580ВК28, на вход которого

поступает информация с байта состояния

и сигналы чтение/запись МП. В МП 1821

требуется внешняя схема формирования

сигнала с помощью дешифратора (это

наиболее простой способ).

.

Формирование этих сигналов зависит от

особенностей МП. Для К580 сигналы

записи/чтения формируются в системном

контроллере К580ВК28, на вход которого

поступает информация с байта состояния

и сигналы чтение/запись МП. В МП 1821

требуется внешняя схема формирования

сигнала с помощью дешифратора (это

наиболее простой способ).

Если обращение идет как к ячейке памяти, то достаточно сделать следующее:

Приведенные схемы используются в тех случаях, когда нет режима ПДП. При наличии ПДП они должны быть с тремя состояниями или открытым коллектором. В качестве сигналов синхронизации обычно используются входы кварцевого генератора с частотой МП, усиленной по мощности, либо сигналы синхронизации, формируемые в МП.

Для К580 - сигнал F2T.

Для задания требуемой частоты МП, кварц на входы генератора ГФ24 должен иметь собственную частоту в 9 раз больше, чем требуемая (9:1).

Для 1821 соотношение 2:1. В качестве сигнала синхронизации используют выход SINC.

Особенности мп к1812вм85(intel 80185).

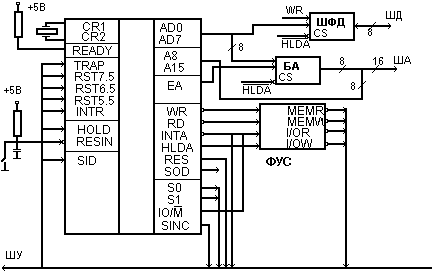

Рис.1.1. Структура процессорного блока на основе К1821 ВМ85:

TRAP - вход запроса не маскируемого прерывания;

RST7.5-RST5.5 - входы запроса прерывания повторного запуска;

INTR - вход запроса прерывания общего назначения;

RESIN - вход сигнала сброса;

SID - вход данных в последовательном коде;

SOD - выход данных в последовательном коде;

AD7-AD0 - мультиплексная шина адреса/данных;

А15-А8 - старшие разряды ША;

ЕА - стробирующий сигнал фиксации адреса;

S0, S1, IO/![]()

![]() -

сигналы состояния машинного цикла,(IO/

-

сигналы состояния машинного цикла,(IO/![]() )

является идентификатором обращения к

памяти (IO/

)

является идентификатором обращения к

памяти (IO/![]() = 0) или УВВ (IO/

= 0) или УВВ (IO/![]() = 1);

= 1);

SYNC - выход импульсов системной синхронизации, период сигнала SYNC и вдвое большее периода входных сигналов на входах CR1, CR2; CR1, CR2 - входы синхроимпульсов, могут присоединяться к кварцевому резонатору, LC или RC - цепочке, к внешнему генератору синхроимпульсов;

ШФД - шинный формирователь данных; БА - буферный регистр адреса;

ФУС - схема формирования управляющих сигналов.

Выполнен на

КМОП-технологии. Младший байт ША

передается в режиме с разделением

времени по ШД. Передача адреса

сопровождается сигналом ALE(EA). В МП

содержится встроенный генератор, поэтому

необходим только кварцевый резонатор,

подключенный ко входам CR1, CR2. Частота

кварца должна быть в 2 раза больше

необходимой частоты. Частота МП выводится

через выход SYNC. МП имеет встроенную

подсистему прерываний , которая

обрабатывает сигналы немаскируемого

прерывания NMI(TRAP), 3 векторных прерываний

RST 7.5, RST 6.5, RST 5.5 и вход INTR внешних прерываний

для обслуживания внешних контроллеров

прерываний. В составе МП есть входы и

выходы для реализации последовательных

каналов SID, SOD. Эти входы могут использоваться

для ввода/вывода битовых сигналов или

для реализации последовательного

обмена, который требует программных

затрат. Байт состояния, аналогично К580,

не формируется. Для контроля машинных

циклов используются выходы S0, S1, IO/![]() .

Формирование внешних сигналов для

работы с памятью и внешними устройствами

выполняются на основе сигналов

.

Формирование внешних сигналов для

работы с памятью и внешними устройствами

выполняются на основе сигналов![]() ,

,![]() ,

IO/

,

IO/![]() .

В отличии от К580, тактовая частота в 1,5

раза больше, а для питания используется

один источник в +5В. Циклы выполнения

команд аналогичны К580

.

В отличии от К580, тактовая частота в 1,5

раза больше, а для питания используется

один источник в +5В. Циклы выполнения

команд аналогичны К580![]() 1

такт.

1

такт.

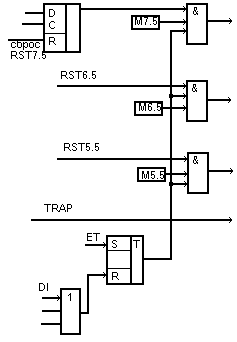

Методология построения подсистемы прерывания аналогично ВМ80, однако число уровней прерывания увеличено с 1 до 5.

ТАБЛИЦА

|

ИМЯ ПРЕРЫВАНИЯ |

ПРИОРИТЕТ |

СТАРТОВЫЙ АДРЕС |

ВИД ЗАПРЕТА |

|

TRAP (NMI) |

1 |

24h |

|

|

RST 7.5 |

2 |

3Ch |

|

|

RST 6.5 |

3 |

34h |

уровень |

|

RST 5.5 |

4 |

2Ch |

уровень |

|

INTR |

5 |

ввод от внешнего устройства |

уровень |

Особенностью немаскируемых прерываний является то, что запрос прерываний вызывается фронтом сигнала с последующим удержанием "1" на время более 400нсек. Это позволяет защитить вход запроса от действий возможных помех. Наиболее удобным является RST7.5. Для работы с этим уровнем в схеме предусмотрен триггер запроса ТЗ. Если прерывание не разрешено, то запрос RST7.5 будет запомнен, остальные запросы пропадают. Внутренний триггер запроса может быть сброшен командой SIM, по которой вектору прерываний P:=A.

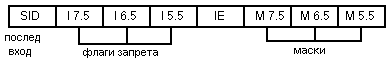

Формат команды:

![]()

А(7) - данные последовательного вывода;

Х - разряд не используется;

IE - разрешение установки масок;

MRST7.5-MRST5.5 - маски прерываний.

Особенностью формата является возможность раздельного управления подсистемы обработки прерываний и последовательного вывода. Это управление выполняется разрядами 6 и 3.

Команда RIM - чтение регистра прерываний, выполняет обратные действия

(А):=(IP)

Формат команды:

Рис.1.3. Формат регистра масок прерываний при чтении командой RIM

Управляются уровнем сигнала.

Достоинства способа: большая помехоустойчивость.

Недостаток способа: необходимость управлять длительностью сигнала запроса.

Запрос должен быть снят в процедуре подпрограммы обработки.