- •Микропроцессорные устройства

- •4.2.1.3 Специальный режим использования порта р0:

- •10 Примеры схем включения омэвм………………………………………...……..……………..73

- •Введение

- •1 Общая характеристика омэвм к1816ве751

- •2 Условное графическое обозначение омэвм к1816ве751 и назначение ее отдельных выводов

- •3 Структура омэвм к1816ве751 и ее описание

- •3.1 Блок управления и синхронизации микроЭвм

- •3.2 Блок арифметико-логического устройства (алу)

- •3.3 Резидентная память данных

- •3.4 Резидентная память программ

- •3.5 Блок прерываний

- •3.6 Блок таймеров – счетчиков

- •3.7 Блок последовательного порта (интерфейса)

- •3.8 Параллельные порты ввода-вывода

- •3.9 Схема десятичной коррекции аккумулятора (сдка)

- •3.10 Внутренний тактовый генератор (osc)

- •3.11 Резидентная шина данных

- •3.12 Регистры

- •4 Особенности функционирования и применение омэвм в различных режимах

- •4.1 Использование таймеров-счётчиков

- •4.2 Использование параллельных портов ввода-вывода

- •4.2.1 Особенности работы порта р0

- •4.2.1.1 Особенности работы р0 с вп (впп или впд)

- •4.2.1.2 Особенности работы р0 в качестве портов ввода/вывода

- •4.2.1.2.1 Вывод данных через р0

- •4.2.1.2.2 Ввод данных через р0

- •4.2.1.3 Специальный режим использования порта р0:

- •4.2.2 Особенности работы порта р1

- •4.2.3 Особенности работы порта р2

- •4.2.4.1.2 Выполнение портом р3 альтернативных функций входа

- •4.2.4.2 Работа р3 в качестве порта вывода

- •4.2.4.3 Работа р3 в качестве порта ввода

- •4.3 Применение последовательного порта

- •4.3.1 Работа последовательного порта в режиме 0

- •4.3.1.1 Передача в режиме 0

- •4.3.1.2 Приём в режиме 0

- •4.3.2 Работа последовательного порта в режиме 1

- •4.3.2.1 Передача в режиме 1

- •4.3.2.2 Приём в режиме 1

- •4.3.3 Работа последовательного порта в режимах 2 и 3

- •4.3.4 Скорость передачи-приёма данных через последовательный порт

- •4.3.5 Пример программирования последовательного порта омэвм

- •4.3.6 Особенности межконтроллерного обмена информацией в локальных управляющих сетях

- •4.4 Особенности структуры прерываний

- •4.5 Организация пошагового режима работы

- •4.6 Организация памяти

- •4.6.1 Особый режим работы памяти омэвм

- •4.7 Расширение резидентной (внутренней) системы ввода-вывода (рсвв/выв)

- •5 Система команд

- •5.1 Способы адресации операндов

- •5.2 Команды передачи данных

- •5.3 Арифметические команды

- •5.4 Логические команды

- •5.5 Операции с битами

- •5.6 Команды передачи управления

- •6 Программирование и проверка омэвм км1816ве751

- •7 Программирование бита защиты памяти

- •8 Режим холостого хода и пониженного энергопотребления

- •8.1 Режим холостого хода

- •8.2 Режим микропотребления

- •8.3 Режим пониженного потребления для омэвм серии 1816 (n-моп)

- •9 Начальная инициализация омэвм

- •10 Примеры схем включения омэвм

- •Список литературы

4.2 Использование параллельных портов ввода-вывода

Как отмечено в 3.8 порты Р0…Р3 могут использоваться:

Как 8-разрядные параллельные порты ввода/вывода информации;

Как 32 одноразрядные линии ввода/вывода;

При работе с внешней памятью программ и данных;

В режиме альтернативных функций (8 линий порта Р3);

При программировании и проверке РПП.

По сигналу ”RESET” в регистры-защёлки всех портов автоматически записываются единицы, настраивающие все 32 линии портов на ввод информации, а восемь линий порта Р3, кроме этого, - на режим “альтернативных” функций.

4.2.1 Особенности работы порта р0

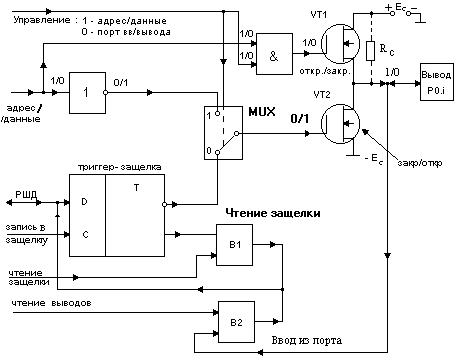

На рисунке 11 приведена упрощённая структурная схема i-го разряда порта Р0, отражающая его работу в двух основных режимах:

Работа с внешней памятью программ или данных;

Р

абота

в качестве порта ввода/вывода.

абота

в качестве порта ввода/вывода.

Рисунок 11 – Упрощенная структурная схема порта Р0 (i-го вывода)

В зависимости от выполняемых в настоящее время команд (работа с портами или с ВП) внутренний сигнал «управление» принимает значение: 0 - Р0 используется как порт ввода/вывода; 1 - порт используется для работы с ВП.

4.2.1.1 Особенности работы р0 с вп (впп или впд)

Сигнал «управление» равен 1. Мультиплексор МХ находится в верхнем положении. На вход инвертора и один из входов конъюнктора поступает значение i-го разряда младшего байта адреса ВП - 1/0. После инвертора оно принимает значение 0/1. Т.к. на другом входе конъюнктора присутствует логическая 1, то выходной сигнал конъюнктора повторяет значение i-го разряда адреса - 1/0. Таким образом, на затворах транзисторов VT1 и VT2 присутствуют две противоположные комбинации логических сигналов:

1 /0

на затворе VT1

/0

на затворе VT1

при значении i-го бита адреса 1/0.

0/1 на затворе VT2

В схеме использованы МОП-полевые транзисторы с каналом типа n. Если на затворе такого VT логическая 1, то транзистор – открыт, а если логический 0, то – закрыт. Следовательно, если в i-м бите адреса выдается логическая 1, то VT1 – открыт, а VT2 – закрыт, и с i-го вывода порта 0 снимается также 1. Если же в i-м бите адреса присутствует логический 0, то VT1 – закрыт, а VT2 – открыт.

С выхода при этом снимается логический 0. Сказанное можно представить следующей таблицей 18.

Таблица 18

|

Значение i-го бита МБ адреса ВП (выводимых данных) |

Сигналы на затворах транзисторов |

Состояние транзисторов |

Значение выходного сигнала | ||

|

VT1 |

VT2 |

VT1 |

VT2 | ||

|

0 |

0 |

1 |

закрыт |

открыт |

0 |

|

1 |

1 |

0 |

открыт |

закрыт |

1 |

Выводы порта Р0 при работе с ВП используются в режиме мультиплексирования: сначала выдаётся МБ адреса ВП, а затем через выводы выдаются или принимаются данные. Выдаются при работе с ВПД, а принимаются при работе с ВПП или ВПД. Следует обратить внимание на то, что при чтении ВПП или ВПД на нижний транзистор VT2 аппаратно автоматически подаётся логический 0, VT закрывается и не шунтирует i-й вывод Р0, через который происходит чтение памяти. Отметим также, что при выполнении команд работы с внешней памятью в триггеры-защёлки порта Р0 автоматически записываются логические 1.