- •Микропроцессорные устройства

- •4.2.1.3 Специальный режим использования порта р0:

- •10 Примеры схем включения омэвм………………………………………...……..……………..73

- •Введение

- •1 Общая характеристика омэвм к1816ве751

- •2 Условное графическое обозначение омэвм к1816ве751 и назначение ее отдельных выводов

- •3 Структура омэвм к1816ве751 и ее описание

- •3.1 Блок управления и синхронизации микроЭвм

- •3.2 Блок арифметико-логического устройства (алу)

- •3.3 Резидентная память данных

- •3.4 Резидентная память программ

- •3.5 Блок прерываний

- •3.6 Блок таймеров – счетчиков

- •3.7 Блок последовательного порта (интерфейса)

- •3.8 Параллельные порты ввода-вывода

- •3.9 Схема десятичной коррекции аккумулятора (сдка)

- •3.10 Внутренний тактовый генератор (osc)

- •3.11 Резидентная шина данных

- •3.12 Регистры

- •4 Особенности функционирования и применение омэвм в различных режимах

- •4.1 Использование таймеров-счётчиков

- •4.2 Использование параллельных портов ввода-вывода

- •4.2.1 Особенности работы порта р0

- •4.2.1.1 Особенности работы р0 с вп (впп или впд)

- •4.2.1.2 Особенности работы р0 в качестве портов ввода/вывода

- •4.2.1.2.1 Вывод данных через р0

- •4.2.1.2.2 Ввод данных через р0

- •4.2.1.3 Специальный режим использования порта р0:

- •4.2.2 Особенности работы порта р1

- •4.2.3 Особенности работы порта р2

- •4.2.4.1.2 Выполнение портом р3 альтернативных функций входа

- •4.2.4.2 Работа р3 в качестве порта вывода

- •4.2.4.3 Работа р3 в качестве порта ввода

- •4.3 Применение последовательного порта

- •4.3.1 Работа последовательного порта в режиме 0

- •4.3.1.1 Передача в режиме 0

- •4.3.1.2 Приём в режиме 0

- •4.3.2 Работа последовательного порта в режиме 1

- •4.3.2.1 Передача в режиме 1

- •4.3.2.2 Приём в режиме 1

- •4.3.3 Работа последовательного порта в режимах 2 и 3

- •4.3.4 Скорость передачи-приёма данных через последовательный порт

- •4.3.5 Пример программирования последовательного порта омэвм

- •4.3.6 Особенности межконтроллерного обмена информацией в локальных управляющих сетях

- •4.4 Особенности структуры прерываний

- •4.5 Организация пошагового режима работы

- •4.6 Организация памяти

- •4.6.1 Особый режим работы памяти омэвм

- •4.7 Расширение резидентной (внутренней) системы ввода-вывода (рсвв/выв)

- •5 Система команд

- •5.1 Способы адресации операндов

- •5.2 Команды передачи данных

- •5.3 Арифметические команды

- •5.4 Логические команды

- •5.5 Операции с битами

- •5.6 Команды передачи управления

- •6 Программирование и проверка омэвм км1816ве751

- •7 Программирование бита защиты памяти

- •8 Режим холостого хода и пониженного энергопотребления

- •8.1 Режим холостого хода

- •8.2 Режим микропотребления

- •8.3 Режим пониженного потребления для омэвм серии 1816 (n-моп)

- •9 Начальная инициализация омэвм

- •10 Примеры схем включения омэвм

- •Список литературы

4 Особенности функционирования и применение омэвм в различных режимах

4.1 Использование таймеров-счётчиков

ОМЭВМ

содержит 2 программируемых 16-разрядных

таймера-счётчика внешних событий Т/С,

которые обозначаются: Т/С0 и Т/С1.

Таймеры-счётчики могут программироваться

на режим таймера или счётчика внешних

событий. В режиме таймера содержимое

Т/С инкрементируется в каждом машинном

цикле, т.е. с интервалом

![]() ,

где

,

где![]() - период частоты внешнего кварцевого

резонатора. В режиме счётчика внешних

событий Т/С инкрементируются под

воздействием перехода из логической 1

в логический 0 внешнего сигнала на входах

Т0, Т1 (линии Р3.4, Р3.5). Для распознавания

перепада из 1 в 0 требуется не менее двух

машинных циклов. В фазе S5 P2 первого МЦ

на входе Ti (i = 0,1) фиксируется значение

логической 1. В фазе S5 P2 следующего МЦ

распознаётся нулевое значение сигнала

на входе Ti (т.е. обнаруживается перепад

из 1 в 0). В очередном МЦ осуществляется

инкремент содержимого Т/С.

- период частоты внешнего кварцевого

резонатора. В режиме счётчика внешних

событий Т/С инкрементируются под

воздействием перехода из логической 1

в логический 0 внешнего сигнала на входах

Т0, Т1 (линии Р3.4, Р3.5). Для распознавания

перепада из 1 в 0 требуется не менее двух

машинных циклов. В фазе S5 P2 первого МЦ

на входе Ti (i = 0,1) фиксируется значение

логической 1. В фазе S5 P2 следующего МЦ

распознаётся нулевое значение сигнала

на входе Ti (т.е. обнаруживается перепад

из 1 в 0). В очередном МЦ осуществляется

инкремент содержимого Т/С.

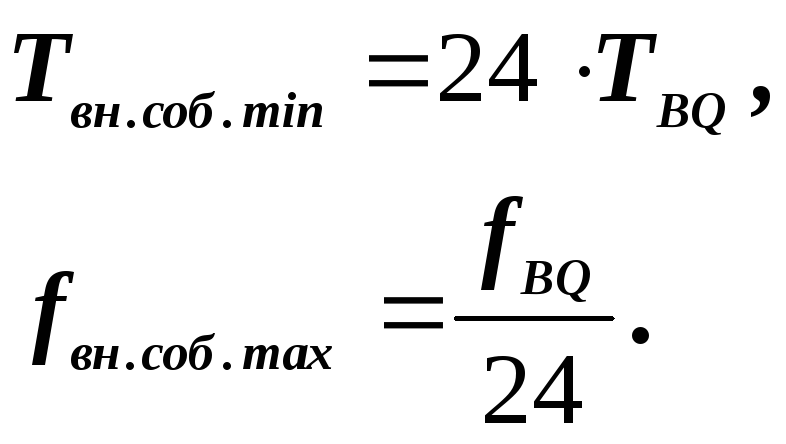

Следовательно, минимальный период и максимальная частота следования импульсов на входе Ti, идентифицирующих наступление внешних событий, определяются из выражений

(1)

(1)

Для того, чтобы при определении перепада из 1 в 0 логические 1 и 0 на входе Ti были зафиксированы, длительности импульсов и пауз должны удовлетворять соотношениям

![]()

![]() (2)

(2)

Логически каждый Т/С разбит на 2 части по 8 бит, обозначаемые TH0, TL0 для T/C0 и TH1, TL1 для T/C1. Последние можно использовать как 8-разрядные регистры общего назначения, если предварительно остановить Т/С, сбросив биты TR0 = TR1 = 0 в регистре РУСТ (TCON).

Начальные

значения

![]() в регистры THi, TLi (i = 0,1) при программировании

Т/С записываются произвольно.

в регистры THi, TLi (i = 0,1) при программировании

Т/С записываются произвольно.

Управлять счётом (разрешать / запрещать) можно программно и аппаратно.

Регистры THi и TLi программно доступны по записи и чтению.

При переполнении Т/С в процессе счёта устанавливаются флаги TFi (i = 0,1) в регистре РУСТ (TCON), которые могут вызывать прерывание основной программы или опрашиваться программно.

Для программирования и управления работой Т/С предназначены два регистра: TMOD и TCON. Обозначение и назначение их отдельных разрядов приведены в таблицах 10…13.

Таймеры / счётчики могут работать в одном из 4-х режимов работы: 0, 1, 2 и 3.

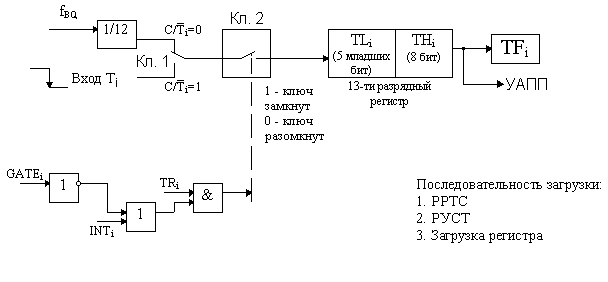

4.1.1 Режим 0. Установка битов М0 = 0, М1 = 0 в регистре TMOD настраивает оба таймера на работу в режиме 0. Упрощённая структура Т/С в этом режиме приведена на рисунке 8.

Р исунок

8 – Упрощенная структурная схема

таймера/счетчика в режиме 0

исунок

8 – Упрощенная структурная схема

таймера/счетчика в режиме 0

Каждый

Т/С работает

как 13-разрядный счётчик. 5 младших

разрядов выполняют функцию предварительного

делителя входной частоты на

![]() .

Значащими в этом режиме являются 5

младших разрядов регистров TLi

и 8 разрядов

THi. Оба Т/С могут работать как таймеры

или счётчики внешних событий в зависимости

от значений разрядов

.

Значащими в этом режиме являются 5

младших разрядов регистров TLi

и 8 разрядов

THi. Оба Т/С могут работать как таймеры

или счётчики внешних событий в зависимости

от значений разрядов

![]() в регистре TMOD.

в регистре TMOD.

Имеются следующие возможности останова (запрета) и включения (разрешения) счёта:

Программно: 1) сброс/установка битов TRi в TCON при GATEi = 0 или INTi = 1 запрещает / разрешает счёт;

2) установка/сброс бита GATEi в регистре TMOD при TRi = 1 и INTi = 0 запрещает / разрешает счёт.

Аппаратно: нулевой / единичный сигнал на входе INTi при GATEi = 1 и TRi = 1 запрещает/разрешает счёт.

В обоих случаях (при программном и аппаратном управлении) при останове в T/Ci сохраняется текущее значение, а после включения счёт продолжается с этого значения, если во время останова T/Ci не перезагружался программно.

Использование

T/Ci для измерения длительности единичного

импульса tи.вх

на входе INTi.

Программно устанавливаем TRi

= 1, GATEi = 1, C/Ti = 0. Запрещаем прерывание от

поступления активного логического

нулевого сигнала на входе INTi. Загружаем

в T/Ci начальное значение ![]() .До поступления

импульса на входе INTi присутствует

логический 0 и T/Ci стоит (счёт запрещён).

.До поступления

импульса на входе INTi присутствует

логический 0 и T/Ci стоит (счёт запрещён).

При поступлении единичного импульса счёт разрешён на время, равное длительности этого импульса. После окончания импульса счёт опять аппаратно запрещается и T/Ci останавливается. По разности чисел в таймере после и до счёта и известной частоте переключения T/Ci

![]()

определяем tи.вх.

При переполнении T/Ci (переход содержимого регистра T/C из состояния «все единицы» в состояние «все нули») устанавливаются флаги TFi в регистре TCON.

На выходе первого T/C в момент переполнения вырабатывается короткий импульс, который поступает в блок синхронизации последовательного интерфейса.

4.1.2 Режим 1 Установка битов М0 = 1, М1 = 0 в регистре TMOD настраивает оба таймера на работу в режиме 1. Упрощённая структура T/Ci в этом режиме приведена в [1].

Каждый T/Ci работает как 16-разрядный счётчик. В остальном программирование, работа и применение T/Ci аналогичны режиму 0.

4 .1.3

Режим 2

Установка битов М0 = 0, М1 = 1 в регистре

TMOD определяет работу T/Ci в режиме 2.

Упрощённая структура T/Ci в этом режиме

приведена на рисунке 9.

.1.3

Режим 2

Установка битов М0 = 0, М1 = 1 в регистре

TMOD определяет работу T/Ci в режиме 2.

Упрощённая структура T/Ci в этом режиме

приведена на рисунке 9.

Рисунок 9 – Упрощенная структурная схема таймера/счетчика1 в режиме 2

Каждый T/Ci может работать как автоперезагружаемый 8-разрядный таймер/счётчик. В качестве счётчика используется регистр TLi, а THi содержит программно установленное начальное значение, с которого ведётся счёт. При каждом очередном переполнении TLi устанавливается флаг переполнения TFi и автоматически начальное значение перезагружается из THi в TLi.

На выходе первого T/Ci в этом режиме вырабатывается последовательность прямоугольных импульсов, которая поступает в блок последовательного интерфейса и может использоваться для синхронизации работы последнего.

4.1.4 Режим 3 Установка битов М0 = 1, М1 = 1 определяет режим 3. Упрощённая структура T/C0 в этом режиме дана на рисунке 10.

Рисунок 10 – Упрощенная структурная схема таймера/счетчика0 в режиме 3

Режим 3 имеет ряд особенностей. Если в этом режиме запрограммировать оба таймера, то T/C1 останавливается, а T/C0 работает как 2 независимых 8-разрядных регистра TH0 и TL0.

Устройство на основе регистра TL0 может работать в режиме таймера и в режиме счётчика внешних событий. За ним сохраняются все биты управления T/C0, оно реагирует на воздействие по входам T0 и INT0. При переполнении TL0 устанавливается флаг TF0.

Устройство на основе регистра TH0 может работать только в режиме таймера. Для управления оно использует часть битов, управляющих работой T/C1, который в режиме 3 остановлен. TR1 управляет включением / выключением TH0. При переполнении TH0 устанавливается флаг TF1.

Вторая особенность режима 3 состоит в том, что T/C0 может программироваться в режим 3, а T/C1 – в режим 0, 1или 2. Так как бит TR1 управляет работой TH0, то T/C1 в режимах 0, 1, 2 при GATE1 = 0 всегда включён, а при GATE1 = 1 – выключен. Флаг переполнения TF1 используется TH0, поэтому при переполнении в режимах 0 и 1 T/C1 обнуляется, а в режиме 2 перезагружается, не устанавливая флаг переполнения. Остальные управляющие биты и сигналы T/C1 используются аналогично режимам 0, 1, 2.

T/C1 аппаратно связан с блоком синхронизации последовательного интерфейса. При работе в режимах 0, 1, 2 при переполнении T/C1 всегда вырабатывает тактовый импульс, поступающий в интерфейс. Поэтому режим 3 для T/C0 удобно применять когда:

1. Требуется работа двух 8-разрядных таймеров (TH0, TL0) и формирование тактовых импульсов для

последовательного интерфейса (T/C1 в режиме 2).

2. Требуется работа 8-разрядного таймера (TH0), 8-разрядного счётчика внешних событий (TL0) и формирование синхроимпульсов для последовательного порта (T/C1 в режиме 2).