- •Введение

- •1 Анализ технического задания

- •2.3 Упрощенная структурная схема

- •3.2 Постоянное запоминающее устройство к556рт6

- •4.2 Выбор последовательного интерфейса

- •4.3 Выбор программируемого параллельного интерфейса

- •4.4 Выбор контролера прерываний

- •4.5 Выбор контроллера прямого доступа к памяти

- •4.6 Выбор программируемого таймера

- •4.7 Выбор ацп

- •4.8 Выбор цап

- •4.9 Уточненная структурная схема мпс

- •5 Разработка алгоритма работы микропроцессорной

- •6 Реализация работы мпс

- •Заключение

- •Список использованных источников

4.3 Выбор программируемого параллельного интерфейса

БИС программируемого параллельного интерфейса КР580ВВ55 предназначена для организации ввода/вывода параллельной информации различного формата и позволяет реализовать большинство известных протоколов обмена по параллельным каналам. БИС программируемого параллельного интерфейса (ППИ) может использоваться для сопряжения микропроцессора со стандартным периферийным оборудованием (дисплеем, телетайпом, накопителем).

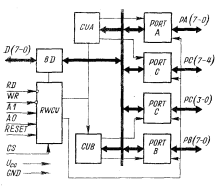

В состав БИС входят: двунаправленный 8-разрядный буфер данных (ВD), связывающий ППИ с системной шиной данных; блок управления записью/чтением (RWCU), обеспечивающий управление внешними и внутренними передачами данных, управляющих слов и информации о состоянии ППИ; три 8-разрядных канала ввода/вывода (РОRТ А, В и С) для обмена информацией с внешними устройствами; схема управления группой А (СUA), вырабатывающая сигналы управления каналом А и старшими разрядами канала С[РС(7-4)]; схема управления группой В (СUВ), вырабатывающая сигналы управления каналом В и младшими разрядами канала С[РС(3-0)]. Структурная схема ППИ приведена на рисунке 24.

Рисунок 24 — Структурная схема ППИ КР580ВВ55

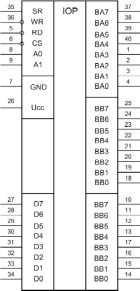

Рисунок 25 – Условное графическое обозначение ППИ КР580ВВ55

Таблица 11 - Описание выводов ППИ КР580ВВ55.

|

№ вывода |

Обозначение |

Наименование |

Назначение |

Тип сигнала |

Состояние |

|

|

Англ. |

Рус. |

|||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

27; 28; 29; 30; 31; 32; 33; 34 |

D(7 – 0) |

Д0 - Д7 |

Шина данных |

Вход/выход данных |

вх/вых |

1,0,в.с. |

|

5 |

RD |

СТБ |

Чтение |

L-уровень сигнала разрешает считывание информации с регистра, адресуемого по входам А0, А1 на шину D(7 – 0) |

вход |

0 |

|

6 |

CS |

ВК |

Выбор кристалла |

L-уровень сигнала подключает ППИ к системной шине |

вход |

0 |

|

7 |

GND |

ОБЩ |

Сигнал питания |

напряжение питания 0 В |

- |

- |

Продолжение таблицы 11

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

9; 8 |

A0, A1 |

A0, A1 |

Входы адреса |

Входы для адресации внутренних регистров ППИ |

вход |

1 |

|

26 |

UCC |

UИП1 |

Сигнал питания |

напряжение питания +5 В |

- |

- |

|

35 |

RESET |

СБР |

Сброс |

Н-уровень сигнала обнуляет регистр управляющего сигнала и устанавливает все порты в режим ввода |

вход |

1 |

|

36 |

WR |

ЗП |

Запись |

L-уровень сигнала разрешает запись информации с шины D(7 – 0) в регистр ППИ, адресуемый по входам А0, А1 |

вход |

0 |

|

37; 38; 39; 40; 1; 2; 3; 4 |

PA(7 – 0) |

ПА(7-0) |

Канал А |

Вход/выход канала А |

вх/вых |

1 |

|

15; 24; 23; 22; 21; 20; 19; 18 |

PB(7 – 0) |

ПB(7 – 0) |

Канал В |

Вход/выход канала В |

вх/вых |

1 |

|

10; 11; 12; 13; 17; 16; 15; 14 |

PC(7 – 0) |

ПC(7 – 0) |

Канал С |

Вход/выход канала С |

вх/вых |

1 |

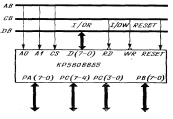

Назначения входных, выходных и управляющих сигналов ППИ приведены при описании выводов микросхемы в таблице 11. Сопряжение БИС КР580ВВ55 со стандартной системной шиной показано на рисунке 11. Сигналы управления работой ППИ подаются на блок RWCU и вместе с адресными входами А0, А1 задают вид операции, выполняемой БИС.

Рисунок 26 - Схема подключения ППИ КР580ВВ55