- •Архитектура и режимы работы микропроцессора к1810вм86

- •Выбор основных узлов для построения мпс

- •3.1 Буферные регистры и шинные формирователи

- •3.2 Программируемый таймер к1810ви54

- •3.3 Разработка блока ацп

- •3.4 Разработка контроллера прямого доступа к памяти

- •3.5 Организация прерываний в мп к1810вм86

- •3.6 Разработка подсистемы ввода/вывода

- •3.7 Генератор тактовых импульсов

- •3.8 Разработка принципиальной схемы микро-эвм

- •5. Буферные регистры и шинные формирователи

-

Выбор основных узлов для построения мпс

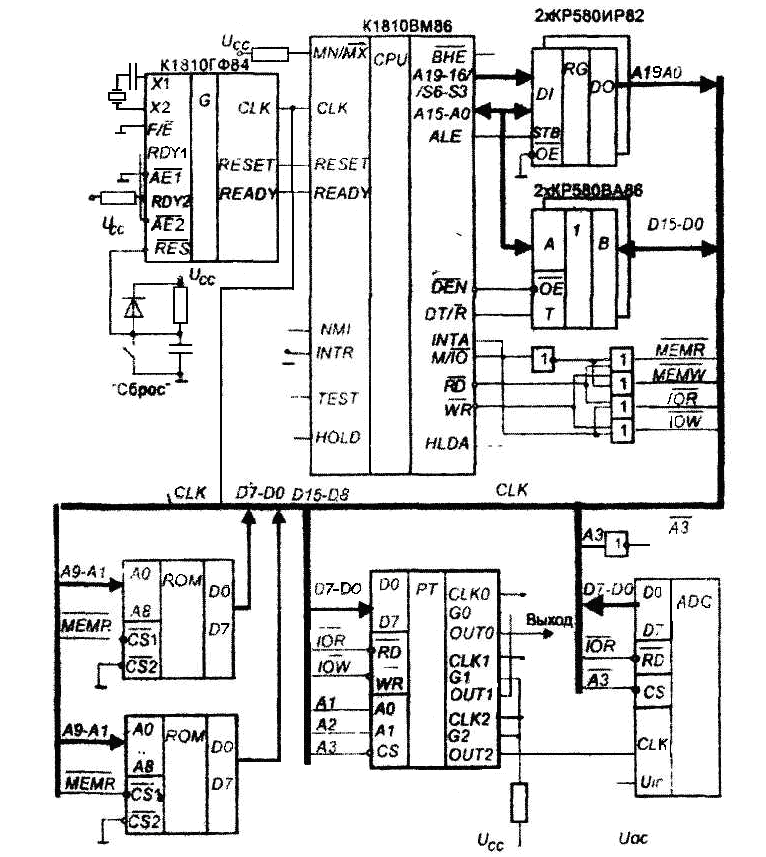

Структурная схема МПС управления показана на рисунке 9.

Рисунок 9 – Структурная схема МПС управления

Сигнал обратной связи поступает на АЦП, который преобразует его в двоичный код. Этот код по системной шине поступает в ЦП, где по программе, записанной в ПЗУ, обрабатывается по закону пропорционального регулятора. Результатом вычисления является коэффициент заполнения импульсов который загружается в регистр таймера ПТ как константа. На выходе таймера образуются логические уровни импульсов управления ШИМ.

Функциональная схема МПС управления

показана на рисунке 10. При разработке

функциональной схемы модуля центрального

процессора возникает потреб ность

в демультиплексировании шины адреса/данных,

буферизации шин адреса (АВ) и шин данных

(BD), а также в формировании

системных управляющих сигналов

памяти и внешних устройств.

Демультиплексирование осуществляется

с помощью двух БИС К580ИР82, которые

выполняют функции защелки адреса и

буфера шины АВ, ; буферизация шин данных

создается с помощью двунаправленных

шинных формирователей К580ВА86, усиливающих

сигналы шины данных; формирование

управляющих сигналов осуществляется

с помощью комбинационных логических

элементов. На выходе этих элементов

формируются сигналы MEMR,

MEMW, JOR, IOW.

ность

в демультиплексировании шины адреса/данных,

буферизации шин адреса (АВ) и шин данных

(BD), а также в формировании

системных управляющих сигналов

памяти и внешних устройств.

Демультиплексирование осуществляется

с помощью двух БИС К580ИР82, которые

выполняют функции защелки адреса и

буфера шины АВ, ; буферизация шин данных

создается с помощью двунаправленных

шинных формирователей К580ВА86, усиливающих

сигналы шины данных; формирование

управляющих сигналов осуществляется

с помощью комбинационных логических

элементов. На выходе этих элементов

формируются сигналы MEMR,

MEMW, JOR, IOW.

Поскольку в разрабатываемой МПС не нужны режимы ПДП, прерываний и обмена по сигналу готовности, схема не содержит входов запросов прерываний, готовности, запроса ПДП и разрешения шин BUSEN. Поэтому на входы БИС генератора, ЦП, регистров-защелок и буферных регистров поданы постоянные логические уровни нуля или единицы. Отсутствуют также схемы оконечных каскадов, формирующих управляющие сигналы (в этой схеме нет потребности переводить управляющие сигнал в третье состояние).

Модуль ПЗУ выполнен на базе двух БИС К541РЕ1 емкостью 512х8 бит каждая. Память организована в виде двух банков памяти - младшего и старшего. Младший банк подключается к младшей половине шины данных D7-D0 и содержит только ячейки памяти с четными адресами; старший банк - к старшей половине шины данных D15-D8 и содержит только ячейки памяти с нечетными адресами. Считывание из ПЗУ происходит при выполнении цикла чтения памяти. При этом формируется сигнал МЕШ=О, который и переводит выходы И 1С ПЗУ в активное состояние. Из ПЗУ всегда считывается слово. Для данного примера начальный адрес ПЗУ определим при нулевых значениях А9-А1, АО, а конечный - при единичных.

Таким образом, начальный адрес ПЗУ –

00000Н, конечный адрес ПЗУ -003 FFH.

Функциональная схема содержит также

АЦП К572ПВ1, что представляет собой

12-разрядный преобразователь напряжения

в двоичный код сравнительно низкого

быстродействия. Поскольку ЛЦП имеет

внутренний регистр со входом управления

третьим состоянием, внешний порт ввода

не нужен. Выход АЦП соединен с линиями

D11-D0. С точки

зрения процес сора.

АЦП представляет собой 16-разрядный

порт. Адрес 16-разрядного порта должен

быть четным. Как видно из рисунка 10,

АЦП выбирается при A3 = 1. Таким образом,

адрес АЦП может быть любым при A3 = 1,

АО = 0. Например, выберем адрес АЦП, равный

08Н.

сора.

АЦП представляет собой 16-разрядный

порт. Адрес 16-разрядного порта должен

быть четным. Как видно из рисунка 10,

АЦП выбирается при A3 = 1. Таким образом,

адрес АЦП может быть любым при A3 = 1,

АО = 0. Например, выберем адрес АЦП, равный

08Н.

Рисунок 10 - Функциональная схема МПС

Программируемый

таймер К1810ВИ54 в данной схеме предназначен

для генерации импульсов управления

широтно-импульсным стабилизатором.

Таймер содержит три независимых канала,

каждый из которых может быть запрограммирован

на работу в одном из шести режимов для

двоичного и двоично-десятичного счета.

Программируемый

таймер К1810ВИ54 в данной схеме предназначен

для генерации импульсов управления

широтно-импульсным стабилизатором.

Таймер содержит три независимых канала,

каждый из которых может быть запрограммирован

на работу в одном из шести режимов для

двоичного и двоично-десятичного счета.

В дальнейшем выбираем основные узлы для построения МПС, буферные регистры и шинные формирователи, программируемый таймер, АЦП и дополняем схему контроллером прямого доступа к памяти, системой прерываний, генератором тактовых импульсов, подсистемой ввода/вывода.