- •1 Расшифровка и анализ задания

- •1.1 Общая структура разрабатываемой микроЭвм

- •1.2 Реакция системы на внешние события

- •2.1 Архитектура однокристальной микроЭвм к1816ве51

- •2.2 Функциональное описание ве51

- •3 Разработка подсистемы памяти

- •3.1 Описание микросхемы кр537ру8

- •3.2 Описание микросхемы кр556рт6

- •3.3 Подключение озу и пзу к системной шине

- •4.1 Аналогово-цифровой преобразователь к111зпв1

- •4.2 Цифроаналоговый преобразователь к572па1

- •4.3 Контроллер прямого доступа к памяти кр580вт57

- •4.4 Многорежимный буферный регистр к589ир12

- •4.5 Контроллер клавиатуры/дисплея кр580вв79

- •4.6 Уточненная схема управляющей микроЭвм

- •5 Разработка программного обеспечения

- •5.1 Алгоритм управления объектом

- •5.2 Разработка блок-схемы управляющей системы

- •6 Реализация устройства на базе омэвм к1816ве51

- •6.1 Основные технические данные и характеристики.

4.3 Контроллер прямого доступа к памяти кр580вт57

БИС программируемого КПДП КР580ВТ57 предназначена для организации высокоскоростного обмена данными между памятью системы и периферийными устройствами путем генерации массива последовательных адресов памяти по требованию периферийного устройства.

МС КР580ВТ57 - четырехканальный программируемый КПДП, осуществляет двунаправленный обмен данными между памятью и периферийными устройствами путем формирования в адресном канале микропроцессорной системы параметров заданного массива адресов ячеек памяти и управляющих сигналов. Массив адресов, по которым происходит обмен данными между периферией и памятью, характеризуется начальным адресом, и числом циклов обращений к памяти. После предоставления системной шины со стороны процессора МС может осуществить обмен массивом данных между памятью и периферийными устройствами без дальнейшего вмешательства процессора.

Каждый из четырех каналов МС КР580ВТ57 обеспечивает адресацию (путем инкрементирования выработанного адреса) внешней памяти массивы объемом до 16К байт с возможностью задания любого до 64К начальных адресов.

Основные электрические параметры МС КР580ВТ57 при температуре окружающей среды + 25 + 10°С.

Выходное напряжение логического нуля UOL, В < 0,45.

Выходное напряжение логической единицы UOH, В > 2,4.

Ток потребления IСС, мА < 100.

Ток утечки на входах IIL, мкА < 1,5.

Ток утечки на управляемых выводах IОL, мкА -1,5,...,1,5.

Упрощенная структурная схема КПДП приведена на рисунке 14.

В состав БИС входят: двунаправленный двустабильный буфер данных (ВD), предназначенный для обмена информацией между МП и КПДП; схема управления чтением/записью (RWCU), адресующая внутренние регистры КПДП и управляющая обменом по шине D(7-0); блок управления (СU), содержащий регистры режима и состояния КПДП и обеспечивающий последовательность операций, необходимую для организации режима прямого доступа к памяти; блок управления приоритетами (РСU), обеспечивающий определенный порядок обслуживания запросов внешних устройств; четыре канала прямого доступа (СН0 - СН3), каждый из которых содержит регистр адреса ячейки памяти, с которой производится обмен, и счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена.

Рисунок 14 - Структурная схема контроллера прямого доступа к памяти КР580ВТ57

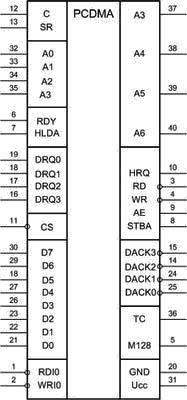

Назначение входных, выходных и управляющих сигналов КПДП (рисунок 15) приведено при описании выводов МС в таблице 5.

Рисунок 15 - Цоколевка КР580ВТ57

Таблица 5 - Описание выводов контроллера прямого доступа к памяти КР580ВТ57

|

Номера контактов |

Обозначение |

Назначение |

Тип сигнала |

Состояние |

|

1 |

2 |

3 |

4 |

|

|

21; 22; 23; 26; 27; 28; 29; 30 |

D(7-0) |

Входы/выходы данных для обмена с МП |

вх/вых |

0, 1, z |

|

12 |

CLK |

Вход тактовых импульсов |

вх |

|

|

13 |

RESET |

Вход установки 0 |

вх |

|

|

35; 34; 33; 32 |

A(3-0) |

Двунаправленные тристабильные адресные выводы |

вых |

0, 1, z |

|

1 |

RD10 |

Чтение ввода/вывода - двунаправленный тристабильный вход/выход; входной сигнал L-уровня разрешает чтение информации из КПДП в МП; выходной сигнал L-уровня разрешает чтение из ВУ |

вх/вых |

0 |

|

2 |

WR10 |

Запись ввода/вывода - двунаправленный тристабильный вход/выход; входной сигнал L-уровня разрешает программирование КПДП: выходной сигнал L-уровня разрешает запись в ВУ |

вх/вых |

0 |

|

6 |

RDY |

Готовность - входной сигнал Н-уровня указывает на готовность к обмену |

вх |

1 |

|

10 |

HRQ |

Запрос захвата - выходной сигнал Н-уровня указывает на запрос о доступе КПДП к системным шинам |

вых |

1 |

|

11 |

CS |

Выбор микросхемы |

|

0 |

|

40; 39; 38; 37 |

A(7-4) |

Тристабильные адресные выходы |

вых |

0, 1, z |

|

7 |

HLDA |

Подтверждение захвата - входной сигнал Н-уровня указывает на возможность доступа к системным шинам |

вх |

1 |

|

3 |

RD |

Чтение из памяти - тристабильный выход; выходной сигнал L-уровня разрешает чтение из ячейки памяти, адресуемой КПДП |

вых |

0 |

|

4 |

WR |

Запись в память - тристабильный выход; выходной сигнал L-уровня разрешает запись в ячейку, адресуемую КПДП |

вых |

0 |

|

9 |

AE |

Разрешение адреса - сигнал Н-уровня используется для блокировки некоторых шин адреса и данных |

вх |

1 |

|

8 |

STBA |

Строб адреса - сигнал Н-уровня указывает на нахождение на шине D (7-0) старшего байта адреса ЗУ |

вх |

1 |

|

36 |

TC |

Конец счета - сигнал Н-уровня определяет выполнение последнего цикла передачи блока данных |

вх |

1 |

|

31 |

UСС |

Напряжение питания ( + 5 В) |

|

|

|

20 |

GND |

Напряжение питания (0 В) |

|

|

|

Продолжение таблицы 5 |

||||

|

1 |

2 |

3 |

4 |

5 |

|

5 |

M128 |

Маркер - сигнал Н-уровня указывает, что до конца передаваемого блока необходимо выполнить число циклов обмена, кратное 128 |

вх |

1 |

|

16;17;18; 19 |

DRQ3-DRQ0 |

Запросы прямого доступа к памяти каналов СН3-СН0; сигнал Н-уровня указывает на запрос от ВУ |

вых |

1 |

|

15; 14; 24; 25 |

DACK3-DACK0 |

Подтверждение запросов прямого доступа к памяти каналов СН3-СН0; сигнал L-уровня указывает на разрешение обмена |

вх |

0 |

Схема подключения КПДП к системной шине с использованием буферного регистра К589ИР12 показана на рисунке 16.

Рисунок 16 - Схема подключения КПДП к системной шине с использованием буферного регистра К589ИР12