- •1 Расшифровка и анализ задания

- •1.1 Общая структура разрабатываемой микроЭвм

- •1.2 Реакция системы на внешние события

- •2.1 Архитектура однокристальной микроЭвм к1816ве51

- •2.2 Функциональное описание ве51

- •3 Разработка подсистемы памяти

- •3.1 Описание микросхемы кр537ру8

- •3.2 Описание микросхемы кр556рт6

- •3.3 Подключение озу и пзу к системной шине

- •4.1 Аналогово-цифровой преобразователь к111зпв1

- •4.2 Цифроаналоговый преобразователь к572па1

- •4.3 Контроллер прямого доступа к памяти кр580вт57

- •4.4 Многорежимный буферный регистр к589ир12

- •4.5 Контроллер клавиатуры/дисплея кр580вв79

- •4.6 Уточненная схема управляющей микроЭвм

- •5 Разработка программного обеспечения

- •5.1 Алгоритм управления объектом

- •5.2 Разработка блок-схемы управляющей системы

- •6 Реализация устройства на базе омэвм к1816ве51

- •6.1 Основные технические данные и характеристики.

2.1 Архитектура однокристальной микроЭвм к1816ве51

2.1.1 Организация архитектуры К1816ВЕ51. Микросхема К1816ВЕ51 представляет собой СБИС семейства высокопроизводительных однокристальных микроЭВМ соответственно со встроенной постоянной памятью программ. Она предназначена для использования в системах обработки информации в качестве высокопроизводительных контроллеров и управляющих устройств в изделиях самого широкого применения.

Система команд ОМЭВМ содержит 111 базовых команд с форматом 1, 2, 3 байта. В составе микросхема МК51 имеет:

- 8-ми битовый канал данных с возможностью обработки следующих форматов данных: бит, байт, два байта;

- внутренюю память данных емкостью 128 байт;

- внутренюю память емкостью 8 Кбайт;

- 32 РОН;

- четыре способа адресации данных (прямая побайтовая и побайтная, косвенная, непосредственная, регистровая);

- пять векторов прерывания;

- 2 уровня прерывания;

- четыре 8-ми разрядных программируемых канала ввода/вывода;

- последовательный канал ввода/вывода;

- 128 определяемых пользователем программно управляемых флага;

- два 16-битовых многорежимных таймеров (счетчиков);

- стек с полной глубиной для связи подпрограмм возврата и памяти данных;

- двоичную и десятичную арифметику.

Базовая организация предоставляет встроенные средства расширения своих ресурсов, которые предусматривают либо реализацию вне кристалла всей памяти программ, либо расширение памяти, имеющейся внутри кристалла до 64 Кб. Имеется возможность подключения дополнительной внешней памяти данных в 64 Кб. Дальнейшее расширение ресурсов может быть выполнено только с помощью внешних средств.

Микроконтроллер конструктивно выполнен в корпусе, имеющем 40 выводов, как изображено на рисунке 1. Назначение выводов микросхемы приведено в таблице 1.

Рисунок 1 - Расположение и обозначение выводов КМ1816ВЕ51

Таблица 1- Назначение выводов микросхемы КМ1816ВЕ51

|

Номера контактов |

Обозначение англ. – рус. |

Назначение |

Тип сигнала |

Состояние |

|

1 |

2 |

3 |

4 |

5 |

|

1-8 |

1-8 Р1.0 - Р1.7 |

Входы-выходы порта Р1 |

вх/вых |

1, 0, z |

|

9 |

RST/VРD – СБР/АП |

Cброс/питание холостого хода |

вх |

1 |

|

10 |

RхD - ВХПР |

Вход приемника |

вх |

1 |

|

11 |

ТхD - ВЫХПЕР |

Выход передатчика |

вых |

1 |

|

12 |

INT0 – ЗПР 0 |

Запрос прерывания 0 |

вх |

0 |

|

13 |

INT1 - ЗПР 1 |

Запрос прерывания 1 |

вх |

0 |

|

14 |

Т0 |

Вход таймера/счетчика 0 |

вх |

1 |

|

15 |

Т1 |

Вход таймера/счетчика 1 |

вх |

1 |

|

16 |

WR - ЗП |

Сигнал записи во внешнее ОЗУ |

вых |

0 |

|

17 |

RD - ЧТ |

Сигнал чтения внешнего ОЗУ |

вых |

0 |

|

Продолжение таблицы 1 |

||||

|

1 |

2 |

3 |

4 |

5 |

|

18-19 |

Х1, Х2 |

Подключение внешнего резонатора |

1-вх, 2-вых |

1 |

|

20 |

VSS – ОБЩ |

"Земля" (Общий вывод И.П.) |

|

|

|

21-28 |

P2.0 - P2.7 |

Входы-выходы порта P2 |

вх/вых |

1, 0, z |

|

29 |

PSEN - РВПП |

Активация внешней памяти программ |

вых |

0 |

|

30 |

ALE/PROG – САВП/ПРОГ |

Строб фиксации адреса внешней памяти |

вых |

1/0 |

|

31 |

ЕA/ VPP – ОРПП/ДП |

Активация внутренней памяти программ / программирование внутренней памяти программ |

вх |

0/1 |

|

32-39 |

Р0.7 - Р0.0 |

Входы-выходы порта Р0 |

вх/вых |

1, 0, z |

|

40 |

VCC - ОСН |

Питание + 5В |

|

|

В архитектуре МК51 и ее модификациях использован стандартный для МК принцип независимости сред для хранения программ и данных. Структурная схема МК51 представлена в приложении А1.

Контроллер состоит из следующих функциональных узлов: - АЛУ (арифметико-логическое устройство); - резидентных памяти программ (РПП) и памяти данных (РПД); - регистров специальных функций (РСФ); - портов параллельного и последовательного ввода-вывода; - таймеров; - системы прерывания.

Архитектура МК51 включает пять типов пространств, четыре из которых являются областями данных:

RSEG Пространство регистров;

DSEG Пространство внутренней памяти данных;

BSEG Битовое пространство данных;

XSEG Пространство внешней памяти;

CSEG Пространство программного кода.

Однако пространство регистров, за исключением PC, и пространство битов, частично пересекаясь, физически совмещаются с пространством DSEG, образуя единую внутреннюю среду для хранения данных, имеющую достаточно сложную структуру. Это стандартный для однокристальных МС прием, позволяющий одни и те же физические данные рассматривать с разных позиций. В результате выбирается наиболее удобный для конкретного случая способ интерпретации тех или иных данных, в соответствии с которым и организуется доступ к ним.

АЛУ МК51 реализует достаточно мощную систему команд, включащую

команды умножения, деления, вычитания, выполнения операций над битами, команды управления. Большинство команд имеют формат один или два байта и выполняются за один или два машинных цикла длительностью 1 мкс (при тактовой частоте 12 МГц). Память программ и память данных физически и логически разделены. Кроме того, к адресному пространству РПД примыкает адресная область регистров специальных функций, включающая в себя: аккумулятор (АСС), слово состояния программы (PSW), указатель стека (SP), указатель данных (DPTR), порты (Р0 - Р3), регистр приоритетов (IP), регистр маски прерываний (IE), регистр режимов таймеров-счетчиков (TMOD), таймеры-счетчики (Т0, Т1), регистр управления и буфер приемопередатчика (SCON и SBUF) и др. Для побайтового ввода-вывода информации в МК51 могут быть использованы четыре порта (Р0 - Р3). Помимо того, выводы порта Р3 (контакты 10-17) могут быть настроены для реализации альтернативных функций (таблице 1) записью в соответствующие разряды порта логической единицы. В случае применения внешней памяти данных (ВПД) или программ (ВПП) используются выходные буферы портов Р0 и Р2. При этом через порт 0 в режиме мультиплексирования выводится младший байт адреса ВПД или ВПП, а затем осуществляется передача данных. Если разрядность адреса составляет более 8 бит, то через порт Р2 происходит выдача его старших разрядов.

Специальный сброс МК51 осуществляется подачей единицы на вход RST в течение по меньшей мере двух машинных циклов. При этом сбрасывается содержимое счетчика команд и всех регистров специальных функций, в регистр указателя стека записывается число 07Н, а в порты - 0FFH. После снятия сигнала RST запускается программа по адресу 0000H.

2.1.2 Набор регистров МК51. Набор программно-доступных регистров процессора ВЕ51 приведен на рисунке 2. Архитектура относится к классу аккумуляторных с переключаемыми банками рабочих регистров. Поэтому центральным регистром набора считается 8-разрядный аккумулятор А, выполняющий обычные функции основного арифметического регистра.

Рисунок 2 - Набор регистров МК51

В МК ВЕ51 предусмотрено четыре банка по восемь рабочих регистров

R0 - R7 в каждом, переключаемых полем RS слова состояния программы. Регистры выполняют общецелевые функции промежуточного хранения данных. По аналогии с ВЕ48 два регистра R0 и R1 каждого банка реализуют также функции 8-разрядных указателей данных.

Использование наборов рабочих регистров позволяет существенно уменьшить длительность переключения контекстов ЦП, что очень важно для МС реального времени. Следует также отметить, что в ВЕ51 отсутствует ряд ограничений, накладываемых на обработку подпрограмм и процедур обслуживания прерываний.

При сбросе МК все регистры устанавливаются в исходное состояние. Программный счетчик PC принимает значение 0000Н, аккумулятор А - 00Н; В - 00Н, PSW - 00Н, SP - 07H и DPTR - 0000Н. Сброс PC обеспечивает передачу управления по стартовому адресу 0000Н, а установка SP в состояние 07Н поддерживает совместимость со стеком ВЕ48. Сброс PSW реализует выбор нулевого регистрового банка RB0.

Регистр В служит расширением аккумулятора А, необходимым для осуществления операций умножения и деления, причем он является как источником, так и приемником операндов. Во всех других операциях регистр В выполняет функции, определяемые пользователем.

Регистр слова состояния программы кроме флажков, входящих в PSW МК51:

PSW.7 CY Перенос из старшего разряда АЛУ;

PSW.6 АС Дополнительный перенос из младшей тетрады АЛУ;

PSW.5 F0 Флажок пользователя общего назначения включает также флажки;

PSW.2 OV Признак арифметического переполнения результата PSW.1;

Р Признак четности.

Сюда же входит двухразрядное поле RS (Registers Select) выбора одного из четырех возможных банков рабочих регистров. Флажки признаков результата CY, АС и OV, как правило, отражают состояние последней арифметической операции, флажок Р - четность содержимого А. Флажок переноса CY является аккумулятором булевого процессора. Функциональное назначение флажка F0 определяется пользователем в конкретной ситуации.

2.1.3 Организация памяти МК51. Пространство внутренней памяти DSEG имеет общий объем 256 байт. Однако организация МК51 предусматривает реализацию только первой его половины (128 байт). Все банки рабочих регистров, а также системный стек в МК ВЕ51 располагаются во внутренней памяти данных и могут рассматриваться как обычные ячейки памяти. Существуют два способа адресации памяти данных МК: прямой и косвенный через регистры R0, R1 выбранного в данный момент одного из банков RB0 - RB3. При прямой адресации доступна только младшая половина адресного пространства внутренней памяти данных (128 байт), при косвенной обеспечивается доступ к любой ее ячейке (256 байт). Введение прямой адресации значительно расширило возможности обработки данных МК, в частности появились средства прямого доступа в соседние регистровые банки и стек системы, интерпретируемые как обычные ячейки памяти. Карты адресов отдельных бит представлены на рисунке 3.

Микроконтроллер BE51 имеет мощную и развитую подсистему ввода-вывода (ВВ) и средства поддержки режима реального времени. Для их управления в МК предусмотрен ряд регистров, которые размещаются во второй половине прямо адресуемого пространства, образующей пространство специальных регистров (128 байт). Сюда же включены порты и основные регистры ЦП.

а) б)

а) – карта адресуемых бит в резидентной памяти данных; б) – карта адресуемых бит в блоке регистров специальных функций

Рисунок 3 - Карты адресов отдельных бит МК BE51

Центральный процессор МК51 содержит специальную логику, предназначенную для выполнения нескольких однобитовых операций, булев или одноразрядный процессор для вычисления булевых выражений. В основу булева процессора положен стандартный аккумуляторный принцип организации. В данном случае роль аккумулятора выполняет флажок переноса CY.

Для хранения булевых данных в архитектуре ВЕ51 предусмотрено специальное одноразрядное линейно упорядоченное пространство BSEG объемом 256 байт, которое физически совмещено с байтовым пространством данных DSEG. При этом одна часть пространства BSEG попадает на обычные ячейки памяти DSEG и может рассматриваться как область общего назначения. Обычно она используется для хранения булевых переменных. Другая часть пространства BSEG попадает на ячейки памяти, совмещенные с регистрами МК, что обеспечивает независимый доступ к их отдельным разрядам. В булевом пространстве определена только прямая адресация bit.

В МК ВЕ51 имеется возможность совмещения внешней части CSEG с пространством XSEG. Такое совмещение поможет распространить на область CSEG операции и способы доступа к XSEG, в частности станет осуществимой операция записи, что может быть использовано при загрузке программ из внешней памяти.

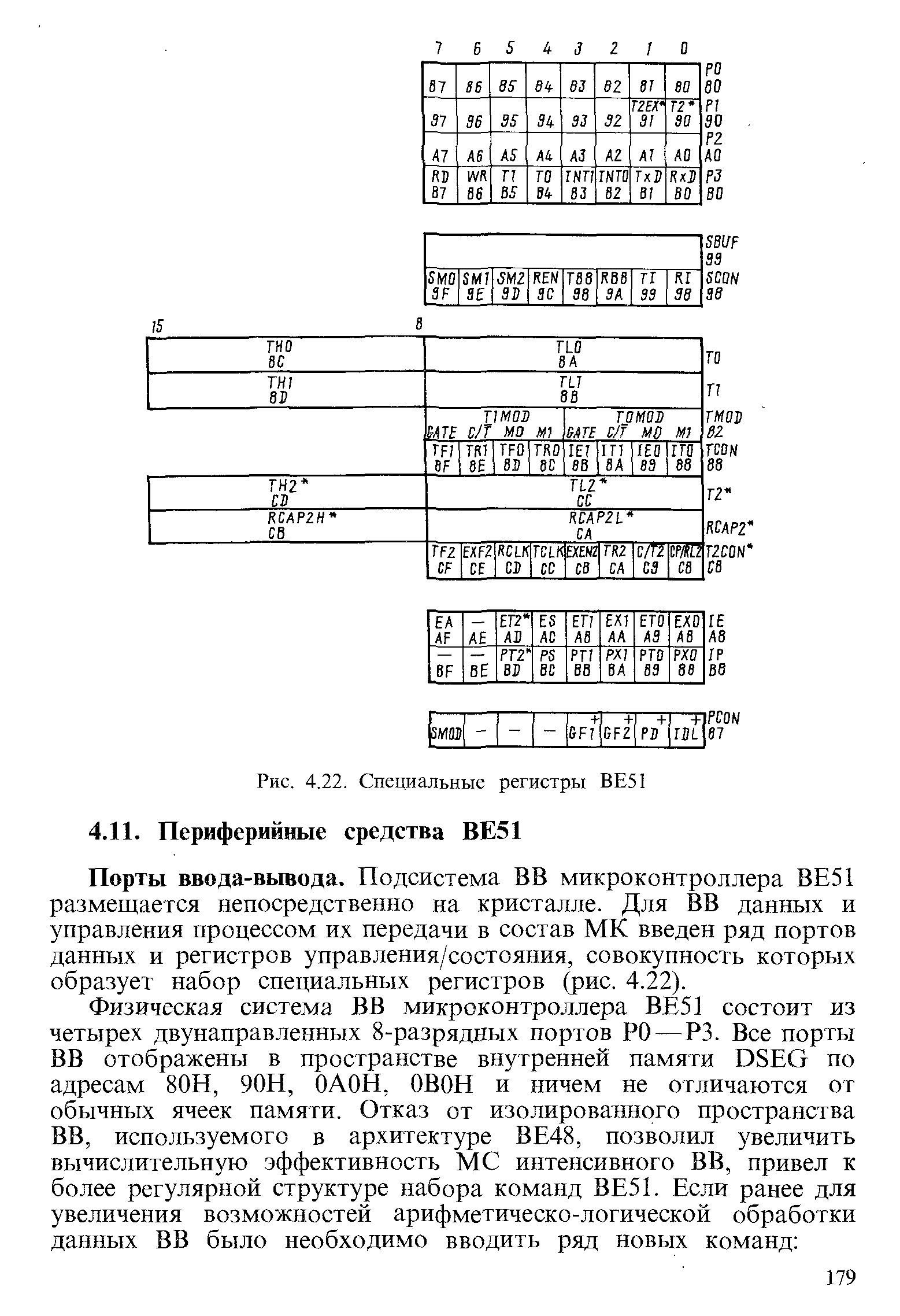

2.1.4 Порты ввода-вывода. Подсистема ввода-вывода (ВВ) МК ВЕ51 размещается непосредственно на кристалле. Для ВВ данных и управления процессом их передачи в состав МК введен ряд портов данных и регистров управления/состояния, совокупность которых образует набор специальных регистров (рисунок 4).

Рисунок 4 - Специальные регистры МК BE51

Физическая система ВВ микроконтроллера ВЕ51 состоит из четырех двунаправленных 8-разрядных портов Р0 - РЗ. Все порты ВВ отображены в пространстве внутренней памяти DSEG по адресам 80Н, 90Н, ОАОН, ОВОН и ничем не отличаются от обычных ячеек памяти.

Каждый из портов содержит фиксатор и буфер. Фиксатор представляет собой 8-ми разрядный регистр, имеющий байтовую и битовую адресацию для установки (сброса) разрядов с помощью программного обеспечения. Физические адреса фиксаторов Р0, Р1, Р2, Р3 составляют для:

Р0 - 80Н, при битовой адресации 80Н-87Н;

P1 - 90H, при битовой адресации 90Н-97Н;

P2 - A0H, при битовой адресации А0Н-А7Н;

P3 - B0H, при битовой адресации В0Н-В7Н.

Порты Р1, Р2, Р3 в установившемся состоянии имеют внутреннее сопротивление, обеспечивающее ток нагрузки в диапазоне от 800 мкА до 80 мА при входном напряжении от 0,45 В до 2,4 В.

При переключении входной информации на порт с низкого уровня на

высокий на время, равное одному состоянию (2 периода), подключается форсирующий транзистор, уменьшающий внутреннее сопротивление буфера, в результате чего уменьшается длительность фронта и задержка выходного сигнала.

Порт Р0 отличается от остальных отсутствием внутреннего сопротивления.

Расширение пространства ВВ может быть выполнено за счет области XSEG или другими средствами с помощью самих портов Р0 - РЗ и SBUF.

2.1.5 Последовательный канал связи. В состав ВЕ51 входит дуплексный канал последовательной связи с буферизацией, который может быть запрограммирован для работы в одном из четырех режимов:

режим 0 - синхронный последовательный ВВ со скоростью OSC/12;

режим 1- асинхронный с 10-битовым кадром и переменной скоростью передачи;

режим 2 - асинхронный с 11-битовым кадром и фиксированной скоростью передачи OSC/32 или OSC/64;

режим 3 - асинхронный с 11-битовым кадром и переменной скоростью передачи.

Входные и выходные данные хранятся в буферном регистре SBUF с адресом 99Н. Управление работой приемопередатчиков осуществляется через слово управления и состояния SCON, расположенное в регистре по адресу 98Н.

2.1.6 Таймеры/счетчики. Предназначены для подсчета внешних событий, для получения программно управляемых временных задержек, выполнения времязадающих функций ОМЭВМ.

В состав блока входят:

- два 16-ти разрядных регистра Т/С 0, Т/С 1;

- 8-ми разрядный регистр режимов Т/С (ТМ0D);

- 8-ми разрядный регистр управления (ТСОN);

- схема инкремента;

- схема фиксации INT0, INT1, Т0, Т1;

- схема управления флагами;

- логика управления Т/С.

Два 16-разрядных регистра Т/С 0 и Т/С 1 выполняют функцию хранения содержимого счета. Каждый из них состоит из пары 8-ми разрядных регистров, соответственно ТH0, ТL0 и ТH1, ТL1. Причем регистры ТН0, ТH1 - старшие, регистры ТL0, ТL1 - младшие 8 разрядов. Каждый из 8-ми разрядных регистров может быть использован, как РОН, если Т/С не используются (бит TR0 для Т/С 0 и бит TR1 для Т/С 1 в регистре управления TCON равен "0").

Регистр режимов Т/С (TMOD) предназначен для приема и хранения кода, определяющего:

- один из 4-х возможных режимов работы каждого Т/С;

- работу в качестве таймеров или счетчиков;

- управление Т/С от внешнего вывода.

2.1.7 Система прерываний. Упрощенная схема прерываний МК51 приведена на рисунке 5.

Рисунок 5 - Упрощенная схема реализации прерываний МК ВЕ51

Внешние прерывания INT0 и INT1 могут быть вызваны либо низким логическим уровнем, либо переходом из 1 в 0 на входах МК51 в зависимости от значений IT0 и IT1 - управляющих бит, представленных в регистре TCON (timer control register - регистр управления таймерами) разрядами TCON.0 и TCON.2. При появлении запросов от внешних источников прерываний устанавливаются флаги IE0 и IE1 в разрядах TCON.1 и TCON.3. При переполнении таймеров устанавливаются флаги запроса прерываний от таймеров TF0 и TF1 (TCON.5 и TCON.7), которые сбрасываются автоматически при передаче управления программе обслуживания прерываний. Флаги запросов на прерывания от приемника и передатчика RI и TI устанавливаются универсальным приемопередатчиком и должны сбрасываться программно.

Два регистра специальных функций IE и IP позволяют управлять режимами прерываний и уровнями приоритета. Каждому запросу соответствует адрес вектора прерывания в поле адресов памяти программ (рисунок 5). По адресу вектора прерывания должна быть записана команда безусловного перехода (JMP) к подпрограмме обслуживания прерывания. Возврат в основную программу осуществляется по команде RETI.

2.1.8 Система команд МК ВЕ51. Система насчитывает 111 команд, из них 49 однобайтовых, 45 двухбайтовых и 17 трехбайтовых. Все команды выполняются за один или два машинных цикла (12 тактов ALE) за исключением команд MUL и DIV, которые требуют четыре цикла. Большинство двухбайтовых команд одноцикловые, а все трехбайтовые команды - двухцикловые.

Все множество команд ВЕ51 удобно разбить на пять групп: пересылки, логической обработки, арифметической обработки, передачи управления, булевого процессора.

Группа команд пересылки содержит команды MOV (пересылки данных между DSEG и RSEG), MOVC (между CSEG и A), MOVX (между XSEG и А или RSEG), команды обращения к стеку PUSH и POP, а также две команды обмена ХСН и XCHD. Наиболее емкой инструкцией является команда MOV, которая использует четыре способа адресации: регистровый (A, Rn, DPTR), прямой (direct), косвенный (@Ri) и непосредственный (#data, #data 16). Для указания приемника служат три способа адресации (кроме непосредственного), для указания источника все четыре.

Группа команд логических операций содержит три типовые двухместные операции: ANL - логическое И, ORL - логическое ИЛИ и XRL - логическое исключающее ИЛИ. Источником первого операнда и одновременно приемником результата служит либо аккумулятор А, либо прямо адресуемая ячейка памяти. Второй операнд задается одним из четырех основных методов адресации. В состав группы входит также ряд одноместных операций: CLR - очистки, CPL - логического дополнения (инверсия), а также RL, RLC, RR и RRC - операции циклического и расширенного сдвигов вправо и влево. Все операции манипулируют содержимым только аккумулятора А. Сюда же включена операция обмена тетрад в аккумуляторе SWAP, которая может интерпретироваться как циклический сдвиг байта на четыре разряда.

В состав группы команд арифметической обработки входят: операция сложения ADD, сложения с учетом переноса ADDC, вычитания с учетом займа SUBB, увеличения и уменьшения на единицу INC и DEC, десятичная коррекция сложения в 2/10-коде упакованного формата DA, умножение MUL и деление DIU. Операции выполняются над беззнаковыми целыми числами.

В операциях сложения и вычитания первым операндом и приемником результата служит аккумулятор. В качестве второго операнда выступает либо рабочий регистр Rn, п = 0 - 7, выбранного регистрового банка, либо ячейка памяти данных, адресуемая прямо direct или косвенно @Ri, i = 0 - 1, либо непосредственные данные #data. Операции INC и DEC применимы к аккумулятору, одному из рабочих регистров или к ячейке памяти, адресуемой как прямо, так и косвенно.

В составе группы команд передачи управления находятся команды перехода AJMP, LJMP, SJMP, JMP, условного перехода JZ, JNZ, CJNE, вызова ACALL, LCALL, возврата RET, RETI и модификации с условным переходом DJNZ. Сюда же включена пустая команда NOP.

К типовым условным операциям ВЕ51 относятся также операции JZ и JNZ, JC и JNC. Две последние включены в группу булевых. Появилась новая операция «Сравнить и перейти» CJNE. По данной команде операнд сначала сравнивается по правилам вычитания целых чисел с константой и в соответствии с результатом сравнения выставляется флажок CY. Затем в случае несовпадения с константой выполняется ветвление.